POWER5

POWER5 POWER5 MCM | |

| 일반 정보 | |

|---|---|

| 시작됨 | 2004 |

| 설계자 | IBM |

| 퍼포먼스 | |

| 최대 CPU 클럭 속도 | 1.5GHz ~ 2.3GHz |

| 캐시 | |

| L1 캐시 | 32+32KB/코어 |

| L2 캐시 | 1.875MB/칩 |

| L3 캐시 | 36MB/칩(오프칩) |

| 건축과 분류 | |

| 기술 노드 | 130nm ~ 90nm |

| 명령 집합 | 파워PC 2.02 |

| 물리적 사양 | |

| 코어스 |

|

| 역사 | |

| 전임자 | POWER4 |

| 후계자 | POWER6 |

| POWER, PowerPC 및 Power ISA 아키텍처 |

|---|

| NXP(이전의 Freescale 및 Motorola) |

| IBM |

|

| IBM/닌텐도 |

| 기타 |

| 관련 링크 |

| 회색으로 취소됨, 이탤릭체로 기록됨 |

POWER5는 IBM이 개발하고 조립한 마이크로프로세서다.POWER4의 개량형이다.주요 개선사항은 동시 멀티스레딩(SMT)과 온디 메모리 컨트롤러 지원이다.POWER5는 듀얼 코어 마이크로프로세서로, 각 코어가 총 2개의 물리적 스레드 및 4개의 논리적 스레드를 각각 지원한다.

역사

마이크로프로세서의 기술적 세부 사항은 2003년 핫 칩스 회의에서 처음 제시되었다.좀 더 완전한 설명은 2003년 10월 14일 마이크로프로세서 포럼 2003에서 제공되었다.POWER5는 공개 판매되지 않았으며 IBM과 그 파트너들에 의해 독점적으로 사용되었다.마이크로프로세서를 사용하는 시스템은 2004년에 도입되었다.POWER5는 주로 Intel Itanium 2에 대항하여 고급 기업용 서버 시장에서 경쟁했으며, 그 중에서도 Sun Microsystems UltraSPARC IV와 Fujitsu SPARC64 V가 경쟁하였다.2005년에 개선된 반복인 POWER5+로 대체되었다.

설명

POWER5는 POWER4의 추가 개발이다.양방향 다중 스레딩을 추가하기 위해서는 각 스레드가 고유한 스레드를 가질 수 있도록 리턴 스택, 프로그램 카운터, 명령 버퍼, 그룹 완료 단위 및 스토어 대기열을 복제해야 한다.각 스레드는 자체 레지스터 집합을 보지만 레지스터 파일 및 실행 단위와 같은 대부분의 리소스는 공유된다.POWER5는 두 개의 스레드가 동시에 실행되는 동시 멀티스레딩(SMT)을 구현한다.POWER5는 현재 워크로드에 맞게 최적화하기 위해 시만텍을 실행 중지할 수 있다.

레지스터 파일 등 많은 자원을 두 개의 스레드로 공유하기 때문에 성능 손실을 보상하기 위해 용량이 늘어나는 경우가 많다.POWER4의 정수 레지스터와 부동 소수점 레지스터 수는 80개, 부동 소수점 레지스터 72개에서 각각 120개로 늘어난다.부동 소수점 명령 캐쉬도 20개에서 24개 항목으로 용량이 늘어난다.L2 통합 캐시의 용량은 1.875MB로, 설정 연관성은 10-way로 증가하였다.통합 L3 캐시는 별도의 칩에 외부로 배치되는 대신 포장되어 제공되었다.용량은 36MB로 늘렸다. POWER4처럼 캐시는 두 코어가 공유한다.캐시는 코어 주파수의 절반으로 운영되는 두 대의 단방향 128비트 버스를 통해 액세스된다.

온 다이 메모리 컨트롤러는 최대 64GB의 DDR 및 DDR2 메모리를 지원한다.고주파 직렬 버스를 사용하여 듀얼 인라인 메모리 모듈(DIMM)을 마이크로프로세서에 연결하는 외부 버퍼와 통신한다.

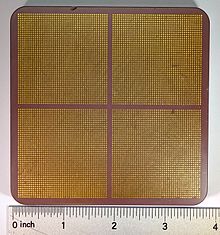

POWER5는 2억 7천 6백만 개의 트랜지스터를 포함하고 있으며 면적은 389mm이다2.IBM은 8개 층의 구리 인터커넥트로 절연체(SOI)에 0.13μm 실리콘을 보완한 금속-산화-반도체(CMOS) 공정으로 제작했다.POWER5 다이에는 듀얼 칩 모듈(DCM) 또는 멀티 칩 모듈(MCM)이 패키징되어 있다.DCM에는 POWER5 다이 1개와 관련 L3 캐시 다이 1개가 포함되어 있다.MCM에는 POWER5 다이 4개와 L3 캐시 다이 4개가 들어 있으며, 각 POWER5 다이당 1개씩 들어 있으며, 95mm x 95mm이다.[1][2]

하이엔드 시스템의 여러 POWER5 프로세서를 함께 결합하여 ViVA(Virtual Vector Architecture)라는 기술에 의해 단일 벡터 프로세서의 역할을 할 수 있다.

POWER5+

POWER5+는 2005년 10월 4일에 도입된 POWER5의 개선된 반복이다.개선사항은 초기에는 새로운 공정으로 인해 전력 소비량이 낮았다.POWER5+ 칩은 90nm의 제작 공정을 사용한다.이로 인해 다이 크기가 389mm에서2 243mm로2 감소하였다.

클럭 주파수는 출시 당시 증가하지 않았고 1.5~1.9GHz로 유지됐다.2006년 2월 14일, 새로운 버전은 클럭 주파수를 2.2GHz로, 그리고 2006년 7월 25일에 2.3GHz로 높였다.

POWER5+는 이전의 POWER5 마이크로프로세서와 동일한 패키지로 포장되었지만, 또한 POWER5+ 다이당 하나씩 2개의 POWER5+ 다이와 2개의 L3 캐시 다이를 포함하는 쿼드칩 모듈(QCM)에서도 사용할 수 있었다.이 QCM 칩은 1.5~1.8GHz의 클럭 주파수로 작동했다.

상품들

IBM은 System p와 System i 서버 제품군, DS8000 스토리지 서버 및 하이엔드 Infoprint 프린터의 내장형 마이크로프로세서로 DCM과 MCM POWER5 마이크로프로세서를 사용한다.DCM POWER5 마이크로프로세서는 IBM의 하이엔드 IntelliStation POWER 285 워크스테이션에서 사용된다.POWER5 마이크로프로세서의 타사 사용자는 자사의 에스컬라 서버에 있는 Groofe Bull과 최대 128개의 POWER5+ 마이크로프로세서가 있는 SR11000 컴퓨터에 있으며, 이 컴퓨터에는 2007년 TOP500 슈퍼컴퓨터 목록에 여러 개의 설치가 포함되어 있다.IBM은 System p5 510Q, 520Q, 550Q 및 560Q 서버에 POWER5+ QCM을 사용한다.[3]

메모들

- ^ 글라스카우스키, "IBM Rises Curtain on Power5"

- ^ Krewell, "Power5 Tops On Bandwidth".

- ^ POWER5+ 기술을 기반으로 하는 IBM System p5 Quad-Core 모듈:기술 개요 및 소개

참고 항목

참조

- "IBM Previews Power5"(2003년 9월 8일).마이크로프로세서 보고서.

- 클라베스, 요아힘 외(2004)."POWER5 마이크로프로세서의 설계 및 구현".2004 IEEE 국제 솔리드 스테이트 회로 회의의 진행.

- 글라스카우스키, 피터 N. (2003년 10월 14일)"IBM Rises Curtain on Power5"마이크로프로세서 보고서.

- 갈라와 론과 신하로이와 발람과텐들러, 조엘 M. (2004)"IBM Power5 칩: 듀얼 코어 멀티스레드 프로세서"IEEE 마이크로.

- Krewell, Kevin(2003년 12월 22일)."Power5 Tops On Bandwidth".마이크로프로세서 보고서.

- 신하로이, 발라람 외(2005)."POWER5 시스템 마이크로아키텍처".IBM Journal of Research and Development.

- 밴스, 애슐리(2005년 10월 4일)"IBM은 Power5+가 가득 찬 Unix 라인을 펌프질한다."레지스터.

외부 링크

- POWER5와 Montecito의 비교 및 분석인 슈퍼 헤비급 사이징은 POWER4와 POWER5 사이의 주요 변경 사항과 성능 추정치를 설명한다.

- 고성능 IBM Power5+ p5-575 클러스터 1600 및 DDN S2A9550 스토리지, 텍사스 A&M 대학교