시리얼 존재 검출

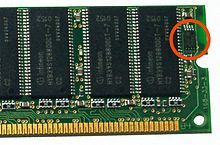

Serial presence detect컴퓨팅에서 시리얼 존재 검출(SPD)은 메모리 모듈에 대한 정보에 자동으로 액세스하는 표준화된 방법입니다.이전의 72핀 SIMM에는 5비트의 PPD(Parallel Presence Detect) 데이터를 제공하는5개의 핀이 포함되어 있었지만, 168핀 DIMM 규격은 시리얼 존재 검출로 변경되어 보다 많은 [1]정보를 부호화했습니다.

일반적인 최신 컴퓨터의 전원을 켜면 전원 투입 시 자가진단(POST)을 실행하는 것으로 시작됩니다.1990년대 중반 이후 이 프로세스에는 현재 존재하는 하드웨어가 자동으로 구성됩니다.SPD는 어떤 메모리가 있는지, 어떤 메모리 타이밍을 사용하여 메모리에 액세스할 수 있도록 하는 메모리 하드웨어 기능입니다.

일부 컴퓨터는 하드웨어 변경에 완전히 자동으로 적응합니다.대부분의 경우 BIOS 파라미터에 액세스하여 설정을 표시하고 변경할 수 있는 특별한 절차가 있습니다.컴퓨터의 메모리 SPD 데이터 사용 방법을 제어할 수 있습니다(설정 선택, 메모리 타이밍 선택 변경, SPD 데이터 완전 덮어쓰기 등).

저장된 정보

SPD를 지원하는 메모리모듈의 경우 JEDEC 표준에서는 특정 파라미터가 메모리모듈에 있는EEPROM의 하위128바이트에 있어야 합니다.이러한 바이트에는 타이밍 파라미터, 제조원, 시리얼 번호 및 모듈에 관한 기타 유용한 정보가 포함됩니다.메모리를 이용하는 디바이스는 이 정보를 읽어 모듈의 주요 파라미터를 자동으로 판단합니다.예를 들어 SDRAM 모듈의 SPD 데이터는 CAS 지연에 대한 정보를 제공하므로 사용자의 개입 없이 시스템이 이를 올바르게 설정할 수 있습니다.

SPD EEPROM 펌웨어에는 I²C 프로토콜의 변형인 SMBus를 사용하여 액세스합니다.그러면 모듈의 통신 핀 수가 클럭 신호와 데이터 신호 두 개로 줄어듭니다.EEPROM은 RAM과 접지 핀을 공유하며 자체 전원 핀이 있으며 슬롯을 식별하기 위한 추가 핀(SA0~2)이 3개 있습니다.이 핀은 EEPROM에 0x50~0x57 범위의 고유 주소를 할당하기 위해 사용됩니다.8개의 메모리 모듈 간에 통신회선을 공유할 수 있을 뿐만 아니라 전원장치 전압, CPU 온도, 팬 속도 등의 시스템 헬스모니터링 태스크에도 같은 SMBus가 일반적으로 사용됩니다.

SPD EEPROM은 쓰기 보호가 되어 있지 않은 경우 I²C 주소 0x30~0x37에도 응답합니다.확장(TSE 시리즈)에서는 주소 0x18~0x1F 를 사용하여 옵션의 온칩 온도 센서에 액세스합니다.이러한 모든 값은 SA0-2를 사용하는 Device Type Identifier Code Prefix(DTIC; 디바이스 유형 식별자 코드 프리픽스)에 의해 형성되는7비트 I²C 주소입니다.슬롯 3에서 (1100)을 읽으려면110 0011 = 0x33최종 R/W 비트와 함께 8비트 디바이스 선택 [2]코드를 형성합니다.slot-id의 의미는 쓰기 보호 조작에 따라 다르므로 SA 핀에 의해 [3]전혀 전달되지 않습니다.

SPD 이전에는 메모리 칩에 PPD(Parallel Presence Detect)가 탑재되어 있었습니다.PPD는 정보 비트마다 별도의 핀을 사용했습니다.즉, 핀을 저장할 수 있는 공간이 한정되어 있기 때문에 메모리 모듈의 속도와 밀도만 저장할 수 있었습니다.

SDRAM

최초의 SPD 사양은 JEDEC에 의해 발행되어 PC100 메모리 [4]사양의 일부로서 인텔에 의해 강화되었습니다.지정된 대부분의 값은 이진 코드화된 10진수 형식입니다.가장 유의한 니블에는 10에서 15 사이의 값이 포함될 수 있으며 경우에 따라 더 높게 확장될 수 있습니다.이 경우 대신 1, 2, 3의 부호화가 16, 17 및 18의 부호화에 사용됩니다.최상위 니블인 0은 "정의되지 않음"을 나타내기 위해 예약되어 있습니다.

SPD ROM은 바이트 18의 세트비트로 지정된3개의 CAS 지연에 대해 최대 3개의 DRAM 타이밍을 정의합니다.먼저 CAS 지연이 가장 높고(가장 빠른 클럭), 다음으로 클럭 속도가 점차 낮은2개의 CAS 지연이 발생합니다.

| 바이트 | 조금 | 메모들 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (12월) | ( ) 。 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | 존재하는 바이트 수 | 통상 128 | |||||||

| 1 | 0x01 | log2(SPD EEPROM 크기) | 통상 8(256바이트) | |||||||

| 2 | 0x02 | 기본 메모리 타입(4:SPD SDRAM) | ||||||||

| 3 | 0x03 | 뱅크 2 행 주소 비트(0 ~15) | 뱅크 1 행 주소 비트(1 ~15) | 뱅크 1과 같은 경우 뱅크 2는 0입니다. | ||||||

| 4 | 0x04 | 뱅크 2 컬럼주소 비트(0 ~15) | 뱅크 1 컬럼주소 비트(1 ~15) | 뱅크 1과 같은 경우 뱅크 2는 0입니다. | ||||||

| 5 | 0x05 | 모듈상의 RAM 뱅크 수(1 ~255) | 일반적으로 1 또는 2 | |||||||

| 6 | 0x06 | 모듈 데이터 폭 낮음 바이트 | 일반적으로 ECC DIMM의 경우 64 또는 72 | |||||||

| 7 | 0x07 | 모듈 데이터 폭 하이 바이트 | 0(폭 256비트 이하일 경우 제외) | |||||||

| 8 | 0x08 | 이 어셈블리의 인터페이스 전압 레벨(V 공급 전압과cc 동일하지 않음)(0~4) | 테이블 검색에 의해 디코딩됨 | |||||||

| 9 | 0x09 | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | CAS 지연이 가장 클럭사이클 시간 | ||||||

| 10 | 0x0a | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | 클럭으로부터의 SDRAM 액세스 시간(tAC) | ||||||

| 11 | 0x0b | DIMM 구성 유형(0 ~2) : ECC 이외, 패리티, ECC | 테이블 룩업 | |||||||

| 12 | 0x0c | 자신 | 갱신기간(0~5): 64, 256, 128, 32, 16, 8kHz | 갱신 요건 | ||||||

| 13 | 0x0d | 뱅크 2 2× | 뱅크 1의 프라이머리 SDRAM 폭(1~127, 통상은 8) | 뱅크 1 데이터 SDRAM 디바이스의 폭.뱅크 2는 같은 폭, 비트7이 설정되어 있는 경우는 2×폭으로 할 수 있다. | ||||||

| 14 | 0x0e | 뱅크 2 2× | 뱅크 1 ECC SDRAM 폭(0~127) | 뱅크 1 ECC/패리티 SDRAM 디바이스의 폭.뱅크 2는 같은 폭, 비트7이 설정되어 있는 경우는 2×폭으로 할 수 있다. | ||||||

| 15 | 0x0f | 랜덤 열 읽기의 클럭 지연 | 통상은 1 | |||||||

| 16 | 0x10 | 페이지입니다. | — | — | — | 8 | 4 | 2 | 1 | 지원되는 버스트 길이(비트맵) |

| 17 | 0x11 | SDRAM 디바이스별 뱅크(1 ~255) | 보통 2 또는 4 | |||||||

| 18 | 0x12 | — | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 지원되는 CAS 지연(비트맵) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 지원되는 CS 지연 시간(비트맵) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 지원되는 WE 지연 시간(비트맵)맵) |

| 21 | 0x15 | — | 용장성 | 다른 클럭 | 등록된 데이터 | 버퍼링된 데이터 | 온카드 PLL | 등록된 주소 | 버퍼 주소 | 메모리 모듈 기능 비트맵 |

| 22 | 0x16 | — | — | 상한cc V(전압) 공차 | 낮은cc V(전압) 공차 | 쓰기/1 읽기 버스트 | 모두 프리차지 | 자동 프리차지 | 조기 RAS 프리차지 | 메모리 칩 기능 지원 비트맵 |

| 23 | 0x17 | 나노초(4~18) | 10분의 1 나노초(0~9: 0.0~0.9) | 중간 CAS 지연에서의 클럭사이클 시간 | ||||||

| 24 | 0x18 | 나노초(4~18) | 10분의 1 나노초(0~9: 0.0~0.9) | 클럭으로부터의 데이터 액세스 시간(tAC) | ||||||

| 25 | 0x19 | 나노초 (1 ~63) | 0.25ns(0~3: 0.00~0.75) | 짧은 CAS 지연에서의 클럭사이클 시간 | ||||||

| 26 | 0x1a | 나노초 (1 ~63) | 0.25ns(0~3: 0.00~0.75) | 클럭으로부터의 데이터 액세스 시간(tAC) | ||||||

| 27 | 0x1b | 나노초 (1 ~255) | 최소 행 프리차지 시간(tRP) | |||||||

| 28 | 0x1c | 나노초 (1 ~255) | 최소 행 액티브-행 액티브 지연(tRRD) | |||||||

| 29 | 0x1d | 나노초 (1 ~255) | RAS에서 CAS로의 최소 지연(tRCD) | |||||||

| 30 | 0x1e | 나노초 (1 ~255) | 프리차지 최소 활성 시간(tRAS) | |||||||

| 31 | 0x1f | 512 MiB | 256 MiB | 128 MiB | 64 MiB | 32 MiB | 16 MiB | 8 MiB | 4 MiB | 모듈 뱅크 밀도(비트맵).크기가 다른 뱅크일 경우 2비트가 설정됩니다. |

| 32 | 0x20 | 서명(1: -) | 나노초(0~7) | 10분의 1 나노초(0~9: 0.0~0.9) | 클럭으로부터의 주소/명령어 셋업 시간 | |||||

| 33 | 0x21 | 서명(1: -) | 나노초(0~7) | 10분의 1 나노초(0~9: 0.0~0.9) | 클럭 이후의 주소/명령 홀드 시간 | |||||

| 34 | 0x22 | 서명(1: -) | 나노초(0~7) | 10분의 1 나노초(0~9: 0.0~0.9) | 클럭으로부터의 데이터 입력 셋업 시간 | |||||

| 35 | 0x23 | 서명(1: -) | 나노초(0~7) | 10분의 1 나노초(0~9: 0.0~0.9) | 클럭 이후의 데이터 입력 홀드 타임 | |||||

| 36–61 | 0x24~0x3d | 예약필 | 향후 표준화를 위해 | |||||||

| 62 | 0x3e | 메이저 리비전(0~9) | 마이너 리비전(0~9) | SPD 리비전 레벨(예: 1.2) | ||||||

| 63 | 0x3f | 체크섬 | 0 ~ 62 바이트의 합계(그 후 부정되지 않음) | |||||||

| 64–71 | 0x40~47 | 제조원 JEDEC ID | 스토어드 리틀 엔디안, 트래킹 제로 패드 | |||||||

| 72 | 0x48 | 모듈 제조장소 | 벤더 고유 코드 | |||||||

| 73–90 | 0x49~0x5a | 모듈 부품 번호 | ASCII, 스페이스 패딩 | |||||||

| 91–92 | 0x5b~0x5c | 모듈 리비전 코드 | 벤더 고유 코드 | |||||||

| 93 | 0x5d | 수십 년 (0~9: 0~90) | 년 (0 ~ 9) | 제조일(YYWW) | ||||||

| 94 | 0x5e | 수십 주 (0~5: 0~50) | 주 (0 ~ 9) | |||||||

| 95–98 | 0x5f~0x62 | 모듈 시리얼 번호 | 벤더 고유 코드 | |||||||

| 99–125 | 0x63~0x7f | 제조원 고유의 데이터 | 퍼포먼스 프로파일 향상 가능 | |||||||

| 126 | 0x7e | 66MHz의 경우 0x66 [sic], 100MHz의 경우 0x64 | 인텔 주파수 지원 | |||||||

| 127 | 0x7f | CLK0 | CLK1 | CLK3 | CLK3 | 90/100 °C | CL3 | CL2 | 동시 액세스 포인트 | 인텔 기능 비트맵 |

DDR SDRAM

DDR DIMM SPD 포맷은 SDRAM 포맷의 확장판입니다.대부분의 경우 파라미터 범위는 고속에 맞게 조정됩니다.

| 바이트 | 조금 | 메모들 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (12월) | ( ) 。 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | 쓴 바이트 수 | 통상 128 | |||||||

| 1 | 0x01 | log2(SPD EEPROM 크기) | 통상 8(256바이트) | |||||||

| 2 | 0x02 | 기본 메모리 타입 (7 = DDR SDRAM) | ||||||||

| 3 | 0x03 | 뱅크 2 행 주소 비트(0 ~15) | 뱅크 1 행 주소 비트(1 ~15) | 뱅크 2는 뱅크 1과 같은 경우 0입니다. | ||||||

| 4 | 0x04 | 뱅크 2 컬럼주소 비트(0 ~15) | 뱅크 1 컬럼주소 비트(1 ~15) | 뱅크 2는 뱅크 1과 같은 경우 0입니다. | ||||||

| 5 | 0x05 | 모듈상의 RAM 뱅크 수(1 ~255) | 일반적으로 1 또는 2 | |||||||

| 6 | 0x06 | 모듈 데이터 폭 낮음 바이트 | 일반적으로 ECC DIMM의 경우 64 또는 72 | |||||||

| 7 | 0x07 | 모듈 데이터 폭 하이 바이트 | 0(폭 256비트 이하일 경우 제외) | |||||||

| 8 | 0x08 | 이 어셈블리의 인터페이스 전압 레벨(V 공급 전압과cc 동일하지 않음)(0-5) | 테이블 검색에 의해 디코딩됨 | |||||||

| 9 | 0x09 | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | CAS 지연이 가장 높을 때의 클럭사이클 시간 | ||||||

| 10 | 0x0a | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 SDRAM 액세스 시간(tAC) | ||||||

| 11 | 0x0b | DIMM 구성 유형(0 ~2) : ECC 이외, 패리티, ECC | 테이블 룩업 | |||||||

| 12 | 0x0c | 자신 | 갱신기간(0~5): 64, 256, 128, 32, 16, 8kHz | 갱신 요건 | ||||||

| 13 | 0x0d | 뱅크 2 2× | 뱅크 1 프라이머리 SDRAM 폭(1~127) | 뱅크 1 데이터 SDRAM 디바이스의 폭.뱅크 2는 같은 폭, 비트7이 설정되어 있는 경우는 2×폭으로 할 수 있다. | ||||||

| 14 | 0x0e | 뱅크 2 2× | 뱅크 1 ECC SDRAM 폭(0~127) | 뱅크 1 ECC/패리티 SDRAM 디바이스의 폭.뱅크 2는 같은 폭, 비트7이 설정되어 있는 경우는 2×폭으로 할 수 있다. | ||||||

| 15 | 0x0f | 랜덤 열 읽기의 클럭 지연 | 통상은 1 | |||||||

| 16 | 0x10 | 페이지입니다. | — | — | — | 8 | 4 | 2 | 1 | 지원되는 버스트 길이(비트맵) |

| 17 | 0x11 | SDRAM 디바이스별 뱅크(1 ~255) | 통상은 4 | |||||||

| 18 | 0x12 | — | 4 | 3.5 | 3 | 2.5 | 2 | 1.5 | 1 | 지원되는 CAS 지연(비트맵) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 지원되는 CS 지연 시간(비트맵) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 지원되는 WE 지연 시간(비트맵)맵) |

| 21 | 0x15 | — | x | 차이 클럭 | FET 스위치 외부 활성화 | FET 스위치 온보드 활성화 | 온카드 PLL | 등록한 | 버퍼링 완료 | 메모리 모듈 기능 비트맵 |

| 22 | 0x16 | 고속 AP | 동시 자동 프리차지 | 상한cc V(전압) 공차 | 낮은cc V(전압) 공차 | — | — | — | 약한 드라이버 포함 | 메모리 칩 기능 비트맵 |

| 23 | 0x17 | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | 중간 CAS 지연에서의 클럭사이클 시간 | ||||||

| 24 | 0x18 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 데이터 액세스 시간(tAC) | ||||||

| 25 | 0x19 | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | 짧은 CAS 지연에서의 클럭사이클 시간 | ||||||

| 26 | 0x1a | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 데이터 액세스 시간(tAC) | ||||||

| 27 | 0x1b | 나노초 (1 ~63) | 0.25ns(0~0.75) | 최소 행 프리차지 시간(tRP) | ||||||

| 28 | 0x1c | 나노초 (1 ~63) | 0.25ns(0~0.75) | 최소 행 액티브-행 액티브 지연(tRRD) | ||||||

| 29 | 0x1d | 나노초 (1 ~63) | 0.25ns(0~0.75) | RAS에서 CAS로의 최소 지연(tRCD) | ||||||

| 30 | 0x1e | 나노초 (1 ~255) | 프리차지 최소 활성 시간(tRAS) | |||||||

| 31 | 0x1f | 512 MiB | 256 MiB | 128 MiB | 64 MiB | 32 MiB | 16 MiB/ 4 GiB | 8 MiB/ 2 GiB | 4 MiB/ 1 GiB | 모듈 뱅크 밀도(비트맵).크기가 다른 뱅크일 경우 2비트가 설정됩니다. |

| 32 | 0x20 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 주소/명령어 셋업 시간 | ||||||

| 33 | 0x21 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭 이후의 주소/명령 홀드 시간 | ||||||

| 34 | 0x22 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 데이터 입력 셋업 시간 | ||||||

| 35 | 0x23 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭 이후의 데이터 입력 홀드 타임 | ||||||

| 36–40 | 0x24~0x28 | 예약필 | 슈퍼셋 정보 | |||||||

| 41 | 0x29 | 나노초 (1 ~255) | 최소 활성에서 활성/새로 고침 시간(tRC) | |||||||

| 42 | 0x2a | 나노초 (1 ~255) | 활성/새로고침 시간으로의 최소 새로 고침(tRFC) | |||||||

| 43 | 0x2b | 나노초(1~63 또는 255: 최대값 없음) | 0.25ns(0~0.75) | 최대 클럭 사이클 시간(최대CK) | ||||||

| 44 | 0x2c | 100분의 1 나노초 (0.01 ~2.55) | 최대 스큐, 임의의 DQ에 대한 DQS(최대DQSQ) | |||||||

| 45 | 0x2d | 10분의 1 나노초(0.0~1.2) | 100분의 1 나노초(0.00~0.09) | 읽기 데이터 홀드 스큐 계수(tQHS) | ||||||

| 46 | 0x2e | 예약필 | 향후 표준화를 위해 | |||||||

| 47 | 0x2f | — | 높이 | DIMM 모듈 높이, 테이블 검색 | ||||||

| 48–61 | 0x30~0x3d | 예약필 | 향후 표준화를 위해 | |||||||

| 62 | 0x3e | 메이저 리비전(0~9) | 마이너 리비전(0~9) | SPD 리비전레벨, 0.0 또는 1.0 | ||||||

| 63 | 0x3f | 체크섬 | 0 ~ 62 바이트의 합계(그 후 부정되지 않음) | |||||||

| 64–71 | 0x40~47 | 제조원 JEDEC ID | 스토어드 리틀 엔디안, 트래킹 제로 패드 | |||||||

| 72 | 0x48 | 모듈 제조장소 | 벤더 고유 코드 | |||||||

| 73–90 | 0x49~0x5a | 모듈 부품 번호 | ASCII, 스페이스 패딩 | |||||||

| 91–92 | 0x5b~0x5c | 모듈 리비전 코드 | 벤더 고유 코드 | |||||||

| 93 | 0x5d | 수십 년(0~90년) | 년 (0 ~ 9) | 제조일(YYWW) | ||||||

| 94 | 0x5e | 수십 주 (0 ~ 50) | 주 (0 ~ 9) | |||||||

| 95–98 | 0x5f~0x62 | 모듈 시리얼 번호 | 벤더 고유 코드 | |||||||

| 99–127 | 0x63~0x7f | 제조원 고유의 데이터 | 퍼포먼스 프로파일 향상 가능 | |||||||

DDR2 SDRAM

DDR2 SPD 규격에서는 몇 가지 변경이 이루어지지만 위와 거의 비슷합니다.눈에 띄는 점은 크기가 다른2개의 랭크 DIMM 의 서포트가 혼란스럽고 거의 사용되지 않는다는 점입니다.

BCD로 인코딩된 사이클 시간 필드(바이트 9, 23, 25 및 49)의 경우 일반적인 타이밍을 정확하게 나타내기 위해 10 진수에 대해 몇 가지 추가 인코딩이 정의됩니다.

| 16진수 | 바이너리 | 중요성 |

|---|---|---|

| A | 1010 | 0.25 (¼) |

| B | 1011 | 0.33 (⅓) |

| C | 1100 | 0.66 (⅔) |

| D | 1101 | 0.75 (¾) |

| E | 1110 | 0.875 (,, Nvidia XMP 확장) |

| F | 1111 | 예약필 |

| 바이트 | 조금 | 메모들 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 12월 | 16진수 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | 쓴 바이트 수 | 통상 128 | |||||||

| 1 | 0x01 | log2(SPD EEPROM 크기) | 통상 8(256바이트) | |||||||

| 2 | 0x02 | 기본 메모리 타입(8 = DDR2 SDRAM) | ||||||||

| 3 | 0x03 | 예약필 | 행 주소 비트(1 ~15) | |||||||

| 4 | 0x04 | 예약필 | 열 주소 비트(1 ~15) | |||||||

| 5 | 0x05 | 수직 높이 | 스택? | 콘씨? | 랭크 1 (1 ~8) | 일반적으로 0 또는 1은 1 또는 2를 의미합니다. | ||||

| 6 | 0x06 | 모듈 데이터 폭 | 일반적으로 ECC DIMM의 경우 64 또는 72 | |||||||

| 7 | 0x07 | 예약필 | ||||||||

| 8 | 0x08 | 이 어셈블리의 인터페이스 전압 레벨(V 공급 전압과cc 동일하지 않음)(0-5) | 테이블 룩업에 의해 디코딩됩니다. 일반적으로 5 = SSTL 1.8 V | |||||||

| 9 | 0x09 | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | CAS 지연이 가장 높을 때의 클럭사이클 시간 | ||||||

| 10 | 0x0a | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 SDRAM 액세스 시간(tAC) | ||||||

| 11 | 0x0b | DIMM 구성 유형(0 ~2) : ECC 이외, 패리티, ECC | 테이블 룩업 | |||||||

| 12 | 0x0c | 자신 | 갱신기간(0~5): 64, 256, 128, 32, 16, 8kHz | 갱신 요건 | ||||||

| 13 | 0x0d | 프라이머리 SDRAM 폭(1~255) | 일반적으로 8개(×8개 부품에서 조립된 모듈) 또는 16개 | |||||||

| 14 | 0x0e | ECC SDRAM 폭(0 ~255) | 뱅크 ECC/패리티 SDRAM 디바이스의 폭.보통 0 또는 8 입니다. | |||||||

| 15 | 0x0f | 예약필 | ||||||||

| 16 | 0x10 | — | — | — | — | 8 | 4 | — | — | 지원되는 버스트 길이(비트맵) |

| 17 | 0x11 | SDRAM 디바이스별 뱅크(1 ~255) | 보통 4 또는 8 | |||||||

| 18 | 0x12 | 7 | 6 | 5 | 4 | 3 | 2 | — | — | 지원되는 CAS 지연(비트맵) |

| 19 | 0x13 | 예약필 | ||||||||

| 20 | 0x14 | — | — | 미니 UDIMM | 미니 RDIMM | 마이크로 DIMM | SO-DIMM | UDIMM | RDIMM | 이 어셈블리의 DIMM 타입(비트맵) |

| 21 | 0x15 | — | 모듈이 분석 프로브입니다. | — | FET 스위치 외부 활성화 | — | — | — | — | 메모리 모듈 기능 비트맵 |

| 22 | 0x16 | — | — | — | — | — | — | — | 약한 드라이버 포함 | 메모리 칩 기능 비트맵 |

| 23 | 0x17 | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | 중간 CAS 지연에서의 클럭사이클 시간 | ||||||

| 24 | 0x18 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 데이터 액세스 시간(tAC) | ||||||

| 25 | 0x19 | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | 짧은 CAS 지연에서의 클럭사이클 시간 | ||||||

| 26 | 0x1a | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 데이터 액세스 시간(tAC) | ||||||

| 27 | 0x1b | 나노초 (1 ~63) | 1/4ns(0~0.75) | 최소 행 프리차지 시간(tRP) | ||||||

| 28 | 0x1c | 나노초 (1 ~63) | 1/4ns(0~0.75) | 최소 행 액티브-행 액티브 지연(tRRD) | ||||||

| 29 | 0x1d | 나노초 (1 ~63) | 1/4ns(0~0.75) | RAS에서 CAS로의 최소 지연(tRCD) | ||||||

| 30 | 0x1e | 나노초 (1 ~255) | 프리차지 최소 활성 시간(tRAS) | |||||||

| 31 | 0x1f | 512 MiB | 256 MiB | 128 MiB | 16 GiB | 8 GiB | 4 GiB | 2 GiB | 1 GiB | 각 랭크 사이즈(비트맵). |

| 32 | 0x20 | 10분의 1 나노초(0.0~1.2) | 100분의 1 나노초(0.00~0.09) | 클럭으로부터의 주소/명령어 셋업 시간 | ||||||

| 33 | 0x21 | 10분의 1 나노초(0.0~1.2) | 100분의 1 나노초(0.00~0.09) | 클럭 이후의 주소/명령 홀드 시간 | ||||||

| 34 | 0x22 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 스트로보로부터의 데이터 입력 셋업 시간 | ||||||

| 35 | 0x23 | 10분의 1 나노초 (0.0 ~0.9) | 100분의 1 나노초(0.00~0.09) | 스트로브 후 데이터 입력 홀드 시간 | ||||||

| 36 | 0x24 | 나노초 (1 ~63) | 0.25ns(0~0.75) | 최소 쓰기 복구 시간(tWR) | ||||||

| 37 | 0x25 | 나노초 (1 ~63) | 0.25ns(0~0.75) | 읽기 명령어에 대한 내부 쓰기 지연(tWTR) | ||||||

| 38 | 0x26 | 나노초 (1 ~63) | 0.25ns(0~0.75) | 프리차지 명령 지연에 대한 내부 읽기RTP(t) | ||||||

| 39 | 0x27 | 예약필 | "메모리 분석 프로브 특성"을 위해 예약됨 | |||||||

| 40 | 0x28 | — | tRC 분수 ns(0~5): 0, 0.25, 0.33, 0.5, 0.66, 0.75 | tRFC 분수 ns(0~5): 0, 0.25, 0.33, 0.5, 0.66, 0.75 | tRFC + 256 ns | 바이트 41 및 42의 확장자. | ||||

| 41 | 0x29 | 나노초 (1 ~255) | 최소 활성에서 활성/새로 고침 시간(tRC) | |||||||

| 42 | 0x2a | 나노초 (1 ~255) | 활성/새로고침 시간으로의 최소 새로 고침(tRFC) | |||||||

| 43 | 0x2b | 나노초(0~15) | 10분의 1 나노초 (0.0 ~0.9) | 최대 클럭 사이클 시간(tCK max) | ||||||

| 44 | 0x2c | 100분의 1 나노초 (0.01 ~2.55) | 최대 스큐, 임의의 DQ에 대한 DQS(tDQSQ max) | |||||||

| 45 | 0x2d | 100분의 1 나노초 (0.01 ~2.55) | 읽기 데이터 홀드 스큐 계수(tQHS) | |||||||

| 46 | 0x2e | 마이크로초 (1 ~255) | PLL 재잠금 시간 | |||||||

| 47–61 | 0x2f~0x3d | 예약필 | 향후 표준화를 위해. | |||||||

| 62 | 0x3e | 메이저 리비전(0~9) | 마이너 리비전(0.0~0.9) | SPD 리비전레벨(통상은 1.0) | ||||||

| 63 | 0x3f | 체크섬 | 0 ~ 62 바이트의 합계, 부정되지 않음 | |||||||

| 64–71 | 0x40~47 | 제조원 JEDEC ID | 스토어드 리틀 엔디언, 트레일링 제로 패드 | |||||||

| 72 | 0x48 | 모듈 제조장소 | 벤더 고유 코드 | |||||||

| 73–90 | 0x49~0x5a | 모듈 부품 번호 | ASCII, 스페이스 패딩( , , , , , , A ~ Z, a ~z, 0 ~ 9, 스페이스) | |||||||

| 91–92 | 0x5b~0x5c | 모듈 리비전 코드 | 벤더 고유 코드 | |||||||

| 93 | 0x5d | 2000년 이후 (0 ~255) | 제조일(YYWW) | |||||||

| 94 | 0x5e | 주 (1 ~ 52) | ||||||||

| 95–98 | 0x5f~0x62 | 모듈 시리얼 번호 | 벤더 고유 코드 | |||||||

| 99–127 | 0x63~0x7f | 제조원 고유의 데이터 | 퍼포먼스 프로파일 향상 가능 | |||||||

DDR3 SDRAM

DDR3 SDRAM 규격은 SPD 콘텐츠 레이아웃을 대폭 오버홀하여 심플하게 합니다.BCD로 인코딩된 다수의 나노초 필드 대신 일부 "타임베이스" 단위가 고정밀로 지정되며 다양한 타이밍 파라미터가 해당 [8]기본단위의 배수로서 인코딩됩니다.또한 CAS 지연에 따라 다른 시간 값을 지정하는 관행도 없어졌습니다.이제 타이밍 파라미터는 1세트뿐입니다.

개정 1.1에서는 일부 파라미터를 "중간 타임베이스" 값에 a(서명, -128 +127) "미세 타임베이스" 보정을 더한 값으로 표시할 수 있습니다.일반적으로 중간 타임베이스는 1/8ns(125ps), 미세 타임베이스는 1, 2.5 또는 5ps입니다.보정이 없는 이전 버전과의 호환성을 위해 보통 중간 타임베이스 번호는 반올림되고 보정은 음수입니다.이 방법으로 동작하는 값은 다음과 같습니다.

| MTB 바이트 | FTB 바이트 | 가치 |

|---|---|---|

| 12 | 34 | tminCK, 최소 클럭 주기 |

| 16 | 35 | tminAA, 최소 CAS 지연 시간 |

| 18 | 36 | tminRCD, 최소 RAS#에서 CAS#으로의 지연 |

| 20 | 37 | tminRP, 최소 행 프리차지 지연 |

| 21, 23 | 38 | tminRC, 액티브에서 액티브로의 최소 지연/프리차지연 |

| 바이트 | 조금 | 메모들 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 12월 | 16진수 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | CRC에서 시리얼 제외 | SPD 바이트 합계 (미정의/256) | 사용된 SPD 바이트(미정의/128/176/256) | ||||||

| 1 | 0x01 | SPD 메이저리비전 | SPD 마이너리비전 | 1.0, 1.1, 1.2 또는 1.3 | ||||||

| 2 | 0x02 | 기본 메모리 타입 (11 = DDR3 SDRAM) | RAM 칩의 종류 | |||||||

| 3 | 0x03 | 예약필 | 모듈 타입 | 모듈 유형(예: 2 = Unbuffered DIMM, 3 = SO-DIMM, 11 = LRDIMM) | ||||||

| 4 | 0x04 | — | 뱅크 어드레스 비트-3 | log2(칩당 비트 수)-28 | 0은 8개의 뱅크, 256 Mibit을 의미합니다. | |||||

| 5 | 0x05 | — | 행 주소 비트-12 | 컬럼 주소 비트-9 | ||||||

| 6 | 0x06 | 예약필 | 1.25V | 1.35 V | 1.5V가 아니다 | 모듈 전압 지원. 기본값은 1.5V입니다. | ||||

| 7 | 0x07 | — | 랭크 1 | log2(I/O 비트/칩)-2 | 모듈 구성 | |||||

| 8 | 0x08 | — | ECC 비트(001=8) | log2(데이터 비트)-3 | 64비트 비ECC DIMM의 경우 0x03 | |||||

| 9 | 0x09 | 배당, 피코초 (1 ~15) | 제수, 피코초(1~15) | 파인 타임 베이스, 배당/나눗셈 | ||||||

| 10 | 0x0a | 배당, 나노초 (1 ~255) | 중간 타임 베이스, 배당/나눗셈, 일반적으로 1/8 | |||||||

| 11 | 0x0b | 제수, 나노초 (1 ~255) | ||||||||

| 12 | 0x0c | 최소 사이클 시간 tminCK | MTB의 배수 | |||||||

| 13 | 0x0d | 예약필 | ||||||||

| 14 | 0x0e | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 지원되는 CAS 지연(비트맵) |

| 15 | 0x0f | — | 18 | 17 | 16 | 15 | 14 | 13 | 12 | |

| 16 | 0x10 | 최소 CAS 지연 시간(tminAA) | MTB의 배수(예: 80/8 ns). | |||||||

| 17 | 0x11 | 최소 쓰기 복구 시간(tminWR) | MTB의 배수(예: 120/8 ns). | |||||||

| 18 | 0x12 | RAS에서 CAS로의 최소 지연 시간(tminRCD) | MTB의 배수(예: 100/8 ns). | |||||||

| 19 | 0x13 | 행간 최소 활성 지연 시간(tminRRD) | MTB의 배수(예: 60/8 ns). | |||||||

| 20 | 0x14 | 최소 행 프리차지 시간(tminRP) | MTB의 배수(예: 100/8 ns). | |||||||

| 21 | 0x15 | tminRC, 비트 11:8 | tminRAS, 비트 11:8 | 바이트의 상위 4비트 23 및 22 | ||||||

| 22 | 0x16 | 최소 활성 시간, tminRAS, 비트 7:0 | MTB의 배수(예: 280/8 ns). | |||||||

| 23 | 0x17 | 최소 액티브에서 액티브/갱신, tminRC, 비트 7:0 | MTB의 배수(예: 396/8 ns). | |||||||

| 24 | 0x18 | 최소 리프레시 복구 지연(tmin, 비트RFC 7:0) | MTB의 배수로, 예를 들어 1280/8 ns입니다. | |||||||

| 25 | 0x19 | 최소 리프레시 리커버리 지연, tminRFC, 비트 15:8 | ||||||||

| 26 | 0x1a | 읽기 지연에 대한 최소 내부 쓰기 시간(tminWTR) | MTB의 배수(예: 60/8 ns). | |||||||

| 27 | 0x1b | 프리차지 지연을 위한 최소 내부 읽기(tminRTP) | MTB의 배수(예: 60/8 ns). | |||||||

| 28 | 0x1c | 예약필 | tminFAW, 비트 11:8 | MTB의 배수(예: 240/8 ns). | ||||||

| 29 | 0x1d | 최소 4개의 활성화 창 지연 tminFAW, 비트 7:0 | ||||||||

| 30 | 0x1e | DLL 오프 | — | RZQ/7 | RZQ/6 | SDRAM 옵션 기능 지원 비트맵 | ||||

| 31 | 0x1f | PASR | — | ODTS | ASR | ETR 1× | ETR(95°C) | SDRAM 서멀 및 리프레시 옵션 | ||

| 32 | 0x20 | 현재의. | 정확도(TBD, 현재 0 = 정의되지 않음) | DIMM 온도 센서가 있습니까? | ||||||

| 33 | 0x21 | 표준 없음 | 다이카운트 | — | 신호 부하 | 비표준 SDRAM 디바이스 유형(예: 스택형) | ||||

| 34 | 0x22 | tminCK 보정(1.1의 새로운 기능) | 서명된 여러 FTB, 바이트 12에 추가 | |||||||

| 35 | 0x23 | tminAA 보정(1.1의 새로운 기능) | 서명된 여러 FTB, 바이트 16에 추가 | |||||||

| 36 | 0x24 | tminRCD 보정(1.1의 새로운 기능) | 여러 개의 FTB 서명 완료, 바이트 18에 추가 | |||||||

| 37 | 0x25 | tminRP 보정(1.1의 새로운 기능) | 서명된 여러 FTB, 바이트 20에 추가 | |||||||

| 38 | 0x26 | tminRC 보정(1.1의 새로운 기능) | 여러 개의 FTB 서명 완료, 바이트 23에 추가 | |||||||

| 39–40 | 0x27~0x28 | 예약필 | 향후 표준화를 위해. | |||||||

| 41 | 0x29 | 벤더 고유 | tMAW. | Maximum Activate Count(MAC; 최대 활성화 수) (테스트되지 않은/700k/600k/.../200k/예약된/표준) | 행 해머 경감용 | |||||

| 42–59 | 0x2a~0x3b | 예약필 | 향후 표준화를 위해. | |||||||

| 60 | 0x3c | — | 모듈 높이 (mm) (1~31, > 45) | 모듈 공칭 높이 | ||||||

| 61 | 0x3d | 뒷면 두께, mm(1~16) | 전면 두께, mm(1~16) | 모듈 두께, 값 = ceil(mm) - 1 | ||||||

| 62 | 0x3e | 설계. | 리비전 | JEDEC 설계 번호 | 사용된 JEDEC 참조 설계(1111=없음) | |||||

| 63–116 | 0x3f~0x74 | 모듈 고유의 섹션 | 등록된 것과 버퍼되지 않은 것이 다릅니다. | |||||||

| 117 | 0x75 | 모듈 제조원 ID(lsbyte) | JEP-106에 의해 할당됨 | |||||||

| 118 | 0x76 | 모듈 제조업체 ID(msbyte) | ||||||||

| 119 | 0x77 | 모듈 제조장소 | 벤더 고유 코드 | |||||||

| 120 | 0x78 | 수십 년 | 몇 해 | 제조년도(BCD) | ||||||

| 121 | 0x79 | 수십 주 | 몇 주 | 제조주간(BCD) | ||||||

| 122–125 | 0x7a~0x7d | 모듈 시리얼 번호 | 벤더 고유 코드 | |||||||

| 126–127 | 0x7e~0x7f | SPD CRC-16 | 바이트 0~116 또는 0~125를 포함합니다.바이트 0 비트7 참조 | |||||||

| 128–145 | 0x80–0x91 | 모듈 부품 번호 | ASCII 서브셋, 스페이스 패딩 | |||||||

| 146–147 | 0x92~0x93 | 모듈 리비전 코드 | 벤더 정의 | |||||||

| 148–149 | 0x94~0x95 | DRAM 제조원 ID | 모듈 제조업체와 구별됨 | |||||||

| 150–175 | 0x96~0xAF | 제조원 고유의 데이터 | ||||||||

| 176–255 | 0xB0~0xFF | 고객님이 사용하실 수 있습니다. | ||||||||

모듈의 메모리 용량은 바이트 4, 7, 8에서 계산할 수 있습니다.모듈 폭(바이트 8)을 칩당 비트 수(바이트 7)로 나누면 등급당 칩 수를 알 수 있습니다.그런 다음 칩당 용량(바이트 4)과 모듈의 칩 순위 수(일반적으로 바이트 7부터 1 또는 2)에 곱할 수 있습니다.

DDR4 SDRAM

SPD의 DDR4 SDRAM "Annex L" 규격에 따라 사용되는 EEPROM 모듈이 변경됩니다.이제 JEDEC은 기존의 AT24C02 호환 256바이트 EEPROM 대신 SMBus 수준에서 각각 256바이트의 2페이지로 구성된 새로운 비표준 EE1004 유형을 정의합니다.새로운 메모리에서는 여전히 오래된 0x50~0x57 주소가 사용되지만, 현재는 0x36(SPA0)과 0x37(SPA1)의 2개의 추가 주소를 사용하여 뱅크스위칭의 [11]일종인 버스의 현재 액티브페이지를 선택하기 위한 명령어를 수신하고 있습니다.내부적으로는 각 논리 페이지가 각각 128바이트의 2개의 물리 블록으로 분할되어 합계 4개의 블록과 [12]512바이트가 됩니다."[13]특수" 주소 범위에 대한 다른 의미론은 동일하지만, 쓰기 보호는 블록별로 해결되어 SA0에서 높은 전압이 상태를 변경해야 합니다.

Annex L은 메모리 모듈의 유형에 따라 512바이트(최대 320바이트가 정의됨) 템플릿에 연결할 수 있는 몇 가지 레이아웃을 정의합니다.비트 정의는 DDR3와 [12]비슷합니다.

| 바이트 | 조금 | 메모들 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 12월 | 16진수 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | 사용된 SPD 바이트 | ||||||||

| 1 | 0x01 | SPD 리비전 n | 일반적으로 0x10, 0x11, 0x12 | |||||||

| 2 | 0x02 | 기본 메모리 타입 (12 = DDR4 SDRAM) | RAM 칩의 종류 | |||||||

| 3 | 0x03 | 예약필 | 모듈 타입 | 모듈 유형(예: 2 = Unbuffered DIMM, 3 = SO-DIMM, 11 = LRDIMM) | ||||||

| 4 | 0x04 | 뱅크 그룹 비트 | 뱅크 주소 비트-2 | 다이당 총 SDRAM 용량(Gb) | 0은 은행 그룹이 없음을 의미합니다. 4개의 은행, 256 Mibit. | |||||

| 5 | 0x05 | 예약필 | 행 주소 비트-12 | 컬럼 주소 비트-9 | ||||||

| 6 | 0x06 | 프라이머리 SDRAM 패키지 타입 | 다이카운트 | 예약필 | 신호 로드 | |||||

| 7 | 0x07 | 예약필 | 최대 활성화 창(tMAW) | Maximum Activate Count(MAC; 최대 활성화 수) | SDRAM 옵션 기능 | |||||

| 8 | 0x08 | 예약필 | SDRAM 서멀 및 리프레시 옵션 | |||||||

| 9 | 0x09 | 패키지 수리 후(PPR) | 소프트 PPR | 예약필 | 기타 SDRAM 옵션 기능 | |||||

| 10 | 0x0a | SDRAM 패키지 유형 | 다이 카운트-1 | DRAM 밀도비 | 신호 로드 | 보조 SDRAM 패키지 유형 | ||||

| 11 | 0x0b | 예약필 | 엔듀란트 플래그 | 동작 가능한 플래그 | 모듈 공칭 전압, VDD | |||||

| 12 | 0x0c | 예약필 | 랭크 믹스 | DIMM-1당 패키지 등급 | SDRAM 디바이스 폭 | 모듈 구성 | ||||

| 13 | 0x0d | 예약필 | 버스 폭 확장 | 프라이머리 버스 폭 | 모듈 메모리 버스 폭(비트) | |||||

| 14 | 0x0e | 열센서 | 예약필 | 모듈 열 센서 | ||||||

| 15 | 0x0f | 예약필 | 확장 기본 모듈 유형 | |||||||

| 16 | 0x10 | 예약필 | ||||||||

| 17 | 0x11 | 예약필 | 중규모 타임베이스(MTB) | 미세 타임베이스(FTB) | ps 단위로 측정됩니다. | |||||

| 18 | 0x12 | 최소 SDRAM 사이클 시간(tminCKAVG) | MTB의 배수(예: 100/8 ns). | |||||||

| 19 | 0x13 | SDRAM의 최대 사이클 시간(tmaxCKAVG) | MTB의 배수(예: 60/8 ns). | |||||||

| 20 | 0x14 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 지원되는 CAS 지연 비트마스크 |

| 21 | 0x15 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 지원되는 CAS 지연 비트마스크 |

| 22 | 0x16 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 지원되는 CAS 지연 비트마스크 |

| 23 | 0x17 | 낮은 CL 범위 | 예약필 | 36 | 35 | 34 | 33 | 32 | 31 | 지원되는 CAS 지연 비트마스크 |

| 24 | 0x18 | 최소 CAS 지연 시간(tminAA) | MTB의 배수로, 예를 들어 1280/8 ns입니다. | |||||||

| 25 | 0x19 | RAS에서 CAS로의 최소 지연 시간(tminRCD) | MTB의 배수(예: 60/8 ns). | |||||||

| 26 | 0x1a | 최소 행 프리차지 지연 시간(tminRP) | MTB의 배수(예: 60/8 ns). | |||||||

| 27 | 0x1b | tminRAS 및 tmin의RC 상부 니블 | ||||||||

| 28 | 0x1c | 최소 활성 프리차지 지연 시간, tminRAS 최하위 바이트 | MTB의 배수 | |||||||

| 29 | 0x1d | 액티브에서 액티브/갱신까지의 최소 지연 시간, tminRC 최하위 바이트 | MTB의 배수 | |||||||

| 30 | 0x1e | 최소 새로 고침 복구 지연 시간(최소RFC1 유효 바이트 수) | MTB의 배수 | |||||||

| 31 | 0x1f | 최소 새로 고침 복구 지연 시간(최대RFC1 유효 바이트 수) | MTB의 배수 | |||||||

| 32 | 0x20 | 최소 새로 고침 복구 지연 시간(최소RFC2 유효 바이트 수) | MTB의 배수 | |||||||

| 33 | 0x21 | 최소 새로 고침 복구 지연 시간(최대RFC2 유효 바이트 수) | MTB의 배수 | |||||||

| 34 | 0x22 | 최소 새로 고침 복구 지연 시간(최소RFC4 유효 바이트 수) | MTB의 배수 | |||||||

| 35 | 0x23 | 최소 새로 고침 복구 지연 시간(최대RFC4 유효 바이트 수) | MTB의 배수 | |||||||

| 36 | 0x24 | 예약필 | tminFAW 최상위 니블 | |||||||

| 37 | 0x25 | 최소 4개의 활성화 창 지연 시간, tminFAW 최하위 바이트 | MTB의 배수 | |||||||

| 38 | 0x26 | 지연 시간, tminRRD_S, 다른 뱅크 그룹을 활성화하기 위한 최소 활성화 | MTB의 배수 | |||||||

| 39 | 0x27 | 지연 시간, tminRRD_L, 같은 뱅크 그룹을 활성화하기 위한 최소 활성화 | MTB의 배수 | |||||||

| 40 | 0x28 | CAS에서 CAS로의 최소 지연 시간(tminCCD_L, 같은 뱅크 그룹) | MTB의 배수 | |||||||

| 41 | 0x29 | tmin의WR 상부 니블 | ||||||||

| 42 | 0x2a | 최소 쓰기 복구 시간(tminWR) | MTB의 배수 | |||||||

| 43 | 0x2b | tmin의WTR 상한 니블 | ||||||||

| 44 | 0x2c | 읽기 시간, tminWTR_S, 다른 뱅크 그룹에 대한 최소 쓰기 | MTB의 배수 | |||||||

| 45 | 0x2d | 읽기 시간, tminWTR_L, 같은 뱅크 그룹에 대한 최소 쓰기 | MTB의 배수 | |||||||

| 49–59 | 0x2e~0x3b | 예약필 | 기본 설정 섹션 | |||||||

| 60–77 | 0x3c~0x4d | 커넥터와 SDRAM의 비트매핑 | ||||||||

| 78–116 | 0x4e~0x74 | 예약필 | 기본 설정 섹션 | |||||||

| 117 | 0x75 | CAS에서 CAS로의 최소 지연시간(tminCCD_L, 같은 뱅크)의 미세 오프셋 | FTB 유닛용 2개의 보완 승수 | |||||||

| 118 | 0x76 | 최소 활성화에 대한 미세 오프셋으로 지연 시간, tminRRD_L, 동일한 뱅크 그룹 활성화 | FTB 유닛용 2개의 보완 승수 | |||||||

| 119 | 0x77 | 최소 활성화에 대한 미세 오프셋으로 지연 시간, tminRRD_S, 다른 뱅크 그룹 활성화 | FTB 유닛용 2개의 보완 승수 | |||||||

| 120 | 0x78 | 최소 활성-활성/새로 고침 지연 시간(tminRC)에 대한 미세 오프셋 | FTB 유닛용 2개의 보완 승수 | |||||||

| 121 | 0x79 | 최소 행 프리차지 지연 시간에 대한 미세RP 오프셋(tmin) | FTB 유닛용 2개의 보완 승수 | |||||||

| 122 | 0x7a | 최소 RAS-CAS 지연시간(tminRCD)의 미세 오프셋 | FTB 유닛용 2개의 보완 승수 | |||||||

| 123 | 0x7b | 최소 CAS 지연 시간(tminAA)의 미세 오프셋 | FTB 유닛용 2개의 보완 승수 | |||||||

| 124 | 0x7c | SDRAM 최대 사이클 시간(tmaxCKAVG)의 미세 오프셋 | FTB 유닛용 2개의 보완 승수 | |||||||

| 125 | 0x7d | SDRAM 최소 사이클 시간(tminCKAVG)의 미세 오프셋 | FTB 유닛용 2개의 보완 승수 | |||||||

| 126 | 0x7e | 기본 구성 섹션의 Cyclic Redundancy Code(CRC; 순회 용장 코드), 최하위 바이트 | CRC16 알고리즘 | |||||||

| 127 | 0x7f | 기본 구성 섹션의 Cyclic Redundancy Code(CRC; 순회 용장 코드), 최상위 바이트 | CRC16 알고리즘 | |||||||

| 128–191 | 0x80~0xbf | 모듈 고유의 섹션 | 메모리 모듈 패밀리(UDIMM, RDIMM, LRDIMM)에 따라 다름 | |||||||

| 192–255 | 0xc0~0xff | 하이브리드 메모리 아키텍처 고유의 파라미터 | ||||||||

| 256–319 | 0x100~0x13f | 확장 함수 파라미터 블록 | ||||||||

| 320–321 | 0x140–0x420 | 모듈 제조원 | 'JEP-106' 참조 | |||||||

| 322 | 0x142 | 모듈 제조장소 | 제조사정의제조위치코드 | |||||||

| 323 | 0x143 | 모듈 제조년도 | BCD(Binary Coded Decimal)로 표시됨 | |||||||

| 324 | 0x144 | 모듈 제조 주간 | BCD(Binary Coded Decimal)로 표시됨 | |||||||

| 325–328 | 0x4 ~ 0x5 | 모듈 시리얼 번호 | 여러 부품 번호에 걸친 고유 일련 번호에 대한 제조업체 정의 형식 | |||||||

| 329–348 | 0x15c~0x15c | 모듈 부품 번호 | ASCII 부품 번호. 사용하지 않는 숫자는 0x20으로 설정해야 합니다. | |||||||

| 349 | 0x15d | 모듈 리비전 코드 | 제조사정의리비전코드 | |||||||

| 350–351 | 0x15e~0x15f | DRAM 제조원 ID 코드 | 'JEP-106' 참조 | |||||||

| 352 | 0x160 | DRAM 스테핑 | 제조업체 정의 스테핑 또는 사용하지 않는 경우 0xFF | |||||||

| 353–381 | 0x180~0x17d | 제조원 고유 데이터 | ||||||||

| 382–383 | 0x17e~0x17f | 예약필 | ||||||||

DDR5 SDRAM

JESD400-5 사양에 근거한 DDR5의 예비 표.

DDR5는 SPD 테이블을 1024바이트로 확장합니다.

| 바이트 | 조금 | 메모들 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 12월 | 16진수 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | SPD 디바이스의 바이트 수 | ||||||||

| 1 | 0x01 | 기본 구성 파라미터의 SPD 리비전 | ||||||||

| 2 | 0x02 | 키 바이트 / 호스트 버스 명령 프로토콜 유형 | ||||||||

| 3 | 0x03 | 키 바이트/모듈 유형 | ||||||||

| 4 | 0x04 | 최초의 SDRAM 밀도 및 패키지 | ||||||||

| 5 | 0x05 | 첫 번째 SDRAM 어드레싱 | ||||||||

| 6 | 0x06 | 첫 번째 SDRAM I/O 폭 | ||||||||

| 7 | 0x07 | 첫 번째 SDRAM 은행 그룹 및 은행 그룹별 은행 | ||||||||

| 8 | 0x08 | 두 번째 SDRAM 밀도 및 패키지 | ||||||||

| 9 | 0x09 | 두 번째 SDRAM 주소 지정 | ||||||||

| 10 | 0x0a | 두 번째 SDRAM I/O 폭 | ||||||||

| 11 | 0x0b | 두 번째 SDRAM 은행 그룹 및 은행 그룹당 은행 수 | ||||||||

| 12 | 0x0c | SDRAM 옵션 기능 | ||||||||

| 13 | 0x0d | 서멀 옵션 및 리프레시 | ||||||||

| 14 | 0x0e | 예약필 | ||||||||

| 15 | 0x0f | 예약필 | ||||||||

| 16 | 0x10 | SDRAM 공칭전압, VDD | ||||||||

내선번호

JEDEC 표준에서는 SPD 바이트의 일부만 지정되어 있습니다.정말 중요한 데이터는 처음 64바이트에 [6][7][15][16][17]들어가고 나머지는 제조업체 식별용으로 할당됩니다.단, 일반적으로 256바이트의 EEPROM이 제공됩니다.남은 공간은 여러 가지 용도로 사용되었습니다.

확장 퍼포먼스 프로파일(EPP)

메모리는 일반적으로 SPD ROM에서 권장되는 타이밍을 고려하여 모든 시스템에서 기본적인 기능을 보장합니다.애호가들은 많은 경우 고속화를 위해 메모리 타이밍을 수동으로 조정하는데 많은 시간을 소비합니다.

Enhanced Performance Profiles는 Nvidia 및 Corsair에 의해 개발된 SPD의 확장판입니다.이 확장판에는 공급전압 및 JEDEC SPD 사양에 포함되지 않은 명령 타이밍 정보 등 DDR2 SDRAM의 고성능 동작에 관한 추가 정보가 포함되어 있습니다.EPP 정보는 같은 EEPROM에 저장되지만 바이트99 ~ 127로 표준 DDR2 [18]SPD에서는 사용되지 않습니다.

| 바이트 수 | 크기 | 풀 프로파일 | 생략 프로파일 |

|---|---|---|---|

| 99–103 | 5 | EPP 헤더 | |

| 104–109 | 6 | 프로파일 FP1 | 프로파일 AP1 |

| 110–115 | 6 | 프로파일 AP2 | |

| 116–121 | 6 | 프로파일 FP2 | 프로파일 AP3 |

| 122–127 | 6 | 프로파일 AP4 | |

이 파라미터는 특히 nForce 5, nForce 6, nForce 7 칩셋의 메모리 컨트롤러에 적합하도록 설계되었습니다.Nvidia는 하이엔드 메인보드 칩셋에 대해 BIOS에서 EPP 지원을 권장합니다.이는 최소한의 노력으로 더 나은 성능을 얻기 위한 "원클릭 오버클럭"을 제공하기 위한 것입니다.

Nvidia는 퍼포먼스와 안정성을 인정받은EPP 메모리의 이름을 "SLI-ready memory"[19]라고 부릅니다."SLI-ready-memory"라는 용어는 SLI 비디오와는 아무런 관련이 없기 때문에 혼동을 일으킵니다.EPP/SLI 메모리는 1장의 비디오 카드(NVIDIA 이외의 카드도)로 사용할 수 있습니다.또, EPP/SLI 메모리 없이도 멀티 카드 SLI 비디오 셋업을 실행할 수 있습니다.

확장 버전 EPP 2.0은 [20]DDR3 메모리도 지원합니다.

Extreme Memory Profile(XMP)

인텔이 개발한 유사한 JEDEC SPD 확장 기능은 DDR3 SDRAM DIMM용으로 개발되었으며 나중에 DDR4에서도 사용됩니다.XMP는 JEDEC에 의해 할당되지 않은 바이트176~255를 사용하여 고성능 메모리타이밍을 [21]부호화합니다

이후 AMD는 [22][23]XMP와 동등한 테크놀로지인 AMP를 개발하여 AMD 플랫폼에서 사용하도록 최적화된 메모리 모듈인 "Radeon Memory" 제품군에 사용하였습니다.또, 메인보드 개발자는 독자적인 테크놀로지를 실장해, AMD 베이스의 메인보드가 XMP 프로파일을 읽어낼 수 있도록 했습니다.MSI는 A-XMP,[24] ASUS는 DOCP(Direct Over Clock Profile), Gigabyte는 EOCP(Extended Over Clock Profile)[25]입니다.

| DDR3 바이트 | 크기 | 사용하다 |

|---|---|---|

| 176–184 | 10 | XMP 헤더 |

| 185–219 | 33 | XMP 프로파일1 ('열정' 설정) |

| 220–254 | 36 | XMP 프로파일2 ('익스트림' 설정) |

헤더에는 다음 데이터가 포함되어 있습니다.가장 중요한 것은 "중간 타임베이스" 값 MTB가 나노초의 합리적인 수로 포함되어 있다는 것입니다(일반값은 1/8, 1/12 및 1/16 ns).그 외의 많은 타이밍 값은 MTB 단위의 정수수로 표현됩니다.

또, 이 헤더에는, 프로파일이 서포트하도록 설계된 메모리 채널 마다의 DIMM 의 수도 기재되어 있습니다.DIMM 이 많아지면, 제대로 동작하지 않는 경우가 있습니다.

| DDR3 바이트 | 비트 | 사용하다 |

|---|---|---|

| 176 | 7:0 | XMP 매직 번호 바이트 1 0x0C |

| 177 | 7:0 | XMP 매직 번호 바이트 2 0x4A |

| 178 | 0 | 프로파일 1이 네이블(0의 경우 디세이블) |

| 1 | 프로파일 2 활성화 | |

| 3:2 | 채널당 프로파일1의 DIMM (0 ~3으로 인코딩된1 ~ 4 ) | |

| 5:4 | 채널당 프로파일2개의 DIMM | |

| 7:6 | 예약필 | |

| 179 | 3:0 | XMP 마이너버전 번호(x.0 또는 x.1) |

| 7:4 | XMP 메이저버전 번호(0.x 또는 1.x) | |

| 180 | 7:0 | 프로파일 1의 중간 타임베이스 배당 |

| 181 | 7:0 | 프로파일 1의 중간 타임베이스 제수(MTB = 배당/제수 ns) |

| 182 | 7:0 | 프로파일 2의 중간 타임베이스 배당(예: 8) |

| 183 | 7:0 | 프로파일 2의 중간 타임베이스 약수(예: 1, MTB = 1/8 ns) |

| 184 | 7:0 | 예약필 |

| DDR3 바이트 1 | DDR3 바이트 2 | 비트 | 사용하다 |

|---|---|---|---|

| 185 | 220 | 0 | 모듈 Vdd 전압 20분의 1(0.00 또는 0.05) |

| 4:1 | 모듈 Vdd 전압의 10분의 1(0.0~0.9) | ||

| 6:5 | 모듈 Vdd 전압 단위(0~2) | ||

| 7 | 예약필 | ||

| 186 | 221 | 7:0 | 최소 SDRAM 클럭 간격 tminCK(MTB 단위) |

| 187 | 222 | 7:0 | 최소 CAS 지연 시간 tminAA(MTB 단위) |

| 188 | 223 | 7:0 | 지원되는 CAS 지연(비트맵, 비트0 ~ 7로 인코딩된4 ~ 11 ) |

| 189 | 224 | 6:0 | 지원되는 CAS 지연(비트맵, 비트0 ~ 6으로 인코딩된12 ~ 18) |

| 7 | 예약필 | ||

| 190 | 225 | 7:0 | 최소 CAS 쓰기 지연 시간 tminCWL(MTB 단위) |

| 191 | 226 | 7:0 | 최소 행 프리차지 지연 시간 tminRP(MTB 단위) |

| 192 | 227 | 7:0 | 최소 RAS-CAS 지연시간 tminRCD(MTB 단위) |

| 193 | 228 | 7:0 | 최소 쓰기 복구 시간 tminWR(MTB 단위) |

| 194 | 229 | 3:0 | tminRAS 상부 니블(비트 11:8) |

| 7:4 | tminRC 상부 니블(비트 11:8) | ||

| 195 | 230 | 7:0 | 프리차지 가능한 최소 활성 지연RAS 시간 tmin 비트 7:0(MTB 단위) |

| 196 | 231 | 7:0 | 최소 액티브에서 액티브/갱신 지연 시간 tminRC 비트 7:0(MTB 단위) |

| 197 | 232 | 7:0 | 최대 평균 새로 고침 간격REFI t lsbyte(MTB 단위) |

| 198 | 233 | 7:0 | 최대 평균 새로 고침 간격REFI tmsbyte(MTB 단위) |

| 199 | 234 | 7:0 | 최소 새로 고침 복구 지연 시간 tminRFC lsbyte(MTB 단위) |

| 200 | 235 | 7:0 | 최소 새로 고침 복구 지연 시간 tminRFC msbyte(MTB 단위) |

| 201 | 236 | 7:0 | 프리차지 명령 지연 시간 tminRTP(MTB 단위)을 위한 최소 내부 읽기 |

| 202 | 237 | 7:0 | 최소 활성 행 대 활성 행 지연 시간 tminRRD(MTB 단위) |

| 203 | 238 | 3:0 | tminFAW 상부 니블(비트 11:8) |

| 7:4 | 예약필 | ||

| 204 | 239 | 7:0 | 최소 4개의 활성화 창 지연 시간 tminFAW 비트 7:0(MTB 단위) |

| 205 | 240 | 7:0 | 최소 내부 읽기 명령 지연 시간 tminWTR(MTB 단위) |

| 206 | 241 | 2:0 | 읽기 명령어 턴어라운드 시간 조정(0~7 클럭 사이클) |

| 3 | 읽기 명령어 턴어라운드 조정 기호(0=pull-in, 1=pull-out) | ||

| 6:4 | 읽기 - 명령어 턴어라운드 시간 조정 (0~7 클럭 사이클) | ||

| 7 | 명령어 턴어라운드 조정 부호(0=풀인, 1=풀아웃)를 쓰기 위해 읽습니다. | ||

| 207 | 242 | 2:0 | Back-to-Back 명령어 턴어라운드 시간 조정(0~7 클럭 사이클) |

| 3 | 백 투 백(Back-to-Back) 조정 기호(0=당김, 1=풀아웃) | ||

| 7:4 | 예약필 | ||

| 208 | 243 | 7:0 | 시스템 CMD 속도 모드. 0=MTB × tCK/ns의 고유 단위로 기본 설정. 예를 들어, MTB가 1/8 ns인 경우, 이는 1/8 클럭 사이클 단위입니다. |

| 209 | 244 | 7:0 | SDRAM의 자동 자동 갱신 퍼포먼스 퍼포먼스 Standard 버전 1.1에서는 문서는 미완료입니다. |

| 210–218 | 245–253 | 7:0 | 예약필 |

| 219 | 254 | 7:0 | 예약된 벤더 고유의 퍼스낼리티 코드입니다. |

상기 데이터는 모두 DDR3(XMP 1.1)용입니다.DDR4 사양은 아직 제공되지 않습니다.

벤더 고유의 메모리

일반적인 오용은 벤더 고유의 메모리 모듈을 특정 시스템에 바인드하기 위해 특정 메모리 영역에 정보를 쓰는 것입니다.Fujitsu Technology Solutions는 이를 실현하는 것으로 알려져 있습니다.시스템에 다른 메모리 모듈을 추가하면 일반적으로 거부 또는 기타 대응책(부팅할 때마다 F1을 누르는 등)이 발생합니다.

02 0E 00 01-00 00 EF-02 03 19 4D-BC 47 C3 46 ........M.G.F 53 43 00 04-EF 4F 8D 1F-00 01 70 00-01 C1 CF SC...O....p......

이것은 Fujitsu-Siemens 컴퓨터용으로 브랜드 된 Micron Technologies의 512 MB 메모리 모듈의 출력입니다. "FSC" 문자열에 주의하십시오.시스템 BIOS는 이 정보가 없는 메모리 모듈을 오프셋 128시간부터 거부합니다.

일부 Packard Bell AMD 노트북에서도 이 방법을 사용하고 있습니다.이 경우 증상은 다양하지만 비프음이 아닌 커서가 깜박일 수 있습니다.덧붙여서,[27] 이것도 BIOS 파손의 증상일 가능성이 있습니다.2GB를 4GB로 업그레이드해도 문제가 발생할 수 있습니다.

SPD 정보 읽기 및 쓰기

메모리 모듈 제조업체는 SPD 정보를 모듈의 EEPROM에 씁니다.메인보드 BIOS에서 SPD 정보를 읽어 메모리 컨트롤러를 설정합니다.대부분의 메인보드 칩셋에서는 SPD 정보를 읽고 수정할 수 있는 프로그램이 몇 가지 있습니다.

- dmidecode 프로그램은 메모리(및 기타)에 대한 정보를 디코딩할 수 있으며 Linux, FreeBSD, NetBSD, OpenBSD, BeOS, Cygwin 및 Solaris에서 실행됩니다.dmidecode는 SPD 정보에 직접 액세스하지 않고 메모리에 [28]대한 SMBIOS 데이터를 보고합니다.이 정보는 제한적이거나 올바르지 않을 수 있습니다.

- Linux 시스템 및 FreeBSD에서는 i2c-tools에 의해 제공되는 사용자 공간 프로그램 디코딩-dimm이 컴퓨터 [29][30]내의 SPD 정보로 모든 메모리의 정보를 디코딩 및 인쇄합니다.여기에는 커널에서의 SMBus 컨트롤러 지원, EEPROM 커널 드라이버 및 SPD EEPROM이 SMBus에 연결되어 있어야 합니다.오래된 Linux 디스트리뷰션에서는 decode-dimms.pl을 lm_buffer의 일부로 사용할 수 있었습니다.

- OpenBSD에는 메모리 모듈에 대한 정보를 제공하는 드라이버(spdem(4))가 버전 4.3부터 포함되어 있습니다.이 드라이버는 NetBSD에서 이식되었으며 릴리스 5.0 이후 사용할 수 있습니다.

- Coreboot은 SPD 정보를 읽고 사용하여 타이밍, 크기 및 기타 속성을 가진 컴퓨터 내의 모든 메모리 컨트롤러를 초기화합니다.

- Windows 시스템에서는 SPD에서 DRAM 모듈 정보를 읽고 표시할 수 있는 HWiNFO,[31] CPU-Z, Speccy 등의 프로그램을 사용합니다.

칩셋에 의존하지 않는 SPD 정보의 읽기 및 쓰기는 EEPROM 프로그래머의 하드웨어 및 소프트웨어를 사용하여 메모리의 EEPROM에 직접 액세스함으로써 이루어집니다.

오래된 노트북의 일반적인 용도는 범용 SMBus 리더입니다.BIOS가 EEPROM을 읽으면 모듈의 내장 EEPROM이 비활성화되어 기본적으로 버스를 사용할 수 있기 때문입니다.사용되는 방법은 A0, A1 회선을 낮게 풀하여 내부 메모리를 셧다운하고 외부 디바이스가 SMBus에 액세스 할 수 있도록 하는 것입니다.이 작업이 완료되면 커스텀 Linux 빌드 또는 DOS 응용 프로그램이 외부 디바이스에 액세스할 수 있습니다.일반적인 용도는 LCD 패널 메모리 칩에서 데이터를 복구하여 범용 패널을 전용 노트북으로 개조하는 것입니다.일부 칩에서는 쓰기 보호 라인을 분리하여 온보드 칩이 재프로그래밍 중에 지워지지 않도록 하는 것도 좋습니다.버스 속도가 상당히 빨라 칩 장애 발생 시 25x 호환 칩을 나중에 uEFI 복제용으로 다시 읽을 수 있도록 수정할 수 있기 때문에 많은 노트북에 포함된 웹캠에 칩을 다시 쓰는 기술도 있습니다.

DDR4는 다른 보안을 사용하여 보통 읽기만 가능하기 때문에 이 기능은 DDR3 이하에서만 작동합니다.SPDTool과 같은 툴을 사용하여 칩을 WP 라인이 없는 칩으로 교체하여 현장에서 변경할 수 있습니다.일부 칩셋에서는 "Incompatible SMBus driver?"라는 메시지가 표시될 수 있으므로 읽을 수도 없습니다.

RGB LED 제어

일부 메모리 모듈(특히 게임용 PC)[32]은 자체 SMBus 명령에 의해 제어되는 RGB LED를 지원합니다.이것에 의해, 커넥터나 케이블을 증설하지 않아도 LED의 색상을 제어할 수 있습니다.조명을 제어하는 데 필요한 여러 제조업체의 커널 드라이버가 2020년에만 [33][34][35]여러 번 악용되어 완전한 커널 메모리 액세스에서 MSR 및 I/O 포트 제어에 이르기까지 다양한 액세스 권한을 얻고 있습니다.

오래된 기기

일부 오래된 기기에서는 병렬 존재 검출 기능이 있는 SIMM(더 일반적으로 존재 검출 또는 PD라고 불립니다)을 사용해야 합니다.이 장비 중 일부는 비표준 PD 코딩, IBM 컴퓨터 및 Hewlett-Packard LaserJet 및 기타 프린터를 사용합니다.

「 」를 참조해 주세요.

레퍼런스

- ^ Thomas P. Koenig; Nathan John (3 February 1997), "Serial Presence Detection poised for limelight", Electronic News, 43 (2153)

- ^ JEDEC Standard 21-C 섹션 4.1.4 "메모리 모듈 애플리케이션용 온도 센서(TS)를 갖춘 TSE2002av 시리얼 존재 검출(SPD) EEPROM의 정의"

- ^ "TN-04-42: Memory Module Serial Presence-Detect Write Protection" (PDF). Micron.

- ^ 애플리케이션 노트 IN-8668-APN3: SDRAM SPD 데이터 표준, memorytesters.com

- ^ PC SDRAM Serial Presence Detect (SPD) Specification (PDF), 1.2A, December 1997, p. 28

- ^ a b JEDEC Standard 21-C 섹션 4.1.2.4 "DDR SDRAM용 SPD"

- ^ a b JEDEC Standard 21-C 섹션 4.1.2.10 "DDR2 SDRAM 전용 SPD"

- ^ "Understanding DDR3 Serial Presence Detect (SPD) Table".

- ^ JESD21-C Annex K: DDR3 SDRAM 모듈의 시리얼 존재 검출, 릴리즈 4, SPD 리비전 1.1

- ^ JESD21-C Annex K: DDR3 SDRAM 모듈의 시리얼 존재 검출, 릴리즈 6, SPD 리비전 1.3

- ^ Delvare, Jean. "[PATCH] eeprom: New ee1004 driver for DDR4 memory". LKML. Retrieved 7 November 2019.

- ^ a b JEDEC. "Annex L: Serial Presence Detect (SPD) for DDR4 SDRAM Modules" (PDF).

- ^ JEDEC. "EE1004 and TSE2004 Device Specification (Draft)" (PDF). Retrieved 7 November 2019.

- ^ JESD21-C Annex L: DDR4 SDRAM 모듈의 시리얼 존재 검출 릴리즈 5

- ^ JEDEC Standard 21-C 섹션 4.1.2.11 "DDR3 SDRAM 모듈용 시리얼 존재 검출(SPD)"

- ^ JEDEC 표준 21-C 섹션 4.1.2 "시리얼 존재 검출 표준, 일반 표준"

- ^ JEDEC Standard 21-C 섹션 4.1.2.5 "동기 DRAM(SDRAM)을 위한 특정 PD"

- ^ DDR2 UDIMM Enhanced Performance Profiles Design Specification (PDF), Nvidia, 12 May 2006, retrieved 5 May 2009

- ^ http://www.nvidia.com/docs/CP/45121/sli_memory.pdf[베어 URL PDF]

- ^ 확장 퍼포먼스 프로파일 2.0 (2-3페이지)

- ^ "Intel Support". Intel.

- ^ Advanced Micro Devices, Inc (2012). "Memory Profile Technology - AMP up your RAM". Retrieved 8 January 2018.

- ^ Ryan Martin (23 July 2012). "AMD introduces its XMP-equivalent AMP - eTeknix". Retrieved 8 January 2018.

- ^ Micro-Star Int'l Co., Ltd (21 March 2017). "MSI is worlds first brand to enable A-XMP on Ryzen for best DDR4 performance, launches new models". Retrieved 8 January 2018.

- ^ Tradesman1 (26 August 2016). "What does XMP, DOCP, EOCP mean - Solved - Memory". Retrieved 8 January 2018.

- ^ a b c Intel Extreme Memory Profile (XMP) Specification, Rev 1.1 (PDF), October 2007, archived from the original (PDF) on 6 March 2012, retrieved 25 May 2010

- ^ "Packard Bell LJ65 RAM upgrade". Tom's Hardware Forum.

- ^ "dmidecode: What's it good for?". Linux.com The source for Linux information. 29 November 2004.

- ^ "decode-dimms(1)". Debian Manpage. Retrieved 16 December 2020.

- ^ "decode-dimms". www.freebsd.org. Retrieved 24 January 2021.

- ^ "HWiNFO - Professional System Information and Diagnostics". HWiNFO.

- ^ "VENGEANCE RGB PRO series DDR4 memory Desktop Memory CORSAIR". www.corsair.com. Retrieved 26 November 2020.

- ^ ActiveCyber. Viper RGB Driver Local Privilege Escalation (Technical report). CVE-2019-18845 – via MITRE Corporation.

- ^ ActiveCyber. CORSAIR iCUE Driver Local Privilege Escalation (CVE-2020-8808) (Technical report). CVE-2020-8808 – via MITRE Corporation.

- ^ ActiveCyber. ACTIVE-2020-003: Trident Z Lighting Control Driver Local Privilege Escalation (Technical report). CVE-2020-12446 – via MITRE Corporation.

외부 링크

- 시리얼 존재 검출 표준, 일반 표준

- DDR SDRAM용 SPD Rev1.0

- DDR2 SDRAM용 SPD Rev1.2

- DDR2 SDRAM용 SPD Rev1.3

- 스페셜리티 DDR2-1066 SDRAM

- Linux 패키지 i2c-tools

- lm-sensors 또는 i2c-tools를 사용하여 데이터를 읽는 방법에 대한 지침 2007년 5월 19일 웨이백 머신에 보관됨

- 메모리 퍼포먼스: 16GB DDR3-1333-DDR3-2400 (Ivy Bridge IGP, G 탑재)스킬 – 다양한 타이밍 값 설명