펜티엄 프로

Pentium Pro | |

| 일반 정보 | |

|---|---|

| 개시. | 1995년 11월 1일 |

| 단종 | 1998년 6월 |

| 공통 제조원 | |

| 성능 | |

| 최대 CPU 클럭 속도 | 150MHz~200MHz |

| FSB 속도 | 60MHz~66MHz |

| 아키텍처 및 분류 | |

| 테크놀로지 노드 | 0.35μm~0.50μm |

| 마이크로아키텍처 | P6 |

| 명령 집합 | x86 |

| 물리 사양 | |

| 코어 |

|

| 소켓 | |

| 역사 | |

| 전임자 | 펜티엄 |

| 후계자 | Pentium II, Pentium II Xeon |

Pentium Pro는 인텔이 개발 및 제조하여 1995년 [1]11월 1일에 선보인 6세대 x86 마이크로프로세서입니다.P6 마이크로아키텍처(i686)를 도입하여 원래 Pentium을 모든 어플리케이션에서 대체하기 위한 것입니다.펜티엄과 펜티엄 MMX는 각각 310만개의 트랜지스터와 450만개의 트랜지스터를 가지고 있었지만 펜티엄 프로는 550만개의 트랜지스터를 [2]가지고 있었다.이후 서버 및 하이엔드 데스크톱 프로세서로서의 역할이 축소되어 ASCI Red와 같은 슈퍼컴퓨터에 사용되었습니다.ASCI Red는 1초당 부동소수점 연산수(teraFLOPS) 퍼포먼스 [3]기록을 달성한 최초의 컴퓨터입니다.Pentium Pro는 듀얼 프로세서 구성과 쿼드 프로세서 구성을 모두 지원했습니다.이 제품은 비교적 큰 직사각형 소켓 8이라는 하나의 폼 팩터로만 제공되었습니다.Pentium Pro는 1998년에 Pentium II Xeon에 의해 계승되었습니다.

마이크로아키텍처

Pentium Pro의 수석 설계자는 슈퍼 스케일러빌리티에 특화된 프레드 폴락으로 인텔 iAPX 432의 [4]수석 엔지니어로도 일했습니다.

요약

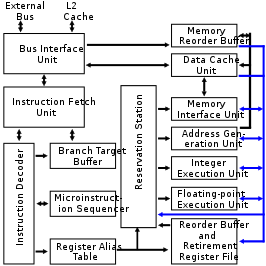

Pentium Pro는 Pentium의 P5 마이크로아키텍처와는 다른 새로운 마이크로아키텍처를 채택했습니다.명령 풀을 사용한 디커플링된 14단계 슈퍼파이프라인 아키텍처가 있습니다.Pentium Pro(P6)는 NexGen Nx586 및 Cyrix 6x86 등 현대의 다른 x86 디자인을 반영하여 많은 아키텍처상의 차이를 구현했습니다.Pentium Pro 파이프라인에는 IA-32 명령어를 버퍼링된 마이크로 오퍼레이션 시퀀스로 동적으로 변환하는 추가 디코드 단계가 있었습니다.이러한 시퀀스는 여러 실행 유닛에 동시에 발행될 수 있는 병렬 가능한 오퍼레이션을 검출하기 위해 분석, 순서 변경 및 이름 변경을 할 수 있었습니다.따라서 펜티엄 프로는 레지스터 이름 변경을 통한 투기적 실행을 포함하여 순서가 맞지 않는 실행을 특징으로 했습니다.또한 물리 주소 확장(PAE)에서 사용할 수 있는 보다 넓은 36비트 주소 버스도 있어 최대 64GB의 메모리에 액세스할 수 있습니다.

Pentium Pro에는 8KB 명령 캐시가 있으며, 각 사이클에서 최대 16바이트가 가져와 명령 디코더로 전송됩니다.명령 디코더는 세 가지가 있습니다.디코더 기능은 동일하지 않습니다.x86 명령어를 디코딩할 수 있는 것은 1개뿐이며, 다른 2개는 단순한 x86 명령어만 디코딩할 수 있습니다.이로 인해 Pentium Pro가 여러 명령을 동시에 디코딩할 수 있는 기능이 제한되고 슈퍼스칼라 실행이 제한됩니다.x86 명령어는 118비트 마이크로 오퍼레이션(마이크로 ops)으로 디코딩됩니다.마이크로 ops는 RISC(Reduced Instruction Set Computer)와 같은 연산, 2개의 소스 및 대상을 인코딩합니다.일반 디코더는 사이클당 최대 4개의 마이크로 ops를 생성할 수 있지만 단순 디코더는 사이클당 1개의 마이크로 ops를 생성할 수 있습니다.따라서, 메모리상에서 동작하는 x86 명령(예를 들면, 이 레지스터를 메모리의 이 위치에 추가)은, 이 조작에는 적어도 3 마이크로 ops가 필요하기 때문에, 일반 디코더에 의해서만 처리될 수 있습니다.마찬가지로 간단한 디코더는 하나의 마이크로 오퍼로 변환할 수 있는 명령어로 제한됩니다.4개 이상의 마이크로 ops가 필요한 명령은 시퀀서의 도움을 받아 변환됩니다.시퀀서는 여러 클럭사이클에 걸쳐 필요한 마이크로 ops를 생성합니다.Pentium Pro는 x86 패밀리에서 BIOS 및/또는 운영체제([5]OS) 제어 하에 업그레이드 가능한 마이크로코드를 지원하는 최초의 프로세서입니다.

마이크로 ops는 Re-order Buffer(ROB)에서 나와 Reserve Station(RS; 예약 스테이션)으로 들어가 실행 유닛으로의 디스패치를 기다립니다.각 클럭 사이클에서 최대 5개의 마이크로옵스를 5개의 실행 유닛에 디스패치할 수 있습니다.Pentium Pro에는 정수 유닛 2개, 부동소수점 유닛(FPU), 로드 유닛, 스토어 주소 유닛 및 스토어 데이터 [6]유닛의 총 6개의 실행 유닛이 있습니다.정수 유닛 중 하나는 FPU와 동일한 포트를 공유하기 때문에 Pentium Pro는 다른 3개의 실행 유닛의 마이크로 op과 더불어 사이클당 1개의 정수 마이크로 op과 1개의 부동 소수점 마이크로 op 또는2개의 정수 마이크로 op만을 디스패치할 수 있습니다.2개의 정수 유닛 중 포트 0의 FPU와 경로를 공유하는 유닛만이 배럴 시프터, 멀티플라이어, 디바이다, LEA 명령 지원 등의 모든 기능을 갖추고 있습니다.포트 1에 접속되어 있는두 번째 정수 유닛에는 이러한 기능이 없으며, 브랜치타깃 [6]주소의 덧셈, 뺄셈, 계산 등의 간단한 조작으로 제한됩니다.

FPU는 부동소수점 연산을 실행합니다.덧셈과 곱셈은 파이프라인 처리되며 지연 시간은 각각 3사이클과 5사이클입니다.분할 및 제곱근은 파이프라인되지 않으며 FPU 포트를 공유하는 개별 단위로 실행됩니다.나눗셈과 제곱근의 지연 시간은 각각 18-36과 29-69입니다.최소값은 단일 정밀도(32비트) 부동 소수점 번호용이고 최대값은 확장 정밀도(80비트) 번호용입니다.나눗셈과 제곱근은 덧셈과 곱셈을 동시에 실행할 수 있으므로 결과를 ROB에 저장해야 하는 경우에만 실행할 수 없습니다.

마이크로프로세서가 출시된 후 일반적으로 "Pentium Pro 및 Pentium II FPU 버그"라고 불리는 부동소수점 유닛과 "Flag erratum"이라고 불리는 인텔에 의해 버그가 발견되었습니다.부동소수점 대 정수 변환 중에 부동소수점 번호가 작은 정수 형식에 맞지 않는 경우에 이 오류가 발생하여 FPU가 문서화된 동작에서 벗어납니다.이 버그는 경미한 것으로 간주되며 영향을 받는 소프트웨어 프로그램은 극히 적습니다.

Pentium Pro P6 마이크로아키텍처는 인텔에 의해 10년 이상 사용되어 왔습니다.파이프라인은 "Tualatin" Pentium III를 사용하면 초기 150MHz에서 최대 1.4GHz까지 확장됩니다.Pentium M과 인텔 Core(Yonah)의 파생 코어로 불리는 Banias가 2006년 이후 [7]Core 마이크로아키텍처(Core 2 프로세서)로 진화하는 등 설계의 다양한 특성이 계속됩니다.

명령 집합

Pentium Pro(P6)는 Intel 범위에 새로운 명령을 도입했습니다.CMOVxx('조건부 이동') 명령은 레지스터의 내용 또는 메모리 위치 중 하나의 값을 다른 레지스터로 이동할 수 있습니다.플래그 레지스터의 일부 술어 논리 조건 xx에 따르면 xx는 조건에 따라 플래그 술어 코드입니다.조건 점프 지시용 이온.예를 들어 CMOVNE은 플래그 레지스터 ie Z 플래그 = 0에서 NE(비표준) 조건이 참인지 여부에 따라 지정된 값을 레지스터로 이동합니다.이를 통해 if-then-else 연산, 예를 들어 C의 ? : 연산 등을 평가할 수 있습니다.이러한 명령어를 사용하면 비용이 많이 드는 점프 및 분기 명령을 피할 수 있으므로 성능이 향상됩니다.예를 들어 CMOVxx destreg1(source_operand2)에서는 첫 번째 오퍼랜드가 수신처 레지스터이고 두 번째 오퍼랜드가 소스 레지스터 또는 메모리 위치입니다.불행히도 두 번째 피연산자는 즉시(인라인 상수) 값이 될 수 없으며 이러한 상수는 먼저 레지스터에 배치되어야 합니다.술어 코드 xx는 조건부 브랜치에서 허용되는 모든 범위의 값을 사용할 수 있습니다.

두 번째 개발은 UD2 불법 명령의 문서화였다.이 op 코드는 예약되어 있으며 P6 이후의 모든 프로세서에서 부정 명령 예외를 발생시킬 수 있습니다.이를 통해 개발자들은 소프트웨어에 의해 버그가 발견되었을 때 현재 프로그램을 미래에 대비한 방식으로 쉽게 크래시할 수 있다.

성능

Pentium Pro의 비순서 레지스터 이름 변경 아키텍처는 한동안 고급화되었지만, 부분 레지스터를 사용하면 파이프라인 [8]플러시가 자주 발생하기 때문에 16비트 코드와 혼합 코드 (16/16비트 포함 8비트 또는 32비트 포함 16비트)를 실행하는 데 문제가 있었습니다.P6 이전의 인텔 프로세서에서는 성능 저하가 발생하지 않았기 때문에 특정 레지스터의 사용은 일반적인 성능 최적화였습니다.또한 Pentium Pro의 출시 당시 주요 운영체제는 16비트 DOS였고 16/32비트 Windows 3.1x와 Windows 95가 혼합되어 있었습니다(단, Pentium Pro는 32비트 80386 CPU를 필요로 했습니다.USER.exe 등의 퍼포먼스상의 이유로 코드는 아직 16비트입니다.이는 펜티엄 프로 시스템의 고비용과 함께 당시 PC 구매자들 사이에서 미온적인 판매로 이어졌다.Pentium Pro의 P6 마이크로 아키텍처를 완전히 사용하려면 Windows NT, Linux, Unix 또는 OS/2와 같은 완전한 32비트 운영 체제가 필요합니다.레거시 코드의 퍼포먼스 문제는 나중에 인텔 Pentium II에 의해 일부 완화되었습니다.

RISC 마이크로프로세서와 비교하여 Pentium Pro는 SPECint95 [9]벤치마크를 실행했을 때 정수 퍼포먼스에서 가장 빠른 RISC 마이크로프로세서를 약간 웃돌았지만 부동소수점 퍼포먼스는 일부 RISC [9]마이크로프로세서의 절반인 대폭 낮았습니다.Pentium Pro의 정수 퍼포먼스 리드는 1996년 1월 MIPS 테크놀로지스 R10000에 의해, 그 후 디지털 이그니션 코퍼레이션의 Alpha 21164의 [10]EV56에 의해 급속히 없어졌습니다.

리뷰어는 비디오 메모리에 대한 쓰기가 매우 느린 것을 P6 플랫폼의 약점으로 지적했습니다.여기서 VIDSPEED 등의 벤치마크에서는 같은 클럭의 Pentium 시스템의 퍼포먼스가 10%나 저하되고 있습니다.방법 이것을 회피하기 위해 Quake,[11] 같은 게임과 FASTVID 나타났다 등 쓰기 등록(MTRRs)자동으로 창호가 설정한 CPU.[12][13]메모리 형식 범위의 특성을 결합함을 활성화한 특정 게임 성능 두배가 될 수 있유틸리티, 나중에 시스템 메모리에 설정 VESA그림 대신 비디오 메모리 포함했다.s비디오 dri1997년부터는 캐시/메모리 서브시스템과 FPU 퍼포먼스가 향상되어 1990년대 중후반, 특히 NT4를 사용하는 경우 새롭게 등장한 3D 게임에서는 Pentium 클럭/클럭을 능가하게 되었습니다.그러나 MMX 구현이 부족하기 때문에 이러한 명령을 사용한 멀티미디어 애플리케이션의 성능이 저하됩니다.

캐싱

펜티엄 프로의 가장 눈에 띄는 추가 기능은 온패키지 L2 캐시로 출시 당시 256KB에서 1997년 1MB까지 다양했다.당시 제조기술로는 프로세서 코어에 대용량 L2 캐시를 통합할 수 없었습니다.대신 인텔은 L2 다이(die)를 패키지에 별도로 장착하여 CPU 코어와 동일한 클럭 속도로 실행할 수 있도록 했습니다.또한 메인 시스템 버스를 CPU와 공유하던 대부분의 메인보드 기반 캐시 스킴과는 달리 Pentium Pro의 캐시에는 자체 백사이드 버스(인텔에서는 듀얼 인디펜던트 버스라고 부릅니다)가 있었습니다.이로 인해 CPU는 메인 메모리와 캐시를 동시에 읽을 수 있어 기존의 병목 현상을 [14]크게 줄일 수 있었습니다.또한 캐시는 "비블로킹"이었기 때문에 프로세서가 한 번에 여러 캐시 요청을 발행할 수 있어(최대 4개) 캐시 미스 패널티를 줄일 수 있었습니다.(다음은 MLP, 메모리레벨 병렬화의 예입니다).이러한 속성을 조합하여 오래된 프로세서의 메인보드 기반 캐시보다 엄청나게 빠른 L2 캐시를 생성했습니다.이 캐시만으로도 CPU는 오래된 x86 CPU에 비해 입출력 성능이 우수합니다.멀티프로세서 구성에서는 각 CPU가 중앙 캐시를 공유하는 아키텍처에 비해 Pentium Pro의 통합 캐시는 성능이 비약적으로 향상되었습니다.

그러나 이 훨씬 빠른 L2 캐시에는 몇 가지 문제가 있었습니다.Pentium Pro의 "온패키지 캐시" 배열은 독특했습니다.프로세서와 캐시는 동일한 패키지로 별도의 다이 상에 있으며 최대 속도 버스에 의해 밀접하게 연결되어 있습니다.두세 개의 다이는 테스트가 가능하기 전에 생산 공정 초기에 서로 접합되어야 했습니다.이는 어느 한 금형에 작은 결함이 있어 전체 어셈블리를 폐기해야 한다는 것을 의미하며, 이것이 펜티엄 프로의 상대적으로 낮은 생산 수율과 높은 비용의 원인 중 하나였다.프로세서 다이와 함께 512KB 캐시 다이 2개가 필요했기 때문에 칩의 모든 버전이 비쌌으며, 1024KB의 칩은 특히 비쌌습니다.

이용 가능한 모델

Pentium Pro의 클럭 속도는 150, 166, 180 또는 200MHz, 외부 버스 클럭은 60 또는 66MHz였습니다.200MHz 버전은 233MHz, 180MHz 버전은 200MHz, 150MHz 버전은 166MHz에서 실행되는 등 Pentium Pro 칩을 오버클럭하는 사용자도 있습니다.이 칩은 대칭형 멀티프로세싱 구성에서 널리 사용되었으며 듀얼 및 쿼드 SMP 서버와 워크스테이션 설정이 일반적이었습니다.

인텔의 「패밀리/모델/스테핑」스킴에서는, Pentium Pro는 패밀리 6, 모델 1, 인텔 제품 코드는 80521 입니다.

| 시계 (MHz) | 버스 (MHz) | L2 캐시 (KB) | 맥스. TDP (W) |

|---|---|---|---|

| 150 | 60 | 256 | 29.2 |

| 166 | 66 | 512 | 35 |

| 180 | 60 | 256 | 31.7 |

| 200 | 66 | 35 | |

| 512 | 37.9 | ||

| 1024 | 44 |

제조

Pentium Pro 프로세서 다이와 개별 캐시 메모리 다이 제조에 사용되는 프로세스가 변경되어 동일한 패키지에 사용되는 프로세스가 조합되었습니다.

- 133MHz Pentium Pro의 시제품 프로세서 다이는 0.6μm BiCMOS [15][16]프로세스로 제작되었습니다.

- 150MHz Pentium Pro 프로세서 다이는 0.50μm BiCMOS [16][9]프로세스로 제작되었습니다.

- 166, 180 및 200MHz Pentium Pro 프로세서 다이는 0.35μm BiCMOS 프로세스로 [16][9]제작되었습니다.

- 256KB L2 캐시 다이는 0.50μm BiCMOS 프로세스로 [16][9]제작되었습니다.

- 512 KB 및 1024 KB L2 캐시 다이는 0.35 μm BiCMOS 프로세스로 [16][9]제작되었습니다.

패키징

Pentium Pro(최대 512KB 캐시)는 세라믹 멀티칩 모듈(MCM)에 포함되어 있습니다.MCM에는 마이크로프로세서 다이와 그 부속 캐시 다이가 있는 2개의 하부 공동이 있습니다.다이는 히트슬러그에 결합되어 있으며, 이 히트슬러그의 노출된 상단은 다이의 열이 히트싱크와 같은 냉각장치로 더 직접적으로 전달되도록 도와줍니다.다이는 기존의 와이어 본딩을 사용하여 패키지에 연결됩니다.충치에는 세라믹 플레이트가 씌워져 있습니다.

1 MB 캐시를 탑재한 Pentium Pro는 플라스틱 MCM을 사용합니다.2개의 캐비티 대신, 3개의 다이(die)가 있는 패키지에 히트슬러그 대신 접합된 단 한 개의 캐비티만 있습니다.그 구멍들은 에폭시로 채워져 있다.

MCM에는 387개의 핀이 있으며, 그 중 약 절반은 Pin Grid Array(PGA; 핀 그리드 어레이)에, 나머지 절반은 Interstitial Pin Grid Array(IPGA; 인터스티셜 핀 그리드 어레이)에 배치되어 있습니다.패키지는 소켓8용으로 설계되어 있습니다.

업그레이드 경로

1998년 소켓8용 300/333 MHz Pentium II 오버드라이브 프로세서가 출시되었습니다.인텔은 2배의 L1과 512KB의 풀 스피드 L2 캐시를 탑재하여 Pentium Pro 시스템 소유자를 위한 드롭인 업그레이드 옵션으로 생산되었습니다.단, 4방향 이상이 아닌 2방향 글루리스 멀티프로세싱만 지원했기 때문에 쿼드프로세서 시스템에서 사용할 수 있는 업그레이드는 되지 않았습니다.이 특별한 패키징의 Pentium II Xeon 프로세서는 ASCI Red 업그레이드에 사용되었습니다.ASCI Red는 Pentium Pro 프로세서를 탑재한 최초의 컴퓨터이며, Pentium II Xeon 프로세서로 업그레이드한 후 2테라 FLOPS를 넘는 최초의 컴퓨터가 되었습니다.

슬롯 1 메인보드가 보급됨에 따라 Tyan M2020, Asus C-P6S1, Tekram P6SL1, Abit KP6와 같은 여러 제조업체에서 슬럭 어댑터를 출시했습니다.슬롯 1 메인보드에서 Pentium Pro 프로세서를 사용할 수 있게 되었습니다.인텔 440FX 칩셋은 Pentium Pro 프로세서와 Pentium II 프로세서를 모두 지원하지만 인텔 440BX 이후의 슬롯1 칩셋은 Pentium Pro를 지원하지 않기 때문에 소켓8 슬롯셋은 널리 사용되지 않습니다.Slockets는 Socket 370에서 Slot 1 어댑터의 형태로 인텔이 Socket 370 Celeron 및 Pentium III 프로세서를 출시했을 때 새로운 인기를 얻었습니다.

핵심사양

펜티엄 프로

- L1 캐시: 8, 8 KB (데이터, 명령)

- L2 캐시: 256, 512KB(1다이), 또는 1024KB(2다이 512KB)의 멀티칩 모듈로 CPU 속도로 클럭 설정

- 소켓: 소켓8

- 프론트 사이드 버스: 60 MHz 및 66 MHz

- VCore: 3.1 ~3.3 V

- 제조: 0.50μm 또는 0.35 BiCMOS[17]

- 클럭레이트: 150, 166, 180, 200MHz(일부 메인보드에서는 233MHz 지원)

- 첫 번째 출시:1995년 11월

Pentium II 오버드라이브

- L1 캐시: 16, 16 KB (데이터 + 명령)

- L2 캐시: CPU 모듈 상의 512KB 외부 칩을 CPU 속도로 클럭 설정

- 소켓: 소켓8

- 승수:5×로 고정

- 프론트 사이드 버스: 60 MHz 및 66 MHz

- VCore: 3.1~3.3 V (온보드 전압 레귤레이터 탑재)

- 제조: 0.25μm

- Clockrate: Deschutes 세대 Pentium II 기반

- 초판 : 1997년

- MMX 테크놀로지 지원

버스 및 멀티프로세서 기능

Pentium Pro는 전면 버스에 [19]GTL+ 시그널링을 사용했습니다.펜티엄 프로는 최대 4방향 디자인으로 단독으로 사용할 수 있습니다.8방향 펜티엄 프로 컴퓨터도 만들어졌지만, 이것들은 [20]여러 개의 버스를 사용했다.

Pentium Pro 버스의 디자인은 Futurebus, 인텔 iAPX 432 버스 및 인텔 i960 [21]버스의 요소에 영향을 받았습니다.Futurebus는 1970년대 후반부터 Motorola 68000에 사용된 VMEbus를 대체하는 고급 버스로 개발되었지만, 모든 [21]우여곡절을 종합하면 표준화 위원회에서 10년 이상 정체되었다.인텔의 iAPX 432 이니셔티브도 상업적인 실패였지만, 그 과정에서 캐시리스 멀티프로세서 시스템을 지원하는 스플릿 트랜잭션 버스를 구축하는 방법을 배웠습니다.i960은 캐시 일관성 프로토콜을 포함하기 위해 분할 트랜잭션 iAPX 432 버스를 추가로 개발하였고, 결국 원래의 Futurebus [21]야망을 매우 연상시키는 기능 세트를 갖게 되었다.

i960의 수석 설계자는 인텔 iAPX 432의 수석 엔지니어이자 i686 칩인 Pentium Pro의 수석 설계자인 슈퍼 스케일러리티 스페셜리스트 프레드 폴락이었습니다.그는 틀림없이 이 모든 역사를 잘 알고 있었다.Pentium Pro는 4방향 SMP 스플릿 트랜잭션 캐시 코히런트 버스를 모든 [21]칩의 필수 기능으로 포함하도록 설계되었습니다.이는 또한 복제된 [21]프로세서를 생산하기 위해 소켓에 대한 경쟁 액세스를 거부하는 역할도 했습니다.

반면 펜티엄 프로가 대중을 위해 기계를, Windows95을 위해 불쌍한 16비트 지원에 기인되어 성공하지는 않았으나, 파일을 서버 공간에 그들의 진보한, 통합 버스 design,[21]때문에 성공할 했던 이전만 상품 시장에 비싼 워크스테이션 분야에 이용 될 수 있었더라면 많은 진보된 기능을 소개하겠다.place.

Pentium Pro/6세대 경쟁 제품

「 」를 참조해 주세요.

레퍼런스

- ^ Fisher, Lawrence M. (November 2, 1995). "Intel Offers Its Pentium Pro For Work Station Market". The New York Times. Retrieved January 4, 2012.

- ^ Brey, Barry (2006). The Intel Microprocessors. p. 12.

- ^ "ASCI Red: Sandia National Laboratory". TOP500 Supercomputer Sites.

- ^ Dvorak, John C. "Whatever Happened to The iAPX432 – Intel's Dream Chip?". Dvorak Uncensored.

- ^ Stiller, Andreas; Paul, Matthias R. (May 12, 1996). "Prozessorgeflüster". c't – magazin für computertechnik. Trends & News (in German). Heise Verlag. Archived from the original on August 28, 2017. Retrieved August 28, 2017.

- ^ a b "Intel Architecture Optimization Manual" (PDF). 1997. p. 2-8. Archived from the original (PDF) on January 21, 2007.

- ^ Stokes, Jon (April 5, 2006). "Into the Core: Intel's next-generation microarchitecture". Retrieved April 24, 2009.

- ^ "Partial Register Stall Warning". VTune Performance Analyzer online help.

- ^ a b c d e f Slater, Michael (November 13, 1995). "Intel Boosts Pentium Pro to 200 MHz". Microprocessor Report. MicroDesign Resources. Vol. 9, no. 15.

- ^ Gwennap, Linley (July 8, 1996). "Digital's 21164 Reaches 500 MHz". Microprocessor Report.

- ^ "Quake/TECHINFO.TXT at master · id-Software/Quake".

- ^ "Quake Technical Information file".

- ^ "MDGx Complete UMBPCI.sys Guide".

- ^ "Accelerated Graphics Port". Next Generation. No. 37. Imagine Media. January 1998. pp. 94–96.

- ^ 팹워스, 데이비드 B.(1996년 4월)."Pentium Pro 마이크로아키텍처 조정"IEEE Micro, 페이지 14-15.

- ^ a b c d e "Intel Pentium Pro Processors - Fact Sheet". Intel. Archived from the original on December 7, 2013.

- ^ sandpile.org 아카이브 1999-09-01 - 오늘 아카이브 - IA-32 구현 - 인텔 P6

- ^ Schnurer, Georg. "Next Exit: Mendocino". Archived from the original on February 19, 2006. Retrieved April 24, 2009.

- ^ Shanley, Tom (1998). Pentium Pro and Pentium II System Architecture. Addison-Wesley Professional. p. 199. ISBN 978-0-201-30973-7.

- ^ Guruge, Anura (May 17, 2000). Web-to-Host Connectivity. CRC Press. p. 405. ISBN 978-0-203-99747-5.

- ^ a b c d e f Hardenberg, Hal W. (June 1, 1997). "Back to the Futurebus". drdobbs.com. Dr. Dobb's Journal. Retrieved September 19, 2020.

외부 링크

- 백사이드 버스, 창고를 수색해techtarget.com

- 인텔 Pentium Pro 이미지와 설명, cpu-collection.데

- CPU-INFO: 인텔 Pentium Pro, 프로세서 이력, web.archive.org