깊은 반응 이온 식각

Deep reactive-ion etchingDeep reactive-ion etching(DRIE)은 웨이퍼/기판에 깊은 침투, 가파른 측면 구멍 및 참호를 생성하기 위해 사용되는 매우 비등방성 에치 공정으로, 일반적으로 높은 가로 세로 비율을 가지고 있다. 이러한 기능이 필요한 미세전자기계시스템(MEMS)을 위해 개발됐지만 D램용 고밀도 캐패시터용 참호를 발굴하는 데도 활용되고 있으며 최근에는 3D 웨이퍼 레벨 패키징 기술에서 실리콘 비아(TSV)를 통한 생성을 위한 참호 발굴에도 활용되고 있다. DRIE에서는 기질이 원자로 내부에 위치하며 여러 기체가 유입된다. 플라즈마는 가스 혼합물에 부딪혀 가스 분자를 이온으로 분해한다. 이온들은 에칭되는 물질의 표면을 향해 가속되었고, 또 다른 기체 원소를 형성하면서 반응한다. 이것은 반응성 이온 식각의 화학적 부분으로 알려져 있다. 물리적인 부분도 있는데, 이온이 충분한 에너지를 가지고 있다면 화학반응 없이 식각될 물질에서 원자를 때려낼 수 있다.

DRIE는 RIE의 특별한 하위 클래스다.

고율 DRIE에는 극저온과 Bosch의 두 가지 주요 기술이 있지만, Bosch 공정만이 인정된 생산 기법이다. 보쉬 공정과 크라이오 공정 모두 90°(진정한 수직) 벽을 제작할 수 있지만, 88°("반복") 또는 92°("반복")와 같이 벽이 약간 테이퍼 처리되는 경우가 많다.

또 다른 메커니즘은 sidewall passivation이다: SiOFxy 기능 그룹(황황 헥사플루오라이드와 산소 에치 가스에서 유래)은 sidewall에서 응축되며, 그들을 측면 에칭으로부터 보호한다. 이러한 프로세스의 조합으로 깊은 수직 구조를 만들 수 있다.

극저온 공정

극저온-DRIE의 경우 웨이퍼가 -110°C(163K)로 냉각된다. 낮은 온도는 등방성 식각을 생성하는 화학반응을 늦춘다. 그러나 이온은 계속해서 위쪽을 향한 표면을 폭격하고 식각한다. 이 과정은 매우 수직적인 측면벽으로 참호를 만든다. 크라이오-DRIE의 주요 문제는 기판 위의 표준 마스크가 극한의 추위 속에서 갈라지고, 에치 부산물이 가장 가까운 차가운 표면, 즉 기판이나 전극에 침전되는 경향이 있다는 것이다.

보쉬 공정

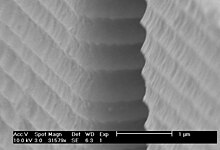

펄스 또는 시간 다중 에칭으로 알려진 [1][2][3]이 공정을 특허를 받은 독일 회사인 Robert Bosch GmbH의 이름을 딴 Bosch 공정은 거의 수직 구조를 달성하기 위해 두 가지 모드 사이를 반복적으로 교대한다.

- 거의 등방성에 가까운 표준 혈장 에치. 플라즈마에는 거의 수직 방향으로 웨이퍼를 공격하는 이온 몇 개가 들어 있다. 실리콘에는 육불화황[SF]6이 많이 사용된다.

- 화학적으로 불활성 수용층의 증착. (예를 들어 옥타플루오로클로부탄[CF48] 선원 가스는 테플론과 유사한 물질을 산출한다.)

각 국면은 몇 초 동안 지속된다. 패시브레이어 층은 더 이상의 화학적 공격으로부터 기질 전체를 보호하고 더 이상의 에칭화를 방지한다. 그러나 식각 단계에서는 기질을 폭격하는 방향 이온이 참호 밑바닥의 패시브 층(그러나 측면을 따라 공격하지는 않는다)을 공격한다. 그들은 그것과 충돌하여 그것을 가래로 튀겨서 기질을 화학 식각제에 노출시킨다.

이러한 에치/예금 단계는 여러 번 반복되어 에치된 구덩이 바닥에서만 많은 수의 매우 작은 등방성 에치 단계가 이루어진다. 예를 들어 0.5mm 실리콘 웨이퍼를 통해 식각하려면 100–1000 에치/예금 단계가 필요하다. 2상 공정은 약 100–500 nm의 진폭으로 sidewall이 풀리게 한다. 사이클 시간은 조절할 수 있다: 짧은 사이클은 벽을 부드럽게 하고, 긴 사이클은 에치 속도를 높인다.

적용들

RIE "깊이"는 응용 프로그램에 따라 달라진다.

- DRAM 메모리 회로에서 캐패시터 참호 깊이는 10~20µm일 수 있으며,

- MEMS에서 DRIE는 몇 마이크로미터에서 0.5mm까지의 모든 것에 사용된다.

- 불규칙 칩 다이싱에서 DRIE는 새로운 하이브리드 소프트/하드 마스크와 함께 사용되어 실리콘 다이스를 주사하기 위한 밀리미터 이하의 에칭이 불규칙한 모양의 레고 조각으로 만들어진다.[4][5][6]

- DRIE는 실리콘 기판의 두께를 극소수에서 수십 마이크로미터로 줄여 기존의 단일형 CMOS 기기를 유연하게 만드는 데 사용된다.[7][8][9][10][11][12]

DRIE와 RIE를 구별하는 것은 엣치 깊이: RIE에 대한 실용적인 에치 깊이는 최대 1µm/min의 속도로 약 10µm로 제한될 수 있는 반면, DRIE는 일부 용도에서는 최대 20µm/min 이상의 속도에 훨씬 더 큰 600µm 이상의 특징을 가질 수 있다.

유리의 DRIE는 높은 플라즈마 파워를 필요로 하기 때문에 진정 깊은 에칭에 적합한 마스크 소재를 찾기 어렵다. 폴리실리콘과 니켈은 10-50µm 에칭된 깊이에 사용된다. 폴리머의 DRIE에서는 SF6 에칭과 CF48 패시브 스텝을 번갈아 밟는 Bosch 공정이 이루어진다. 금속 마스크는 사용할 수 있지만, 항상 여러 장의 추가 사진과 증착 단계가 필요하기 때문에 사용하기에는 비용이 많이 든다. 그러나 금속 마스크는 화학적으로 증폭된 음극 저항기를 사용하는 경우 다양한 기판(Si [800µm까지], InP[40µm까지] 또는 유리[12µm까지]에는 필요하지 않다.

갈륨 이온 이온 이식은 크라이오-DRIE에서 에치 마스크로 사용할 수 있으며, 집중 이온 빔과 크라이오-DRIE의 결합 나노 압착 과정은 N 체쿠로프 외 연구진이 '국소 갈륨 이온 이식 및 극저온 반응 이온 에칭에 의한 실리콘 나노구조 제작' 기사에서 처음 보고했다.[13]

정밀기계

DRIE는 실리콘 기계 부품을 고급 손목시계에 사용할 수 있도록 했다. 까르띠에의 한 엔지니어에 따르면, "DRIE로 기하학적 모양에는 한계가 없다"[14]고 한다. DRIE를 사용하면 30 이상의 가로 세로 비율을 얻을 수 있으며 이는 [15]표면이 폭보다 30배 더 깊은 수직 벽면 참호로 식각될 수 있다는 것을 의미한다.

이를 통해 실리콘 부품은 헤어스프링과 같이 보통 강철로 만들어진 일부 부품으로 대체될 수 있게 되었다. 실리콘은 철강에 비해 가볍고 단단해 장점을 지녔지만 제조 공정이 더 까다롭다.

참조

- ^ 기본 Bosch 공정 특허출원

- ^ 개선된 Bosch 공정 특허 출원

- ^ Bosch 공정 "매개 변수 램프링" 특허 출원

- ^ Ghoneim, Mohamed; Hussain, Muhammad (1 February 2017). "Highly Manufacturable Deep (Sub-Millimeter) Etching Enabled High Aspect Ratio Complex Geometry Lego-Like Silicon Electronics" (PDF). Small. 13 (16): 1601801. doi:10.1002/smll.201601801. hdl:10754/622865. PMID 28145623.

- ^ Mendis, Lakshini (14 February 2017). "Lego-like Electronics". Nature Middle East. doi:10.1038/nmiddleeast.2017.34.

- ^ Berger, Michael (6 February 2017). "Lego like silicon electronics fabricated with hybrid etching masks". Nanowerk.

- ^ Ghoneim, Mohamed; Alfaraj, Nasir; Torres-Sevilla, Galo; Fahad, Hossain; Hussain, Muhammad (July 2016). "Out-of-Plane Strain Effects on Physically Flexible FinFET CMOS". IEEE Transactions on Electron Devices. 63 (7): 2657–2664. Bibcode:2016ITED...63.2657G. doi:10.1109/ted.2016.2561239. hdl:10754/610712. S2CID 26592108.

- ^ Ghoneim, Mohamed T.; Hussain, Muhammad M. (23 July 2015). "Review on physically flexible nonvolatile memory for internet of everything electronics". Electronics. 4 (3): 424–479. arXiv:1606.08404. doi:10.3390/electronics4030424. S2CID 666307.

- ^ Ghoneim, Mohamed T.; Hussain, Muhammad M. (3 August 2015). "Study of harsh environment operation of flexible ferroelectric memory integrated with PZT and silicon fabric" (PDF). Applied Physics Letters. 107 (5): 052904. Bibcode:2015ApPhL.107e2904G. doi:10.1063/1.4927913. hdl:10754/565819.

- ^ Ghoneim, Mohamed T.; Rojas, Jhonathan P.; Young, Chadwin D.; Bersuker, Gennadi; Hussain, Muhammad M. (26 November 2014). "Electrical Analysis of High Dielectric Constant Insulator and Metal Gate Metal Oxide Semiconductor Capacitors on Flexible Bulk Mono-Crystalline Silicon". IEEE Transactions on Reliability. 64 (2): 579–585. doi:10.1109/TR.2014.2371054. S2CID 11483790.

- ^ Ghoneim, Mohamed T.; Zidan, Mohammed A.; Alnassar, Mohammed Y.; Hanna, Amir N.; Kosel, Jurgen; Salama, Khaled N.; Hussain, Muhammad (15 June 2015). "Flexible Electronics: Thin PZT-Based Ferroelectric Capacitors on Flexible Silicon for Nonvolatile Memory Applications". Advanced Electronic Materials. 1 (6): 1500045. doi:10.1002/aelm.201500045.

- ^ Ghoneim, Mohamed T.; Kutbee, Arwa; Ghodsi, Farzan; Bersuker, G.; Hussain, Muhammad M. (9 June 2014). "Mechanical anomaly impact on metal-oxide-semiconductor capacitors on flexible silicon fabric" (PDF). Applied Physics Letters. 104 (23): 234104. Bibcode:2014ApPhL.104w4104G. doi:10.1063/1.4882647. hdl:10754/552155.

- ^ Chekurov, N; Grigoras, K; et al. (11 February 2009). "The fabrication of silicon nanostructures by local gallium implantation and cryogenic deep reactive ion etching". Nanotechnology. 20 (6): 065307. doi:10.1088/0957-4484/20/6/065307. PMID 19417383.

- ^ Kolesnikov-Jessop, Sonia (23 November 2012). "Precise Future of Silicon Parts Still Being Debated". The New York Times. New York.

- ^ Yeom, Junghoon; Wu, Yan; Selby, John C.; Shannon, Mark A. (2005). "Maximum achievable aspect ratio in deep reactive ion etching of silicon due to aspect ratio dependent transport and the microloading effect". Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures. American Vacuum Society. 23 (6): 2319. Bibcode:2005JVSTB..23.2319Y. doi:10.1116/1.2101678. ISSN 0734-211X.