하이퍼SPARC

hyperSPARC| 일반 정보 | |

|---|---|

| 시작됨 | 1993 |

| 단종. | 1996 |

| 설계자 | 로스 테크놀로지 |

| 퍼포먼스 | |

| 최대 CPU 클럭 속도 | 40MHz ~ 200MHz |

| 건축과 분류 | |

| 명령 집합 | SPARC V8 |

| 물리적 사양 | |

| 코어스 |

|

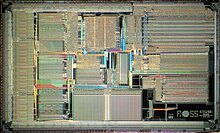

코드명 '피너클'인 하이퍼SPARC는 사이프러스 반도체용 로스테크놀로지가 개발한 SPARC Version 8 명령 집합 아키텍처(ISA)를 구현한 마이크로프로세서다.

하이퍼SPARC는 1993년에 도입되었으며, Sun Microsystems SuperSPARC와 경쟁하였다. 라주 베게스나는 마이크로아키텍처였다. 하이퍼SPARC는 1990년대 중반 Sun Microsystem의 주요 경쟁사였다. 후지쓰가 사이프레스로부터 로스를 인수했을 때, 역시 후지쓰 자회사인 HAL Computer Systems가 개발한 SPARC64보다 하이퍼SPARC가 새 소유주에게 더 중요한 것으로 여겨져 애널리스트들과 의견을 같이 했다.

설명

하이퍼SPARC는 양방향 슈퍼칼라 마이크로프로세서였다. 실행 단위는 정수 단위, 부동 소수점 단위, 부하/저장 단위, 분기 단위 등 4개였다. 하이퍼SPARC에는 8KB 명령 캐시가 있으며, 이 캐시로부터 사이클당 두 개의 명령이 가져와 디코딩되었다. 이전에 해독된 명령이 실행부서에 발행되지 않은 경우 디코더는 새로운 명령을 해독할 수 없었다.

정수 레지스터 파일에는 136개의 레지스터가 포함되어 SPARC ISA에 정의된 기능인 8개의 레지스터 창을 제공한다. 그곳에는 두 개의 읽기 포트가 있었다. 정수 단위는 4단 파이프라인이 있었고, 그 중 2단계가 추가되어 파이프라인이 모든 비부동점 파이프라인과 같을 것이다. SPARC 아키텍처의 V8 버전에 추가된 명령인 정수 곱하기 및 나누기는 각각 18 사이클과 37 사이클의 지연 시간을 가지며, 파이프라인이 완료될 때까지 파이프라인을 정지시켰다.

마이크로프로세서는 MBus 시스템에서 멀티프로세싱을 지원했다.

물리적인

하이퍼SPARC는 120만 개의 트랜지스터로 구성되어 있다. 사이프러스가 0.65 µm의 2층 금속, 보완 금속-산화물-반도체(CMOS) 공정에서 제작했다. 이후 하이퍼SPARC의 반복은 새로운 기능으로 인해 더 많은 트랜지스터를 가지고 있으며, 새로운 프로세스에 포팅되었다. NEC가 조작한 마지막 반복을 제외하고 후지쓰가 조작한 것이다.

포장

하이퍼SPARC는 멀티 칩 설계였다. PGA(핀 그리드 어레이)가 탑재된 세라믹 멀티칩 모듈(MCM)에 포장됐다.

칩셋

하이퍼SPARC는 1992년 7월 말에 도입된 사이프러스 스파르크셋 칩셋을 사용했다. 디자인을 조작한 사이프레스(Cypress)를 위해 캘리포니아주 창업기업 님버스 테크놀로지스(Santa Clara, Inc. SparcSet는 다른 SPARC 마이크로프로세서와도 호환이 가능했다.

참조

- 레빈, 버나드(1994년 4월 11일) "MCM 옹호자들은 예비 사용자를 유혹한다." 일렉트로닉 뉴스.

- 홀든, 다니엘 (1993년 2월 15일) "Cypress, Sun: HyperSPARC 고혈압" 일렉트로닉 뉴스.

- 홀든, 다니엘 (1993년 3월 15일) "HyperSparc 아이즈는 P6 프로세서에서 인텔과 결합한다." 일렉트로닉 뉴스.

- 홀든, 다니엘 (1993년 4월 19일) "HyperSPARC는 Sun Micro와 함께 느리게 간다." 일렉트로닉 뉴스.

- 심, 존 폴, 리파스티, 미코 H. (2004) 현대 프로세서 설계. 맥그로힐 프로페셔널

추가 읽기

- "Ros Previews Pinnacle SPARC Design" (1992년 3월 25일) 마이크로프로세서 보고서, 제6권, 제4권.

- "TI와 사이프레스/SARC 리더십을 위한 크로스 배틀" (1992년 5월 27일) 마이크로프로세서 보고서, 제6권, 제7호.

- "Ross Neually Ships HyperSPARC" (1993년 11월 15일) 마이크로프로세서 보고서, 제7권, 제15호.

- "향상된 HyperSparc Challenges UltraSparc."(1995년 12월 4일) 마이크로프로세서 보고서, 제9권, 제16호.