병렬 처리(DSP 구현)

Parallel processing (DSP implementation)디지털 신호 처리(DSP)에서 병렬 처리는 여러 작업(신호)을 동시에 운용하기 위해 기능 단위를 복제하는 기법이다.[1]따라서, 우리는 해당 중복된 기능 유닛의 서로 다른 신호에 대해 동일한 처리를 수행할 수 있다.또한 병렬 처리의 특징 때문에 병렬 DSP 설계에는 다수의 출력이 포함되어 있지 않은 경우보다 처리량이 더 높은 경우가 많다.null

개념적 예

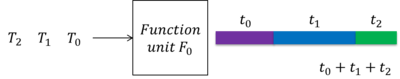

기능 단위( 0 와 세 가지 과제( T 기능 단위 F t {\displaystyle t_{ 그리고 t 2 2}}, 이러한 작업을 처리하는 데 필요한 시간은 t displaystystyle t_{이다그런 다음 이 세 가지 작업을 순차적으로 운영하면, 완료에 필요한 시간은 + +

그러나 기능 단위를 다른 두 개의 복사본({\F} )에 복제하면 집계 이 ( 0 1 , ){\로 줄었는데 순차적인 순서보다 작다.null

파이프라인 대 파이프라인

메커니즘:

- 병렬: 병렬로 작동하는 중복 기능 유닛

- 각각의 업무는 완전히 다른 기능 단위에 의해 처리된다.

- 파이프라이닝: 병렬로 작동하는 다른 기능 유닛

- 각각의 업무는 전문적이고 다른 기능 단위로 처리되는 일련의 하위 업무로 나뉜다.

목표:

- 파이프라이닝은 임계 경로의 감소로 이어져 동일한 속도로 샘플링 속도를 높이거나 전력 소비량을 감소시켜 와트당 더 높은 성능을 산출할 수 있다.

- 병렬 처리 기법에는 다수의 출력이 필요하며, 이 출력은 클럭 기간 동안 병렬로 계산된다.따라서 유효 샘플링 속도는 병렬 수준에 따라 증가한다.

병렬 처리 기법과 파이프라인 기법을 모두 적용할 수 있는 조건을 고려하십시오. 다음과 같은 이유로 병렬 처리 기법을 선택하는 것이 더 낫다.

- 일반적으로 파이프라인으로 인해 I/O 병목 현상이 발생함

- 슬로우 클럭을 사용하면서 전력 소비량을 줄이는 데도 병렬 프로세싱이 활용된다.

- 파이프라이닝과 병렬 프로세싱의 복합적인 방법은 아키텍처의 속도를 더욱 증가시킨다.

병렬 FIR 필터

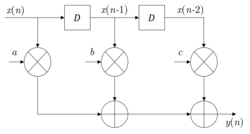

3탭 FIR 필터를 고려하십시오.[2]

다음 그림에 표시된 바와 같다.null

곱셈 단위에 대한 계산 시간은 추가 단위에 대한m T와a T라고 가정한다.샘플링 주기는 다음과 같다.

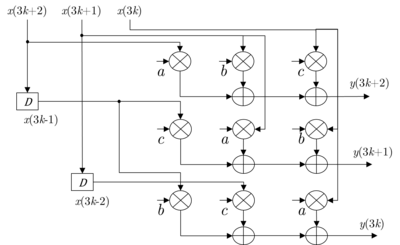

그것을 병렬화함으로써, 결과적 아키텍처는 다음과 같이 나타난다.샘플링 속도는 이제

여기서 N은 사본 수를 나타낸다.null

병렬 에서는 샘플 T = T 에 유의하십시오.은(는) 파이프라인 시스템에 고정되어 있다.null

병렬 1차 IIR 필터

다음과 같이 공식화된 1차 IIR 필터의 전송 기능을 고려하십시오.

안정성에 대한 1 1 및 그러한 필터는 z = a에 하나의 폴만 위치하는 경우;

해당 재귀적 표현은

4-병렬 아키텍처(N = 4)의 설계를 고려하십시오.이러한 병렬 시스템에서 각 지연 요소는 블록 지연을 의미하며 클럭 주기는 샘플링 주기의 4배이다.null

따라서 n = 4k로 반복함으로써 우리는

해당 아키텍처는 다음과 같이 표시된다.null

결과 병렬 설계에는 다음과 같은 특성이 있다.null

- 원래 필터의 폴은 z = a이고, 병렬 시스템의 폴은 z = a이며4, 이는 원점에 더 가깝다.

- 극의 움직임은 시스템의 강건성을 반올림 소음까지 개선한다.

- 이 아키텍처의 하드웨어 복잡성:N×N 다중 추가 작업.

하드웨어 복잡성의 제곱 증가는 동시성과 증분 계산을 활용하여 반복적인 컴퓨팅을 방지함으로써 줄일 수 있다.null

저전력을 위한 병렬 처리

병렬 처리 기법의 또 다른 장점은 공급 전압을 줄임으로써 시스템의 전력 소비를 줄일 수 있다는 것이다.null

일반 CMOS 회로에서 다음과 같은 전력 소비량을 고려하십시오.null

여기서 C는total CMOS 회로의 총 캐패시턴스를 나타낸다.null

병렬 버전의 경우 충전 캐패시턴스는 그대로 유지되지만 총 캐패시턴스는 N배 증가한다.null

동일한 샘플링 속도를 유지하기 위해 N-병렬 회로의 클럭 주기가 원래 회로의 전파 지연의 N배까지 증가한다.null

충전 시간이 N번 연장되도록 한다.공급 전압은 βV로0 줄일 수 있다.null

따라서 N-병렬 시스템의 전력 소비량은 다음과 같이 공식화할 수 있다.

여기서 β는 다음을 통해 계산될 수 있다.

참조

- ^ K. K. Parhi, VLSI 디지털 신호 처리 시스템:1999년 John Wiley, 설계 및 구현

- ^ VLSI 디지털 신호 처리 시스템용 슬라이드:설계 및 구현 John Wiley & Sons, 1999(ISBN 번호: 0-471-24186-5): http://people.ece.umn.edu/~parhi/pari/properties/books/