루트 콤플렉스

Root complex

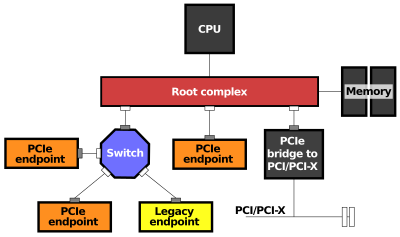

PCIe(PCIe) 시스템에서 루트 복합 디바이스는 CPU 및 메모리 서브시스템을 하나 이상의 PCIe 또는 PCI 디바이스로 구성된 PCI Express 스위치 패브릭에 연결합니다.

PCI [2]시스템의 호스트 브리지와 마찬가지로 루트 복합체는 로컬 버스를 통해 상호 연결된 CPU를 대신하여 트랜잭션 요청을 생성합니다.루트 콤플렉스 기능은 칩셋 및/또는 CPU에 통합될 수 있습니다.루트 콤플렉스에는 여러 PCI Express 포트를 포함할 수 있으며 루트 콤플렉스 또는 캐스케이드 [3]포트에는 여러 스위치 디바이스를 연결할 수 있습니다.

디바이스 메모리 맵

PCIE 루트 콤플렉스에는 각 엔드포인트 장치에서 액세스할 수 있는 호스트 메모리 공간을 정의하는 '타입 1 구성 테이블'의 마스터 복사본이 있습니다.또, 각 PCIE 엔드 포인트 디바이스는, 호스트 시스템 메모리내의 메모리 스페이스 맵의 마스터 카피를 「Type 0 Configuration Table」로서 보관 유지합니다.각 디바이스의 이 구성 테이블에서는, 호스트가 PCIe 디바이스의 로컬 메모리에 액세스 할 수 있습니다.타입 1 및 타입0 설정 테이블은 모두 호스트오퍼레이팅시스템에 의해 설정됩니다.호스트 오퍼레이팅시스템은 열거라고 불리는 프로세스에 의해 루트콤플렉스를 제어하고 각 브리지와 버스네트워크에 접속되어 있는 엔드포인트디바이스에 문의함으로써 시스템의 디바이스 메모리 맵을 구축합니다.마찬가지로 PCIE 브릿지는 "Type 0 Configuration Table"을 사용하여 계층화된 루트 콤플렉스를 수행합니다.

레퍼런스

- ^ Richard Solomon (2015-06-17). "PCI Express Basics and Background" (PDF). PCI-SIG. p. 26. Retrieved 2016-04-12.

- ^ "Bus Specifics (Writing Device Drivers)". docs.oracle.com. Retrieved 2020-11-14.

- ^ "Choosing the Right Programmable Logic Solution for PCI Express Applications". Archived from the original on 21 February 2011. Retrieved 31 March 2010.