트레이스 캐시

Trace cache컴퓨터 아키텍처에서 트레이스 캐시 또는 실행 트레이스 캐시는 트레이스로 알려진 명령의 동적 스트림을 저장하는 특수한 명령 캐시입니다.이미 Import 및 [1]디코딩된 명령의 트레이스를 저장함으로써 명령 페치 대역폭을 늘리고 전력 소비량(인텔 Pentium 4의 경우)을 줄이는 데 도움이 됩니다.트레이스[2] 프로세서는 트레이스 캐시를 중심으로 설계된 아키텍처로 트레이스 수준의 세밀도로 명령을 처리합니다.트레이스의 형식적인 수학 이론은 트레이스 모노이드에 의해 설명됩니다.

배경

트레이스 캐시에 관한 최초의 학술 간행물은 "Trace Cache: 고대역폭 명령 페칭에 대한 낮은 지연 접근법"[1]이었습니다.이 널리 알려진 논문은 Eric Rottenberg, Steve Bennett 및 Jim Smith가 1996년 마이크로아키텍처(MICRO) 국제 심포지엄에서 발표한 것입니다.이전에 발표된 것은 인텔의 Alex Peleg와 Uri Weiser에 의한 미국 특허 5381533으로,[3] "가상 주소 라인에 의존하지 않는 트레이스 세그먼트를 중심으로 구성된 동적 흐름 명령 캐시 메모리"는 1992년에 제출된 애플리케이션의 계속이지만 나중에 포기되었습니다.

필요성

더 넓은 슈퍼스칼라 프로세서는 성능을 높이기 위해 한 사이클에 여러 명령을 가져와야 합니다.브랜치 명령과 점프 명령이 있기 때문에 가져오는 명령이 항상 인접한 메모리 위치(기본 블록)에 있는 것은 아닙니다.따라서 프로세서는 인접하지 않은 기본 블록에서 이러한 명령을 가져와 정렬하기 위해 추가적인 로직 및 하드웨어 지원이 필요합니다.여러 분기가 취득되지 않은 것으로 예측되는 경우 프로세서는 하나의 사이클로 여러 개의 연속된 기본 블록에서 명령을 가져올 수 있습니다.단, 브런치 중 하나가 취득된 것으로 예측되는 경우 프로세서는 같은 사이클로 취득된 경로에서 명령을 가져옵니다.이것에 의해, 프로세서의 취득 기능이 제한됩니다.

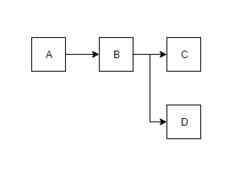

이러한 4개의 기본 블록에 대해 생각해 봅시다(A,B,C,D)는 단순한 if-sign 루프에 대응하는 그림에 나타나 있습니다.이러한 블록은 다음과 같이 인접하여 저장됩니다.ABCD기억 속에.브런치가Dfetch 유닛은 기본 블록을 가져올 수 있습니다.A,B,C인접하게 배치되어 있습니다.단, 만약D예측된 경우, fetch 유닛은 fetch를 해야 합니다.A,B,D비접촉적으로 배치되어 있습니다.따라서 인접하지 않은 블록을 한 사이클로 가져오는 것은 매우 어렵습니다.따라서 이러한 트레이스 캐시는 프로세서에 도움이 됩니다.

가져오면 트레이스 캐시는 명령어를 다이내믹시퀀스로 저장합니다.이러한 명령어가 다시 발견되면 트레이스 캐시를 통해 프로세서의 명령어페치 유닛은 실행 흐름의 브랜치에 대해 걱정할 필요 없이 프로세서에서 여러 기본 블록을 가져올 수 있습니다.명령은 디코딩된 후 또는 폐기될 때 트레이스 캐시에 저장됩니다.그러나 명령 시퀀스는 디코딩 단계 직후에 저장될 경우 추측성이 있습니다.

트레이스 구조

트레이스는 동적 명령 시퀀스라고도 하며 트레이스 캐시 내의 엔트리입니다.이는 최대 명령 수와 최대 기본 블록 수로 특징지을 수 있습니다.트레이스는 임의의 동적 명령으로 시작할 수 있습니다.복수의 트레이스는, 같은 개시 명령, 즉 같은 개시 프로그램 카운터(PC)와 브랜치 결과에 따라서 다른 기본 블록으로부터의 명령을 가질 수 있습니다.위의 그림에서 ABC와 ABD는 유효한 트레이스입니다.둘 다 같은 PC(A의 주소)에서 시작하여 D의 예측대로 기본 블록이 다릅니다.

트레이스는 보통 다음 중 하나가 발생했을 때 종료됩니다.

- 트레이스가 허용 가능한 최대 명령 수로 채워졌습니다.

- 추적에 허용되는 최대 기본 블록이 있습니다.

- 반품 절차

- 간접 분기

- 시스템 콜

트레이스 제어 정보

단일 트레이스에는 다음 정보가 포함됩니다.

- PC 부팅 - 트레이스 내 첫 번째 명령 PC

- 분기 플래그 - (최대 기본 블록 -1) 분기 예측

- Branch mask - 트레이스 내의 브랜치 수 및 트레이스가 브랜치 마스크

- 트레이스 폴 스루 - 마지막 명령이 브랜치 또는 브랜치가 아닌 경우 다음 PC

- 추적 대상 - 마지막 분기에서 가져온 대상의 주소

트레이스 캐시 설계

다음으로 트레이스 캐시를 설계할 때 고려해야 할 요소를 나타냅니다.

- 추적 선택 정책 - 추적의 최대 명령 수와 최대 기본 블록 수

- 연관성 - 캐시가 가질 수 있는 방법 수

- 캐시 인덱싱 방식 - PC 비트와 연결 또는 XOR

- Path Associativity - 시작 PC는 같지만 기본 블록이 다른 트레이스를 다른 세트에 매핑할 수 있습니다.

- 추적 캐시 채우기 선택 항목 -

- 디코딩 단계 후(추측)

- 은퇴 후 단계

추적[4] 캐시가 명령 가져오기의 중요한 경로에 없습니다.

히트/미스 로직

트레이스 라인은 트레이스 내 첫 번째 명령의 PC와 분기 예측 세트를 기반으로 트레이스 캐시에 저장됩니다.이를 통해 동일한 주소에서 시작하는 서로 다른 트레이스 경로를 저장할 수 있으며 각각 다른 분기 결과를 나타냅니다.이 태그 지정 방법은 트레이스 캐시에 대한 경로 연관성을 제공하는 데 도움이 됩니다.다른 방법으로는 트레이스 캐시 내의 태그로서 PC를 기동하는 것만을 포함할 수 있습니다.파이프라인의 명령 페치 단계에서는 현재 PC와 분기 예측 세트를 트레이스 캐시에서 히트 여부를 체크한다.히트가 발생하면 트레이스 라인이 일반 캐시나 이러한 명령을 위해 메모리에 갈 필요가 없는 페치 유닛에 공급됩니다.트레이스 캐시는 트레이스 회선이 종료되거나 파이프라인에 오답이 있을 때까지 페치 유닛을 계속 공급합니다.오류가 발생하면 새 트레이스가 구축되기 시작합니다.

Pentium 4의 실행 트레이스 캐시는 x86 명령 디코딩에 따른 마이크로 오퍼레이션을 저장하며 마이크로 오퍼레이션 캐시의 기능도 제공합니다.이렇게 하면 다음 번에 명령이 필요할 때 [5]다시 마이크로 ops로 디코딩할 필요가 없습니다.

단점들

트레이스 캐시의 단점은 다음과 같습니다.

실행 트레이스 캐시

NetBurst CPU의 L1 캐시에는 인텔의 실행 트레이스 [7][8]캐시가 포함되어 있습니다.디코딩된 마이크로 연산을 저장하기 때문에 새로운 명령을 실행할 때 명령을 다시 가져오고 디코딩하는 대신 CPU가 트레이스 캐시에서 디코딩된 마이크로 ops에 직접 액세스하여 상당한 시간을 절약할 수 있습니다.또한 micro-ops는 예측된 실행 경로에 캐시됩니다.즉, CPU가 캐시에서 명령을 가져올 때 명령이 이미 올바른 실행 순서로 존재함을 의미합니다.이후 인텔은 Sandy Bridge에서 마이크로 오퍼레이션 캐시(UOP 캐시)라고 불리는 유사하지만 단순한 개념을 도입했습니다.

「 」를 참조해 주세요.

레퍼런스

- ^ a b Rotenberg, Eric; Bennett, Steve; Smith, James E.; Rotenberg, Eric (1996-01-01). "Trace Cache: a Low Latency Approach to High Bandwidth Instruction Fetching". In Proceedings of the 29th International Symposium on Microarchitecture: 24–34.

- ^ 에릭 로텐버그, 퀸 제이콥슨, 얀나키스 사제이데스, 제임스 E.스미스, 트레이스 프로세서입니다제30회 마이크로아키텍처 국제심포지엄(MICRO-30), 138-148페이지, 1997년 12월

- ^ Peleg, Alexander; Weiser, Uri (Jan 10, 1995), Dynamic flow instruction cache memory organized around trace segments independent of virtual address line, retrieved 2016-10-18

- ^ a b Leon Gu; Dipti Motiani (2003년 10월).「Trace Cache」(PDF).2013-10-06을 취득했습니다.

- ^ Agner 안개(2014-02-19)."인텔, AMD 및 VIA CPU의 마이크로 아키텍처: 어셈블리 프로그래머 및 컴파일러 제조사를 위한 최적화 가이드" (PDF). agner.org2014-03-21 취득.

- ^ Co, Michele. "Trace Cache". www.cs.virginia.edu. Retrieved 2016-10-21.

- ^ Carmean, Doug (Spring 2002). "The Intel® Pentium® 4 Processor" (PDF). Archived from the original (PDF) on 19 April 2018.[어쩔 수 없는 소스?]

- ^ "Archived copy". www.xbitlabs.com. Archived from the original on 6 March 2016. Retrieved 12 January 2022.

{{cite web}}: CS1 maint: 제목으로 아카이브된 복사(링크)