삼국논리

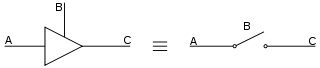

Three-state logic디지털 전자제품에서는 3스테이트, 3스테이트 또는 3스테이트 로직으로 출력 또는 입력 핀/패드가 고임피던스 상태를 가정할 수 있으며, 0 및 1 로직 레벨에 가세해 회로로부터의 출력을 효과적으로 삭제할 수 있습니다.

이것에 의해, 복수의 회선이 같은 출력 회선(한 번에 복수의 디바이스를 수신할 수 없는 버스등)을 공유할 수 있습니다.

3 스테이트 출력은, 7400 및 4000 시리즈의 많은 레지스터, 버스 드라이버, 플립 플랍, 및 그 외의 타입에 실장되어 있습니다만, 내부적으로는 많은 집적 회로에 실장되어 있습니다.다른 일반적인 용도로는 마이크로프로세서, 컴퓨터 메모리 및 주변기기의 내장 및 외장 버스가 있습니다.많은 디바이스는 출력을 높은 임피던스 상태로 유지할지 또는 각각의 부하를 구동할지(0레벨 또는 1레벨로)를 지시하는 OE(Output Enable)라고 불리는 액티브 로우 입력에 의해 제어됩니다.

3가지[1][citation needed] 상태라는 용어는 3진 논리(3-값 논리)와 혼동해서는 안 됩니다.

| 입력 | 산출량 | |

|---|---|---|

| A | B | C |

| 0 | 0 | Z(고임피던스) |

| 1 | Z(고임피던스) | |

| 0 | 1 | 0 |

| 1 | 1 | |

사용하다

세 번째 상태의 기본 개념인 고임피던스(Hi-Z)는 회로의 나머지 부분으로부터 디바이스의 영향을 효과적으로 제거하는 것입니다.복수의 디바이스가 다른 디바이스에 전기적으로 접속되어 있는 경우, 출력을 Hi-Z 상태로 하는 것은, 단락을 방지하기 위해서, 또는 로우(논리 0)를 주행하는 다른 디바이스에 대해서 하이(논리 1)를 주행하는 것을 막기 위해서 자주 사용됩니다.

3 스테이트 버퍼는,[2] 특히 입력수가 많은 멀티플렉서를 실장하기 위해서도 사용할 수 있습니다.

3 스테이트 버퍼는, 공유 전자 버스의 동작에 불가결합니다.

3스테이트 로직을 사용하면 LED 세트를 구동하는 데 필요한 와이어 수를 줄일 수 있습니다(트리스테이트 멀티플렉싱 또는 찰리플렉싱).

출력 활성화와 칩 선택

버스에 접속하도록 설계된 메모리 디바이스(RAM이나 ROM 칩 등)의 대부분은 CS(칩 셀렉트) 핀과 OE(출력 유효) 핀을 모두 갖추고 있습니다.이 핀은 표면적으로는 같은 것으로 보입니다.CS가 단언되지 않은 경우 출력은 고임피던스입니다.

차이는 신호 출력에 필요한 시간에 있습니다.칩 선택이 해제되면 칩은 내부적으로 동작하지 않으며 주소 제공과 데이터 수신 사이에 상당한 지연이 발생합니다(물론 이 경우 칩의 소비전력이 최소화된다는 장점이 있습니다).

칩 선택이 아사트되면 칩은 내부적으로 액세스를 실행하고 최종 출력 드라이버만 아사트 해제하여 비활성화합니다.이는 버스가 다른 용도로 사용되는 동안 수행할 수 있으며, 출력 활성화가 최종적으로 단언되면 데이터는 최소 지연으로 표시됩니다.ROM 또는 스태틱 RAM 칩에 출력 유효 회선이 있는 경우는, 통상, 2개의 액세스 시간이 표시됩니다.하나는 칩 셀렉트로부터의 액세스 시간과 주소 유효 시간이며, 다른 하나는 출력 유효 회선으로부터의 액세스 시간이며, 다른 하나는 출력 유효 회선에서의 액세스 시간입니다.

풀업 및 풀다운 사용

출력이 트라이스테이트(Hi-Z 상태)되면 나머지 회로에 미치는 영향이 제거되고 다른 회로 소자가 상태를 결정하지 않으면 회로 노드가 "부동" 상태가 됩니다.회로 설계자는 종종 풀업 또는 풀다운 저항(보통 1~100kΩ 범위)을 사용하여 출력이 트라이스테이트될 때 회로에 영향을 줍니다.

PCI 로컬버스는 풀업 저항을 제공하지만 버스의 대용량 분산 캐패시턴스를 고려하여 신호를 높은 수준으로 끌어오려면 몇 번의 클럭 사이클이 필요합니다.고속운전을 활성화하기 위해서는 버스에 접속하는 모든 장치가 Hi-Z 상태가 되기 전에 적어도 1회 클럭 사이클 동안 중요한 제어신호를 하이로 구동해야 합니다.이렇게 하면 풀업 저항기는 누출 전류에 직면하여 버스 신호를 유지하는 역할만 합니다.

인텔에서는 이 규약을 "유지된 3가지 상태"라고 부르며 핀 수가 적은 버스에서도 사용합니다.

3주 버스 대체 수단

오픈 컬렉터 입력/출력은 3스테이트 로직의 일반적인 대체 수단입니다.예를 들어, I²C 버스 프로토콜(장치 간에 자주 사용되는 양방향 통신 버스 프로토콜)은 두 통신 라인에서 풀업 저항의 사용을 지정합니다.디바이스가 비액티브하면, 통신 회선을 「해방」해, 그 출력을 트라이 스테이트 해, 회로에의 영향을 없앱니다.버스의 모든 장치가 통신 라인을 "해제"한 경우, 회로에 미치는 유일한 영향은 라인을 높게 당기는 풀업 저항입니다.디바이스는 통신을 필요로 하면 Hi-Z 상태에서 벗어나 회선을 낮춥니다.이 프로토콜을 사용하여 통신하는 디바이스는 회선을 높게 띄우거나 낮게 띄우거나 둘 중 하나입니다.따라서 어떤 디바이스가 회선을 높게 또는 낮게 구동하는 버스 경합 상황을 방지할 수 있습니다.

초기 마이크로컨트롤러에는 입력으로만 동작하는 핀과 푸시풀 출력으로만 동작하는 핀, 오픈 컬렉터 입력/출력으로만 동작하는 핀이 있습니다.일반적인 최신 마이크로컨트롤러에는 이러한 종류의 핀으로 작동하도록 프로그래밍할 수 있는 3가지 상태의 범용 입출력 핀이 많이 있습니다.

3스테이트 버스는 일반적으로 단일 프린트 회로 기판(PCB) 상의 칩 간에 사용되거나 공통 백플레인에 연결된 PCB 간에 사용되기도 합니다.

3 스테이트 로직의 사용은 온칩 접속에는 권장하지 않고 칩 간 [3]접속에는 권장됩니다.

3 스테이트 버퍼는, 복수의 디바이스가 데이터 버스상에서 통신할 수 있도록 하는 경우에, 멀티플렉서로 기능적으로 [4]치환할 수 있습니다.그러면 다양한 디바이스에서 출력을 선택하고 버스에 쓸 수 있습니다.

「 」를 참조해 주세요.

주 및 참고 자료

- ^ Tri-state는 National Semiconductor의 등록상표이지만, 제조원이 제조하는 디바이스를 기술하는 데 자주 사용됩니다.

- ^ Hill, Winfield; Horowitz, Paul (1989). The Art of Electronics. Cambridge University Press. pp. 495–497. ISBN 0-521-37095-7.

- ^ SoC용 온칩버스/네트워크 "온칩버스 [없음] 트라이스테이트버스가 정적 타이밍 해석에 어렵기 때문에 트라이스테이트버스가 사용되지 않음"

- ^ "Tri State Buffer".

외부 링크

- 회선상의 특수 출력 게이트

- 트리스테이트 다중화의 원리