경유(전자 장치)

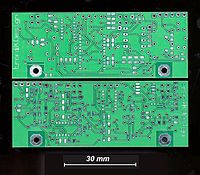

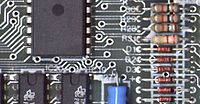

Via (electronics)비아(라틴어로 패스 또는 웨이)는 프린트 회로 기판의 구리층 간의 전기적 연결입니다.기본적으로 비어(via)는 2개 이상의 인접한 층을 통과하는 작은 구멍입니다. 구멍은 구리 층을 분리하는 절연체를 통해 전기적으로 연결되는 구리로 도금됩니다.

Via는 PCB [1]제조에 중요합니다.이는 비아가 일정한 공차로 천공되어 지정된 위치에서 제작될 수 있기 때문에 제조 전에 드릴 위치 오류에 대한 약간의 허용이 필요합니다. 그렇지 않으면 (일부 참조 표준에 따라) 부적합한 기판으로 인해 제조 수율이 감소할 수 있습니다.또한 일반 스루홀 비아는 길고 좁기 때문에 깨지기 쉬운 구조로 간주됩니다.제조업체는 비아가 배럴 전체에 적절히 도금되어 있는지 확인해야 합니다.이것에 의해, 몇개의 가공 단계가 발생합니다.

프린트 기판의 경우

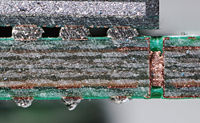

프린트 회로 기판(PCB) 설계에서 비아는 기판의 다른 구리층 위에 대응하는 위치에 있는 2개의 패드로 구성되어 있으며 기판을 [citation needed]통해 구멍으로 전기적으로 연결됩니다.이 구멍은 전기 도금을 통해 전도성이 발생하거나 튜브 또는 [citation needed]리벳으로 라이닝됩니다.고밀도 다층 PCB에는 마이크로비아가 탑재되어 있는 경우가 있습니다.블라인드 비아는 보드의 한쪽 면에만 노출되어 있으며 매립 비아는 어느 한쪽 면에도 노출되지 않고 내부 레이어를 연결합니다.서멀 비아는 전원 장치로부터 열을 전달하며, 일반적으로 약 [2][3]12개의 어레이로 사용됩니다.

Via는 다음과 같이 구성됩니다.

- 배럴 — 드릴로 뚫린 구멍을 채우는 전도성 튜브

- 패드 — 배럴의 각 끝을 구성요소, 평면 또는 트레이스에 연결합니다.

- 안티패드 - 배럴과 금속층이 연결되어 있지 않은 틈새 구멍

비아는 PTV 또는 도금 스루 비아라고 불리기도 하며, 도금 스루 홀(PTH)과 혼동해서는 안 됩니다.Via는 PCB의 구리층 간 상호 연결로 사용되며 PTH는 일반적으로 via보다 크게 만들어지며 비 SMT 저항기, 캐패시터, DIP 패키지 IC 등의 컴포넌트 리드를 수용하기 위한 도금 구멍으로 사용됩니다.PTH는 기계적 연결용 구멍으로도 사용할 수 있지만 ViA는 사용할 수 없습니다.PTH의 또 다른 용도는 기판의 가장자리에 PTH가 정렬되어 있어 기판이 밀링 아웃될 때 PTH가 반으로 잘립니다.주요 용도는 한 PCB를 스택 내에서 다른 PCB에 납땜할 수 있도록 하는 것입니다.따라서 고정 장치의 역할과 [4]커넥터 역할을 동시에 수행합니다.

오른쪽 그림에는 크게 세 가지 종류의 비아가 나와 있습니다.PCB를 만드는 기본 단계는 기판 재료를 만들어 층을 쌓는 것, 비아 도금의 스루 드릴링, 포토 리소그래피와 식판을 이용한 구리 트레이스 패턴 제작입니다.이 표준 절차에서는 통과 구성이 [a]스루홀로 제한됩니다.레이저를 사용하는 등 깊이 제어식 드릴링 기술을 사용하면 더 다양한 타입을 사용할 수 있습니다(레이저 드릴은 기계 드릴이 생성하는 것보다 작고 정확한 위치에 있는 구멍에도 사용할 수 있습니다.PCB의 제조는 일반적으로 기본적인 양면 PCB인 이른바 코어로부터 시작됩니다.이 기본 구성 블록에서 처음 두 개의 레이어를 초과하는 레이어가 쌓입니다.코어 하단에서 2개의 레이어가 연속적으로 쌓이면 1-2 비어, 1-3 비어 및 스루홀을 만들 수 있습니다.각 타입의 비아는 각 적층 단계에서 드릴로 가공됩니다.코어 위에 한 층을 쌓고 아래에서 다른 층을 쌓는 경우 가능한 경유 구성은 1-3, 2-3 및 스루홀입니다.사용자는 PCB 제조원이 허용하는 스태킹 방법 및 가능한 via에 대한 정보를 수집해야 합니다.저렴한 보드의 경우 관통 구멍만 뚫어 비아와 접촉하지 않도록 되어 있는 층에 안티패드(또는 클리어런스)를 배치한다.

IPC 4761

IPC 4761 에서는, 다음의 타입이 정의됩니다.

- 타입 I: 텐트 처리

- 타입 II: 텐트 가공 및 커버 가공

- 타입 III-a: 플러그 바이, 한쪽 면은 비전도성 물질로 씰링

- 타입 III-b: 플러그 비어, 양쪽에 비전도성 재료로 씰링됨

- 타입 IV-a: 플러그 및 커버, 비전도성 소재로 밀봉, 한쪽 면은 젖은 솔더 마스크로 커버

- 타입 IV-b: 콘센트 및 커버, 비전도성 소재로 밀봉, 양쪽이 젖은 납땜 마스크로 덮여 있습니다.

- 타입 V: 비전도성 페이스트로 채워진 비어

- 타입 VI-a: 충전 및 커버, 한쪽 면에는 드라이 필름 또는 습식 납땜 마스크로 덮여 있습니다.

- 타입 VI-b: 충전 및 커버, 드라이 필름 또는 습식 납땜 마스크로 양쪽에 커버

- 타입 VII: 비전도성 페이스트로 충전 및 캡을 씌우고 양면에 도금

장애 동작

올바르게 제조되어 있는 경우 PCB via는 주로 동도금과 PCB의 평면외 방향(Z)의 차이에 의해 장해가 발생합니다.이 차동 팽창 및 수축은 구리 도금에 주기적인 피로를 유발하여 균열 전파 및 전기 개방 회로를 발생시킵니다.다양한 설계, 재료 및 환경 매개변수가 이러한 [5][6]열화 속도에 영향을 미칩니다.견고성을 확보하기 위해 IPC는 고장까지의 시간 [7]계산기를 개발하는 라운드 로빈 연습을 후원했습니다.

집적회로의 Vias

집적회로(IC) 설계에서 비아는 절연 산화층의 작은 개구부이며, 서로 다른 층 간에 전도성 연결을 가능하게 합니다.실리콘 웨이퍼 또는 다이를 완전히 통과하는 집적회로상의 비아는 스루칩 비아(TSV) 또는 스루실리콘 비아(TSV)라고 불립니다.코닝 글라스는 실리콘 [8]패키징에 비해 유리의 전기적 손실이 적기 때문에 반도체 패키징을 위해 TGV(Through-Glass Vias)를 연구해 왔습니다.금속의 최하층을 확산 또는 폴리층에 연결하는 비아는 일반적으로 "접점"이라고 불립니다.

갤러리

CAD의 2층 도금.Vias는 EDA 배치를 가능하게 합니다.

하층 – 빨간색

최상층 – 파란색

「 」를 참조해 주세요.

메모들

- ^ 코어당 관통 구멍이 있습니다.추가 코어 및 적층 단계를 사용하여 블라인드 또는 매립형 비어를 생성할 수 있습니다.또한 도금을 한 쪽에서 원하는 층으로 역추공하여 제거할 수 있으며, 이 층은 물리적 구멍을 관통 구멍으로 남기지만 블라인드 비아와 동등한 전기를 생성합니다.PCB가 블라인드 및 매립형 비어를 정당화할 수 있는 충분한 레이어가 필요한 경우 (레이저로 구멍을 뚫은) 마이크로비어를 필요로 할 정도로 충분히 작은 트레이스도 사용하고 있을 가능성이 있습니다.

레퍼런스

- ^ "PCB Vias: An In-Depth Guide". ePiccolo Engineering.

- ^ "PCB design: A close look at facts and myths about thermal vias".

- ^ Gautam, Deepak; Wager, Dave; Musavi, Fariborz; Edington, Murray; Eberle, Wilson; Dunford, Willa G. (2013-03-17). A review of thermal management in power converters with thermal vias. 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC). Long Beach, California, U.S.A: IEEE. doi:10.1109/APEC.2013.6520276.

- ^ "Castellated Holes / Edge Plating PCB / Castellations". Hi-Tech Corp. 2011. Archived from the original on 2016-05-26. Retrieved 2013-01-02.

- ^ C. Hillman, 장애를 통한 이해, 글로벌 SMT & Packaging – 2013년 11월, 페이지 26-28, https://www.dfrsolutions.com/hubfs/Resources/services/Understanding_Plated_Through_Via_Failures.pdf?t=1514473946162

- ^ C. Hillman, 설계 및 제조를 통한 신뢰성 높은 도금, http://resources.dfrsolutions.com/White-Papers/Reliability/Reliable-Plated-Through-Via-Design-and-Fabrication1.pdf

- ^ "Plated Through Hole (PTH) Fatigue calculator". DfR Solutions. Retrieved 2017-12-17.

- ^ "Progress and Application of Through Glass Via (TGV) Technology" (PDF). corning.com. Retrieved 2019-08-08.

추가 정보

- "Tips for PCB Vias Design" (PDF) (Technical note). Quick-teck. 2014. EN-00417. Retrieved 2017-12-18.

- "Via Tenting - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2014. Printed Circuit Boards > Layout > Design Tip > Tenting. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Plugging - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2014. Printed Circuit Boards > Layout > Design Tip > Plugging. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Filling - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2013. Printed Circuit Boards > Layout > Design Tip > Filling. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Microvia Filling". WE Online. Würth Elektronik GmbH & Co. KG. 2015. Printed Circuit Boards > Layout > Design Tip > Microvia Filling. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Dingler, Klaus; Musewski, Markus (2009-03-18). "Pluggen / Plugging". FED-Wiki (in German). Berlin, Germany: Fachverband Elektronik-Design e.V. (FED). Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Optimization Techniques for High-Speed Channel Designs" (PDF) (Application note). 1.0. Altera Corporation. May 2008. AN-529-1.0. Archived (PDF) from the original on 2017-12-18. Retrieved 2017-12-18.

- Chu, Jun (2017-04-11). "Controlled Depth Drilling, or Back Drilling". Online Documentation for Altium Products. Altium. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Loughhead, Phil (2017-05-30). "Removing Unused Pads and Adding Teardrops". Online Documentation for Altium Products. Altium. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Brooks, Douglas G.; Adam, Johannes (2017-02-09). PCB Trace and Via Temperatures: The Complete Analysis (2nd ed.). CreateSpace Independent Publishing Platform. ISBN 978-1541213524.

외부 링크

- Online Via Calculator(전압, 캐패시턴스, 임피던스, 전력 소산 계산)