전압 승수

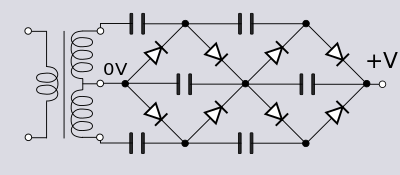

Voltage multiplier전압 승수는 AC 전력을 낮은 전압에서 높은 DC 전압으로 변환하는 전기 회로로, 일반적으로 콘덴서와 다이오드 네트워크를 사용합니다.

전압 승수는 고에너지 물리학 실험 및 번개 안전성 테스트와 같은 목적을 위해 수백만 볼트까지 전자 기기를 위해 몇 볼트씩 생성할 수 있습니다.전압 승수의 가장 일반적인 유형은 빌라드 캐스케이드라고도 불리는 반파 계열 승수입니다(그러나 실제로는 하인리히 그리나허에 의해 발명되었습니다).

작동

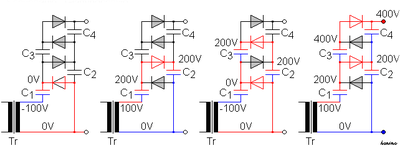

AC전원의 피크전압이 +U이고s C값이 충전되었을 때 전압이 크게 변화하지 않고 전류가 흐를 수 있을 정도로 충분히 높다고 가정하면 캐스케이드의 (간소화된) 동작은 다음과 같습니다.

- 음의 피크(-Us): C 캐패시터는 다이오드11 D를 통해s UV로 충전됩니다(캐패시터의 좌우 플레이트의 전위차는 Us).

- 양의 피크(+Us): C의1 전위가 소스의 전위와 더해져 C를 2U에서s D로2 충전합니다2.

- 음의 피크: C의1 전위가 0V로 떨어졌으므로 C는 D를 통해3 2U로s 충전할 수 있습니다3.

- 양의 피크: C의2 전위가 2U로s 상승하고(스텝 2와 유사하게), C에서 2U로s 충전합니다4.출력 전압(C와 C 아래의2 전압의 합계4)은 4U에s 도달할 때까지 상승합니다.

실제로 C가 최대 전압에 도달하려면4 더 많은 사이클이 필요합니다.2개의 다이오드 및 2개의 캐패시터가 추가될 때마다 출력 전압이 최대 AC 공급 전압의 2배 증가합니다.

전압 더블러 및 트리플러

전압 더블러는 2단계를 사용하여 단일 스테이지 정류기에서 얻을 수 있는 DC 전압을 약 2배로 높입니다.120V 또는 240V 중 하나를 선택하기 위한 SPDT 스위치를 포함한 스위치 모드 전원 입력 단계에서 전압 배율의 예를 찾을 수 있다.120V 위치에서 입력은 일반적으로 브리지 정류기의 AC 연결점 하나를 열고 직렬로 연결된 2개의 필터 캐패시터의 접점에 연결함으로써 전파 전압 더블러로 구성됩니다.240V 동작의 경우 스위치는 시스템을 전파 브릿지로 구성하고 캐패시터 센터탭 와이어를 브리지 정류 시스템의 열린 AC 단자에 다시 연결합니다.따라서 간단한 SPDT 스위치를 추가하여 120V 또는 240V 작업을 수행할 수 있습니다.

전압트리플러는 3단 전압증배기이다.트리플러는 널리 사용되는 전압 증배기입니다.트리플러의 출력전압은 고임피던스로 인해 실제로는 피크입력전압의 3배 미만입니다.부분적으로는 체인 내의 각 캐패시터가 다음 캐패시터에 전력을 공급할 때 부분적으로 방전되어 전압이 손실됩니다.

트리플러는 일반적으로 브라운관(CRT, 화상관)에 고전압을 제공하기 위해 컬러 텔레비전 수상기에서 사용되었습니다.

트리플러는 복사기, 레이저 프린터, 버그재퍼, 전기충격 무기와 같은 고전압 공급 장치에 여전히 사용되고 있다.

고장 전압

멀티플라이어를 사용하여 수천 볼트의 출력을 생성할 수 있지만 전체 전압 범위를 견디기 위해 개별 구성 요소를 정격화할 필요는 없습니다.각 컴포넌트는 자신의 단자와 바로 인접한 컴포넌트의 상대전압차이만 고려하면 됩니다.

일반적으로 전압 승수는 래더처럼 물리적으로 배치되므로 점진적으로 증가하는 전압 전위가 회로의 훨씬 낮은 전위 섹션으로 호를 통과할 기회가 주어지지 않습니다.

사다리가 적어도 하나의 다이오드 또는 캐패시터 구성요소의 단락된 고장에도 살아남을 수 있도록 멀티플라이어의 전압 차이의 상대적 범위에 걸쳐 어느 정도의 안전 여유가 필요합니다.그렇지 않으면 싱글 포인트 단락 장애가 연속적으로 과전압되어 멀티플라이어의 다음 컴포넌트가 파괴되어 멀티플라이어 체인 전체가 파괴될 가능성이 있습니다.

기타 회로 토폴로지

- 스태킹

캐스케이드가 평활 셀에서 끝나도록 모든 컬럼에서 짝수 개의 다이오드 캐패시터 셀이 사용됩니다.클램핑 셀에서 끝나는 홀수일 경우 리플 전압이 매우 커집니다.커넥팅 칼럼의 캐패시터가 클수록 리플도 감소하지만 충전 시간과 다이오드 전류는 증가합니다.

딕슨 충전 펌프

딕슨 충전 펌프 또는 딕슨 승수는 그리너처/콕크로프트-월튼 승수를 개조한 것입니다.단, 이 회로와는 달리 Dickson 멀티플라이어는 DC-DC 컨버터의 형태로 DC 전원을 입력으로 사용합니다.또한 고전압 애플리케이션에서 사용되는 그리너처/콕크로프트-월튼과 달리 딕슨 승수는 저전압 목적으로 설계되었습니다.회로에는 DC 입력 외에 DC 공급 레일 간에 진폭이 흔들리는 2개의 클럭 펄스 트레인의 공급이 필요합니다.이 펄스열은 [1]위상이 어긋난다.

회로의 이상적인 동작을 설명하기 위해 다이오드 D1, D2와 콘덴서 C1, C2 등을 왼쪽에서 오른쪽으로 번호를 매깁니다.클럭이 이 낮으면 D1은 C1을 V로in 충전합니다. 1\ _ {이(가) 하이 상태가 되면 C1의 상판이 2V까지in 밀어집니다.그 후 D1이 꺼지고 D2가 켜지며 C2가 2V로in 충전되기 시작합니다.다음 클럭 사이클 이 다시 로우 상태가 되고 가 하이 상태가 되어 C2의 상판을 3V로in 누른다.D2 스위치가 꺼지고 D3 스위치가 켜지며 C3에서 3V까지in 충전되며 전하가 체인을 통과하므로 충전 펌프라는 이름이 붙습니다.캐스케이드의 최종 다이오드 캐패시터 셀은 클럭 위상이 아닌 접지에 연결되므로 승수가 아니며 평활을 [2]제공하는 피크 검출기입니다.

이상적인in nV의 경우 출력을 감소시키는 요인은 여러 가지가 있습니다.그 중 하나는 스위칭 디바이스의 임계값 전압, 즉T 스위치를 켜는 데 필요한 전압입니다.스위치 전체의 전압 강하에 의해 출력은 nVT 이상 감소합니다.숏키 다이오드는 딕슨 멀티플라이어에서 낮은 순방향 전압 강하 등의 이유로 일반적으로 사용됩니다.또 다른 어려움은 각 노드에서 접지에 기생 캐패시턴스가 있다는 것입니다.이러한 기생 캐패시턴스는 회로의 스토리지 캐패시터가 출력 전압을 더 [3]낮추면서 분압기 역할을 합니다.클럭 주파수가 높을수록 좋습니다. 즉, 리플이 감소하고 주파수가 높으면 나머지 리플을 필터링하기 쉬워집니다.또한 사이클당 저장해야 하는 전하량이 적기 때문에 필요한 캐패시터 크기가 줄어듭니다.그러나 부유 캐패시턴스에 의한 손실은 클럭 주파수의 증가에 따라 증가하며, 실제 한계는 수백 [4]킬로헤르츠 정도입니다.

딕슨 멀티플라이어는 IC에 필요한 전압까지 저전압 배터리 공급을 증가시키는 데 사용되는 집적회로(IC)에서 자주 사용됩니다.IC 설계자와 제조업체는 IC 전체에서 동일한 기술과 동일한 기본 장치를 사용할 수 있는 것이 유리합니다.이러한 이유로 널리 사용되는 CMOS 기술 IC에서 회로의 기본 구성 요소를 구성하는 트랜지스터는 MOSFET입니다.따라서 딕슨 곱셈기 내의 다이오드는 다이오드로서 [5]동작하도록 배선된 MOSFET로 대체되는 경우가 많다.

Dickson 멀티플라이어의 다이오드 배선 MOSFET 버전은 MOSFET의 드레인 소스 전압 강하가 크기 때문에 매우 낮은 전압에서는 잘 작동하지 않습니다.이 문제를 해결하기 위해 보다 복잡한 회로가 사용되는 경우가 많습니다.한 가지 해결책은 선형 영역에 편향된 다른 MOSFET를 스위칭 MOSFET와 병렬로 연결하는 것입니다.이 두 번째 MOSFET는 스위칭 MOSFET 자체보다 드레인 소스 전압이 낮기 때문에(스위칭 MOSFET가 하드 구동되기 때문에) 결과적으로 출력 전압이 증가합니다.선형 바이어스 MOSFET의 게이트는 다음 스테이지의 출력에 연결되어 다음 스테이지가 이전 스테이지의 캐패시터에서 충전되는 동안 꺼집니다.즉, 스위칭 트랜지스터와 동시에 선형 바이어스 트랜지스터가 [6]꺼집니다.

입력이 1.5V인 이상적인 4단 Dickson 승수(5×승수)의 출력은 7.5V입니다.단, 다이오드 배선 MOSFET 4단 멀티플라이어의 출력은 2V에 불과할 수 있습니다.선형 영역에 병렬 MOSFET를 추가하면 이 전압이 약 4V로 향상됩니다. 더 복잡한 회로에서도 이상적인 [7]경우에 훨씬 가까운 출력을 얻을 수 있습니다.

기본 Dickson 회로에는 다른 많은 변형과 개선점이 존재합니다.Mandal-Sarpeshkar 멀티플라이어[8] 또는 [9]Wu 멀티플라이어와 같은 스위칭 임계값 전압을 낮추려고 합니다.다른 회로에서는 임계값 전압이 소거됩니다.우메다 멀티플라이어는 외부에서 제공된[10] 전압으로, 나카모토 멀티플라이어는 내부적으로 생성된 [11]전압으로 소거합니다.Bergeret 승수는 전력 [12]효율을 최대화하는 데 중점을 두고 있습니다.

RF 전원 변경

CMOS 집적회로에서는 클럭 신호를 쉽게 이용할 수 있거나 쉽게 생성할 수 있습니다.RF 집적회로에서는 반드시 이 문제가 발생하는 것은 아니지만 RF 전원을 사용할 수 있는 경우가 많습니다.표준 Dickson 승수 회로는 일반 입력과 클럭 입력 중 하나를 접지하는 것만으로 이 요건을 충족하도록 변경할 수 있습니다.RF전원은 다른 클럭 입력에 주입되어 회로 입력이 됩니다.RF 신호는 사실상 클럭이자 전원입니다.단, 클럭은 다른 모든 노드에만 주입되므로 회로는 제2의 다이오드 캐패시터 셀마다 곱셈 단계만 달성합니다.다른 다이오드 캐패시터 셀은 피크 검출기 역할을 하며 [13]증배 없이 리플을 평활화합니다.

크로스 커플링 스위치 콘덴서

전압증배기는 크로스커플형 스위치 콘덴서 타입의 캐스케이드 전압배율로 형성되어도 된다.이 유형의 회로는 일반적으로 소스 전압이 1.2V 이하일 때 딕슨 승수 대신 사용됩니다.다이오드 배선 트랜지스터의 전압 강하가 출력 전압에 비해 훨씬 더 커지기 때문에 입력 전압이 떨어짐에 따라 딕슨 곱셈기의 전력 변환 효율이 점점 떨어집니다.크로스 커플링 회로의 트랜지스터는 다이오드 배선이 아니기 때문에 전압 강하 문제는 그리 [14]심각하지 않습니다.

회로는 각 스테이지의 출력을 _에 의해 구동되는 전압 더블러와 _에 의해 구동되는 전압 더블러 사이에서 번갈아 전환함으로써 작동합니다.이 동작은 Dickson 멀티플라이어에 비해 2배의 주파수에서 리플 전압이 감소한다는 또 다른 이점을 가져옵니다.리플 주파수의 증가는 필터링을 통해 제거가 용이하기 때문에 유리합니다.각 스테이지(이상 회로 내)는 피크 클럭 전압만큼 출력 전압을 상승시킵니다.이것이 DC 입력 전압과 같은 레벨이라고 가정하면 n 스테이지 승수는 nV를in 출력합니다(이상적으로).크로스커플링 회로의 손실의 주된 원인은 스위칭 임계값 전압이 아니라 기생 캐패시턴스입니다.손실은 일부 에너지가 각 [15]사이클에서 기생 캐패시턴스를 충전해야 하기 때문에 발생합니다.

적용들

TV의 음극선관(CRT)용 고전압 공급 장치에서는 CRT 자체의 내부 및 외부 수중 코팅에 의해 형성된 최종 단계의 스무딩 캐패시터가 포함된 전압 승수를 사용하는 경우가 많습니다.CRT는 이전에는 텔레비전 수상기의 공통 컴포넌트였습니다.전압 승수는 최신 TV, 복사기 및 [16]버그 잡기에서 여전히 찾아볼 수 있습니다.

고압 승압기는 스프레이 도장 장비에 사용되며, 자동차 제조 시설에서 가장 일반적으로 볼 수 있습니다.도료분무기의 노즐에 출력 약 100kV의 전압증배기를 사용하여 무화도료 입자를 대전시키고, 그 후 반대방향으로 대전하는 금속면에 흡착하여 도장한다.이렇게 하면 페인트 사용량을 줄일 수 있고 페인트 코팅이 균일하게 펴지는 데 도움이 됩니다.

고에너지 물리학에서 사용되는 일반적인 전압 승수는 콕크로프트-월튼 발전기이다. (John Douglas Cockcroft와 Ernest Thomas Sinton Walton은 1951년 노벨 물리학상을 받은 입자 가속기를 위해 설계되었다.)

「 」를 참조해 주세요.

- 마르크스 제너레이터(스위치 소자로 다이오드 대신 스파크 갭을 사용하여 다이오드보다 높은 피크 전류를 전달할 수 있는 장치).

- 부스트 컨버터(대부분 인덕터를 사용하여 전압을 올리는 DC-DC 전력 변환기)

메모들

- ^ 류, 페이지 226

- 위안, 페이지 14

- ^ 류, 226~227페이지

- ^ 위안, 13~14페이지

류 2006, 227~228페이지 - ^ 펠루소 외, 35페이지

- 줌발렌, 페이지 741

- ^ 류, 226~228페이지

- 위안, 페이지 14

- ^ 류, 228-230페이지

- 위안, 14-16페이지

- ^ 위안, 14-16페이지

- ^ 위안, 17~18페이지

- ^ 류, 230–232페이지

- ^ 위안, 18-20페이지

- ^ 위안, 19-20페이지

- ^ 위안, 20~21페이지

- ^ 류, 228-230페이지

- 위안, 14~15페이지

- ^ 캄파르도 외, 377-379페이지

- 류, 232~235페이지

- 린, 페이지 81

- ^ 캄파르도 외, 379페이지

- 류, 234페이지

- ^ 맥고원, 87페이지

참고 문헌

- 캄파르도, 지오반니, 미켈로니, 리노, 노보셀, 데이비드 VLSI-design of Non-volatile Memory, Springer, 2005 ISBN3-540-20198-X.

- Lin, 미니어처 센서 시스템용 Yu-Shiang 저전력 회로, Publisher ProQuest, 2008 ISBN 0-549-98672-3.

- Liu, Mingliang Demystifying Switched Capacitor Circuit, Newnes, 2006 ISBN 0-7506-7907-7.

- McGowan, Kevin, Semiconductors: Cenge Learning, 2012 ISBN 1133708382, Book to Breadboard.

- Peluso, Vincenzo; Steyaert, Michiel; Sansen, Willy M. C. 저전압 저전력 CMOS 델타-시그마 A/D 변환기 설계, Springer, 1999년 ISBN 0-7923-8417-2.

- Yuan, 패시브 무선 마이크로시스템용 Fei CMOS Circuits, Springer, 2010 ISBN 1-4419-7679-5.

- 줌발렌, 행크 리니어 회로 설계 핸드북, 뉴네스, 2008 ISBN 0-7506-8703-7.

외부 링크

- 기본 승수 회로

- 콕크로프트 월튼 곱셈기

- 카데트 브랜드(국제전파공사) 모델 1019의 개략도.진공관(25Z5) 전압 증배 정류기가 있는 1937년형 라디오.

낮으면 D1은 C1을 V로in 충전합니다.

낮으면 D1은 C1을 V로in 충전합니다. 하이 상태가 되어 C2의 상판을 3V로in 누른다.D2 스위치가 꺼지고 D3 스위치가 켜지며 C3에서 3V까지in 충전되며 전하가 체인을 통과하므로

하이 상태가 되어 C2의 상판을 3V로in 누른다.D2 스위치가 꺼지고 D3 스위치가 켜지며 C3에서 3V까지in 충전되며 전하가 체인을 통과하므로