64b/66b 부호화

64b/66b encoding데이터 네트워킹 및 전송에서 64b/66b는 64비트 데이터를 66비트 회선 코드로 변환하는 회선 코드입니다.이를 통해 수신측에서 데이터 스트림을 적절히 회복하고 정렬할 수 있습니다.IEEE 802.3 워킹그룹에 의해 10 기가비트/초이더넷을 도입한 IEEE 802.3ae-2002 개정의 일부로 정의되었습니다.64b/66b를 도입했을 때는 SONET OC-192와 같은 레이저로 10 Gb 이더넷을 전송할 수 있었습니다.수년간 사용할 수 없었던[when?] 12.5 Gbit/s 레이저가 필요했습니다.

부호화 방식의 프로토콜 오버헤드는 원시 페이로드 비트 수에 추가된 부호화 비트 수를 더한 비율입니다.64b/66b 부호화의 오버헤드는 64 페이로드 비트마다 2개의 코딩 비트 또는 3.125%입니다.이는 이전에 사용하던8b/10b 부호화 방식의 25% 오버헤드를 대폭 개선한 것입니다.이 방식은 8개의 페이로드 비트에2개의 코딩 비트를 추가합니다.

오버헤드는 페이로드 크기를 2배로 하여 PCIe 3.0에서 사용되는 128b/130b 인코딩을 생성함으로써 더욱 줄일 수 있습니다.

기능.

스킴명이 나타내듯이 64개의 페이로드 비트가 66비트엔티티로 부호화됩니다.66비트 엔티티는 2비트 프리암블 중 하나를 64 페이로드 비트에 프리픽스함으로써 생성됩니다.

- 프리암블이 01인2 경우 64개의 페이로드 비트는 데이터입니다.

- 프리암블이 10인2 경우 64개의 페이로드 비트는 8비트 타입 필드와 56비트의 제어 정보 및/또는 데이터를 보유합니다.

프리암블2 00과2 11은 사용되지 않으며 오류가 있는 경우 이를 나타냅니다.

012 및 102 프리암블을 사용하면 66비트마다 비트 천이를 보증합니다.즉, 연속되는0 또는 1의 스트림은 유효한 데이터가 될 수 없습니다.또, 66비트 마다 천이를 확인할 필요가 있기 때문에, 클럭/타이머의 동기화가 용이하게 됩니다.

다음으로 64비트 페이로드는 자기동기 스크램블러 기능을 사용하여 스크램블됩니다.스크램블링은 데이터를 암호화하기 위한 것이 아니라 전송되는 데이터에서 1과 0의 비교적 균일한 분포를 찾기 위한 것입니다.스크램블러는 출력 데이터가 0 또는 모든 1의 긴 런렝스 또는 통신에서 바람직하지 않은 기타 속성을 갖는 것을 보증할 수 없지만 이러한 이벤트의 확률에 대해 강력한 통계적 경계를 설정할 수 있습니다.실용적인 설계에서는 롱런렝스로 인한 비트오류가 발생하지 않도록 시스템 파라미터를 선택합니다.이 방법은 코드북 기반의 8b/10b 인코딩 방식과는 다릅니다.

일반적으로 인코딩과 스크램블링은 모두 하드웨어로 구현되며 스크램블러는 선형 피드백 시프트 레지스터를 사용합니다.소프트웨어 스택의 상위 레이어에서는 링크레이어가 이러한 방식을 사용하고 있음을 인식할 필요가 없습니다.

속성 및 응용 프로그램

64b/66b의 설계 목표는 클럭 리커버리, 스트림 얼라인먼트, DC 밸런스, 트랜지션 밀도 및 런렝스입니다.8b/10b 인코딩은 DC 밸런스, 트랜지션 밀도 및 런렝스에 엄격한 경계를 보증하는 반면 64b/66b는 이러한 특성에 대한 통계적 경계를 제공합니다.

실행 길이

SONET OC-192 및 64b/66b용으로 설계된 대부분의 클럭 회복 회선은 80비트 실행 길이를 허용하도록 지정되어 있습니다.이러한 실행은 64b/66b에서는 발생할 수 없습니다.이는 전환이 66비트 간격으로 보장되기 때문입니다.또한 실제로 장기 실행 가능성은 매우 낮기 때문입니다.랜덤 데이터 패턴이 스크램블러 상태에 맞추어 65개의 제로 또는 65개의 롱런을 생성하는 것은 이론적으로 가능하지만, 그러한 현상이 발생할 확률은 페어코인을 던져서 같은 상태로 64회 연속 상승시키는 것과 같다.랜덤 데이터를 가정할 때 65비트 실행 길이를 가진 66비트 블록의 예상 이벤트 속도는 66×2µ10µ2초6410, 즉 1900년에 한 번 정도입니다.

데이터가 랜덤이 아닌 특별히 선택된 패턴으로 구성되면 런 길이 통계량이 더 나빠질 수 있습니다.Packet over SONET/SDH에서 사용된 이전 스크램블러( RFC1619(1994)에서는 내부 스테이트가 7비트밖에 없는 짧은 다항식이 있어 악의적인 공격자가 모든 2-1 스테이트에서7 패턴을 전송함으로써 Denial-of-Service 공격을 발생시킬 수 있었습니다.이 공격 중 하나는 클럭 리커버리 회선의 비동기화가 보증되었습니다.이 취약성은 스크램블러 길이가 43비트(RFC2615(1999)로 증가할 때까지 비밀로 유지되어 악의적인 공격자가 짧은 시퀀스로 시스템을 방해할 수 없습니다.

64b/66b는 충분한 랜덤 내부 상태(58비트)를 가진 스크램블링 다항식을 사용하여 [1]: 11–13 이 취약성을 회피했습니다.이를 통해 교묘하게 조작된 이더넷패킷을 사용하는 전용 공격자는 약 29년에 한 번만 스크램블러 출력에 64비트 런렝스를 생성할 수 있습니다.그러면 랜덤 데이터를 사용하는 것과 유사한 속도로 65비트 실행을 포함하는 66비트 블록이 생성됩니다.

DC 밸런스

DC 밸런스 64b/66b는 절대 경계가 아닙니다.단, 스크램블러 출력이 랜덤바이너리 비트의 시퀀스에 근접하고 있음을 알 수 있습니다.이러한 시퀀스를 AC커플링 회로를 통과시키면 가우스 분포를 따르는 베이스라인 방랑 노이즈가 생성되어 시스템 에러율에 대한 영향을 통계적으로 정량화할 수 있습니다.실제로 100Ω 시스템에서 1nF의 적당한 커플링 콘덴서 값은 2.5% 이상의 DC 드리프트가 10비트당22 1회(10Gbit/s로 약 31,700년)보다 적게 발생한다는 것을 보증하기에 충분합니다.[1]:15–16

해밍 거리

10 기가비트이더넷은 단일 동작링크에 대해 Mean Time to False Packet Acceptance(MTTFPA)를 약 10억 년으로 해야 하는 엄격한 차터입니다.통상적인 비트 에러 레이트로 이것을 실현하려면 , 모든 패킷 데이터에 대해서 적어도4비트 해밍 거리 보호가 필요합니다.즉, 패킷 경계 내에서 랜덤하게 간격을 둔3개의 비트 플립의 모든 조합을 검출하여 무효화 패킷을 생성해야 합니다.64b/66b 패킷의 4비트 해밍 거리를 달성하기 위해 여러 가지 전략이 결합되었습니다. 1) 강력한 유형 필드가 4비트 해밍 거리로 선택되었고 2) 스크램블러 다항식이 패킷 보호에 사용되는 CRC-32와 호환되도록 선택되었으며 3) 패킷 경계에 인접한 프로토콜 위반이 비활성화되도록 요구되었습니다.CRC-32와 선택된 스크램블러 다항식의 조합은 최적화된 C 프로그램을 사용하여 가능한 모든 패킷 크기에 대해 모든 4비트 오류 패턴을 완전히 열거함으로써 평가되었습니다.

관찰.

64b/66b의 주요 기여는 결정론적 실행 길이와 8b/10b의 전이 밀도가 항상 25% 코드 오버헤드의 가치가 있는 것은 아니며, 통계적으로 제한된 방법을 사용하여 견고한 시스템을 설계할 수 있다는 관찰이다.어느 시점에서는 전원 공급기와 같은 구성 요소의 MTBF 또는 우주선이나 태양 플레어와 같은 현상으로 인한 실질적인 위험이 8b/10b 및 64b/66b 시스템의 신뢰성을 지배한다.

바리에이션

인터라켄 프로토콜은 더 많은 코딩 비트를 교환하여 DC 밸런스를 더욱 향상시킵니다.64b/67b 인코딩은 명시적인 DC 밸런싱을 통해 64b/66b를 확장합니다.이는 소형 온칩 커플링 캐패시터를 사용하는 등 일부 애플리케이션에 도움이 될 수 있습니다.

PCI Express 3.0에서는 128b/130b 인코딩이 도입되었습니다.이것은 64b/66b와 비슷하지만 페이로드가 64비트가 아닌 128비트이며 다른 스크램블링 다항식 x23 + x2116 + x85 + x + 1을2 사용합니다.또한 자체 동기화되지 않으므로 64b/66b와 대조적으로 시드 값을 명시적으로 동기화해야 합니다.

USB 3.1 및 DisplayPort 2.0은 128b/132b 인코딩을 사용합니다.이는 64b/66b와 동일하지만 각 프리암블비트를 복제하여 검출되지 않은 에러의 위험을 줄입니다.

후계자

각 {n}b/{n+2}b 인코딩에 대해 기호/데이터 비율은 항상 1보다 낮습니다.128b/130b 인코딩의 비율이 0.985이므로 실질적인 개선 여지는 없습니다.

데이터 레이트를 한층 더 높이기 위해서, 다음의 어프로치를 사용할 수 있습니다.

- FEC와 조합한 높은 심볼 레이트

매우 일반적인 것은 512b/514b 인코딩과 Reed-Solomon 오류 수정입니다.다음과 같은 변종이 자주 사용됩니다.

- RS(528,514,,10), 512b/514b 코드 워드에 14개의 수정 비트를 추가하여 최대 의 손상된 비트를 수정할 수 있습니다.오버헤드는 3%로 64b/66b 인코딩과 동일합니다.

- RS(544,514,14,10), 512b/514b 코드 워드에 30개의 수정 비트를 추가하여 최대 15개의 손상된 비트를 수정할 수 있습니다.오버헤드는 6%입니다.

FEC를 사용하면 심볼 오류율이 2.3 · 10−5 또는 2.2 · 10으로−4 전송되는 데이터에서 비트 오류율이 10 미만입니다−15.

- FEC와 조합한 멀티 레벨 부호화

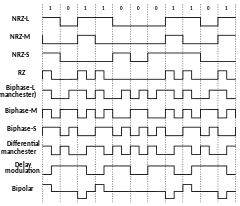

PAM-2에서 PAM-4 또는 Ensemble NRZ 코딩으로 전환함으로써 더 많은 개선이 가능합니다.

- FEC와 조합한 다단계 Treellis 변조

64b/66b 인코딩을 사용하는 테크놀로지

128b/1xxb 인코딩을 사용하는 테크놀로지

- NVLink 1.0

- PCIe 3.x

- PCIe 4.x

- PCIe 5.x

- SATA 3.2

- SAS 4

- USB 3.1 Gen 2

- USB4

- DisplayPort 2.0

256b/257b 인코딩을 사용하는 테크놀로지

- 파이버 채널 32GFC '제6세대' 이후

레퍼런스

- ^ R.C. Walker; R. Dugan (January 18–20, 2000). "64b/66b low-overhead coding proposal for serial links" (PDF). IEEE 802.3 High Speed Study Group.

외부 링크

- 이는 IEEE에 대한 최초 제안이며 최종 합의된 표준에 대해 몇 가지 변경이 이루어졌음을 유의하십시오.제안서에 기술된 58비트 스크램블링 다항식의 회로도는 표준에서 채택된 것과 동일합니다.그러나 제안서의 x+x19+1 다항식이58 표준에서 x+x39+1로 표시된58 것과 동일하도록 제안서는 레지스터에 역순으로 번호를 매긴다.

- 미국 특허/US6650638:64b/66b 부호화 시리얼 데이터 디코딩 방법 및 디코더

- 미국 특허/US6718491: 오버헤드가 적은 패킷화된 시리얼 데이터의 부호화 방법 및 부호화

- 미국 특허/US7055073: 패킷화된 시리얼 데이터를 낮은 오버헤드로 부호화하는 부호화 방법

- 특허 뷰/EP1133123 소프트웨어 특허: 64b/66b 디코딩, 패킷화 시리얼 데이터용

- 64/66비트 부호화 링크 오류 수정

- 10 기가비트 64b/66b의 개요(Clause 49)

- 64b/66b 부호화와 스크램블링에 관한 Xilinx의 레퍼런스 설계

- Aurora 64B66B IP 코어(64b/66b 인코딩 사용)