AND-OR-Invert(반전)

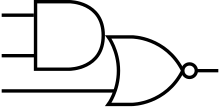

AND-OR-invertAND-OR-Invert(AOI) 논리 및 AOI 게이트는 하나 이상의 AND 게이트와 NOR 게이트의 조합으로 구성된 2레벨 화합물(또는 복합) 논리 함수이다.총 트랜지스터 게이트 수를 NAND 로직 또는 NOR 로직으로 동일한 구성과 비교할 수 있는 CMOS 기술을 사용하여 AOI 셀의 구축이 특히 효율적입니다.AOI 로직의 보완은 OR-AND-Invert(OAI) 로직이며, 여기서 OR 게이트는 NAND [1]게이트 앞에 있습니다.

개요

대부분의 로직 최적화는 곱의 합계 또는 곱의 논리식을 [2]낳습니다.

AOI는 곱의 합에 사용되며, 변수는 AND화 되어 함께 OR화된 후 반전되는 다음과 같은 민항이 형성됩니다.

- AB + CD

- ABC + DEF

- ABCD + EFGH

- ABCDE + FGH + JK

- 기타 변형

논리 연산

AOI 게이트는 1개 이상의 AND 연산을 실행하고 이어서 OR 연산을 실행한 후 반전한다.

2-2 AOI 게이트

2-2 AOI 게이트는 다음 부울 방정식 및 진실 표로 나타낼 수 있습니다.

| 2-2 AOI | ||||

| 입력 A B C D | 산출량 Q | |||

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |

2-1 AOI 게이트

2-1 AOI 게이트는 다음 부울 방정식 및 진실 표로 나타낼 수 있습니다.

| 2-1 AOI | |||

| 입력 A B C | 산출량 Q | ||

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

전자 도입

AND-OR-Invert(AOI) 및 OAI 게이트는 CMOS 회로에 쉽게 구현할 수 있습니다.AOI 게이트는 특히 트랜지스터(또는 게이트)의 총수가 AND, NOT 및 OR 함수를 개별적으로 구현했을 때보다 적다는 점에서 유리하다.그 결과 속도 향상, 전력 절감, 면적 축소 및 잠재적으로 제조 비용 절감으로 이어집니다.예를 들어 2입력 NAND 게이트(4개의 트랜지스터), 인버터(2개의 트랜지스터), 2입력 NOR 게이트(4개의 트랜지스터)를 사용하는 10개의 트랜지스터에 비해 CMOS에 6개의 트랜지스터를 사용하여 2-1 AOI 게이트를 구성할 수 있습니다.

NMOS 로직에서는 CMOS 회로의 하부 절반이 부하 장치 또는 풀업 트랜지스터(일반적으로 고갈 부하 또는 동적 부하)와 함께 사용됩니다.

AOI 게이트는 트랜지스터-트랜지스터 로직(TTL)에서도 마찬가지로 효율적입니다.

- 예

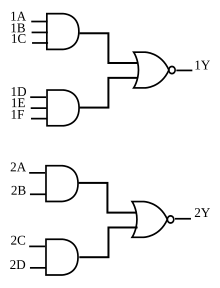

TTL 7400 시리즈 로직 패밀리: (과거 수십 년 동안 7400 시리즈에서는 다수의 AOI 부품을 사용할 수 있었지만, 현재는 대부분 사용되지 않습니다.)

- SN5450 = 듀얼 2-2 AOI 게이트, 하나는 확장[4] 가능(SN54는 SN74의 군사 버전)

- SN74LS51 = 2-2 AOI 게이트 및 3-3 AOI 게이트[3]

- SN54LS54 = 단일 2-3-3-2 AOI 게이트[5]

CMOS 4000 시리즈 로직 패밀리:

- CD4085B = 듀얼 2-2 AOI 게이트[6]

- CD4086B = 싱글 확장형 2-2-2 AOI 게이트"[7]

- CD4048B = 싱글 확장형 8입력 8기능(3스테이트 출력 포함), 게이트 유형: 8 NOR / 8 OR / 8 NAND / 8 AND / 4-4 AND-OR / 4-4 AND-Invert / 4-4 OR - AND - AND - AND - INvert[8] / 4-4

「 」를 참조해 주세요.

레퍼런스

- ^ 카노 맵을 사용한 합계 감소의 산물.

- ^ 제품합계(SOP) 및 제품합계(POS)

- ^ a b "SN74LS51 Datasheet". Texas Instruments. 1988. Archived (PDF) from the original on November 30, 2020.

- ^ "SN5450 Datasheet". Texas Instruments. 1988. Archived (PDF) from the original on July 26, 2018.

- ^ "SN54LS54 Datasheet". Texas Instruments. 1988. Archived (PDF) from the original on March 5, 2018.

- ^ "CD4085B Datasheet". Texas Instruments. 2003. Archived (PDF) from the original on March 3, 2019.

- ^ "CD4086B Datasheet". Texas Instruments. 2003. Archived (PDF) from the original on April 15, 2019.

- ^ "CD4048B Datasheet". Texas Instruments. 2003. Archived (PDF) from the original on March 5, 2019.

- Tinder, Richard F. (2000). Engineering digital design: Revised Second Edition. pp. 317–319. ISBN 0-12-691295-5. Retrieved 2008-07-04.

- John, Michael (1997). Application-Specific Integrated Circuits. Retrieved 2008-07-04.