NOR 논리학

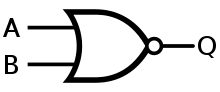

NOR logicNOR 게이트 또는 NOT OR 게이트는 두 입력이 모두 음수일 때만 양의 출력을 제공하는 논리 게이트다.

낸드 게이트와 마찬가지로 NOR 게이트도 다른 어떤 종류의 논리 게이트를 형성하기 위해 결합할 수 있는 이른바 '범용 게이트'이다.예를 들어, 최초의 임베디드 시스템인 아폴로 유도 컴퓨터는 NOR 게이트로부터 독점적으로 구축되었으며, 이후 버전에서는 총 5,600여 대가 구축되었다.오늘날, 집적회로는 오직 하나의 관문형식으로만 구성되지 않는다.대신에 EDA 도구는 논리 회로에 대한 설명을 복잡한 관문(표준 셀) 또는 트랜지스터(완전한 사용자 정의 접근법)의 순목록으로 변환하는 데 사용된다.

NOR

NOR 게이트는 논리적으로 반전 OR 게이트다.다음과 같은 진리표가 있다.

| ||||||||||||||||

| Q = A NOR B

| ||||||||||||||||

NOR 게이트를 사용하여 다른 게이트 만들기

NOR 게이트는 범용 게이트로, 다른 게이트는 NOR 게이트의 조합으로 표현될 수 있다는 것을 의미한다.

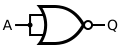

NOT

이것은 NOR 게이트의 입력을 결합하여 만들어진다.NOR 게이트는 NOT 게이트로 이어지는 OR 게이트와 동일하므로, 입력에 합류하면 NOR 게이트의 "OR" 부분의 출력이 입력과 동일하게 되어 고려에서 제거하고 NOT 부분만 남는다.

| 원하는 NOT 게이트 | NOR 건설 | ||||||

|---|---|---|---|---|---|---|---|

|  | ||||||

| Q = NOT(A) | = A NOR A | ||||||

| |||||||

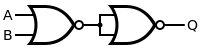

OR

OR 게이트는 NOR 게이트의 출력을 반전시켜 만들어진다.NOT 게이트는 입력을 결합한 NOR 게이트와 동일하다는 것을 이미 알고 있다는 점에 유의하십시오.

| 원하는 OR 게이트 | NOR 건설 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = A 또는 B | = ( A NOR B ) NOR ( A NOR B ) | |||||||||||||||

| ||||||||||||||||

AND

AND 게이트는 두 입력이 모두 1일 때 출력 1을 제공한다.따라서 NOR 게이트의 입력을 뒤집어서 AND 게이트를 만든다.다시, NOT 게이트는 입력이 결합된 NOR과 동등하다는 점에 유의하십시오.

| 원하는 AND 게이트 | NOR 건설 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = A AND | = ( A NOR A ) NOR (B NOR B ) | |||||||||||||||

| ||||||||||||||||

낸드

NAND 게이트는 AND 게이트의 출력을 뒤집어서 만들어진다.NAND라는 단어는 그것이 AND가 아니라는 것을 의미한다.이름에서 알 수 있듯이, 입력 두 개가 모두 1일 때 0이 된다.

| 원하는 NAND 게이트 | NOR 건설 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = A NAND B | = [ ( A NOR A ) NOR ( B NOR B ) ] NOR [ ( A NOR A ) NOR (B NOR B ) ] | |||||||||||||||

| ||||||||||||||||

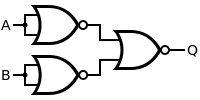

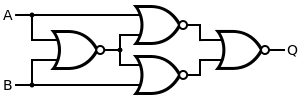

엑스노르

XNOR 게이트는 아래와 같이 NOR 게이트 4개를 연결하여 만든다.이 구조는 단일 NOR 게이트의 3배에 달하는 전파 지연을 수반한다.

| 원하는 XNOR 게이트 | NOR 건설 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = A XNOR B | = [ A NOR ( A NOR B ) ] NOR [ B NOR ( A NOR B ) ] | |||||||||||||||

| ||||||||||||||||

또는 NOR 는 NOR 게이트가 역입력 및 게이트라는 데 모건의 법칙에 따라 결벽 정상 형태 (A+{\overline{({\overline를 고려하여 XNOR 게이트를 만든다이 공사는 4문이 아닌 5개의 관문을 사용한다.

| 원하는 게이트 | NOR 건설 |

|---|---|

|  |

| Q = A XNOR B | = [ B NOR ( A NOR A ) ] NOR [ A NOR (B NOR B ) ] |

XOR

XOR 게이트는 NOR 게이트가 역입력 및 게이트라는 것을 모건의 법칙에서 언급하면서 접속 정상 형태 스타일를 고려하여 만들어진다이 공사는 단일 NOR 게이트의 3배에 달하는 전파 지연을 수반하며 5개의 게이트를 사용한다.

| 원하는 XOR 게이트 | NOR 건설 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||||||||

| Q = A XOR B | = [ ( A NOR A ) NOR ( B NOR B ) ] NOR (A NOR B ) | |||||||||||||||

| ||||||||||||||||

또는 XNOR 게이트의 4-게이트 버전을 인버터와 함께 사용할 수 있다.이 구조는 단일 NOR 게이트의 4배(3회 대신)의 전파 지연을 가진다.

| 원하는 게이트 | NOR 건설 |

|---|---|

|  |

| Q = A XOR B | = { [ A NOR ( A NOR B ) ] NOR [ B NOR ( A NOR B ) ] } NOR { [ A NOR ( A NOR B ) ] NOR [ B NOR ( A NOR B ) ] } |