캐스코드

Cascodecascode는 공통 베이스 [1][2]스테이지에 공급되는 공통 이미터 스테이지로 구성된 2단 앰프입니다.

단일 앰프 스테이지에 비해 이 조합은 입출력 절연, 입력 임피던스, 출력 임피던스, 대역폭의 1개 또는 여러 특성을 가질 수 있습니다.

최신 회로에서 캐스코드는 종종 두 개의 트랜지스터(BJT 또는 FET)로 구성되며, 하나는 공통 이미터 또는 공통 소스로 작동하고 다른 하나는 공통 베이스 또는 공통 게이트로 작동합니다.캐스코드는 출력에서 입력으로 직접 결합되지 않으므로 입출력 격리(역방향 전송 감소)를 개선합니다.이것에 의해, 밀러 효과가 없어지기 때문에, 대역폭이 큰폭으로 확대됩니다.

역사

캐스코드(cascoding)의 사용은 아날로그 회로 성능을 개선하기 위한 일반적인 기술로 진공 튜브와 트랜지스터 모두에 적용됩니다."캐스코드"라는 이름은 1939년 전압 안정기 [3]적용에 대한 토론에서 프레데릭 빈튼 헌트와 로저 웨인 힉먼이 쓴 기사에서 만들어졌다.그들은 펜토드를 대체하기 위해 두 개의 3극(첫 번째에는 공통 음극 설정이 있고 두 번째에는 공통 그리드가 있음)의 캐스케이드를 제안했고, 따라서 그 이름은 "casc(단일 펜토드와 비슷하지만 노이즈가 적은 특성을 가진 3극 증폭기)"[4]의 약자로 가정할 수 있다.캐스코드 회로는 노이즈가 적고 대역폭이 넓기 때문에 '프런트 엔드' 또는 튜너용 초기 텔레비전에 사용되었습니다.

작동

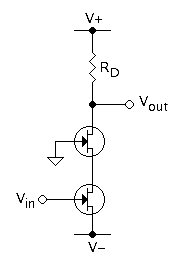

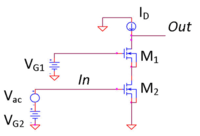

그림 1은 공통 소스 앰프를 신호 소스in V에 의해 구동되는 입력 스테이지로 하는 캐스코드 앰프의 예를 나타냅니다.이 입력 스테이지에서는 출력 신호out V를 사용하여 공통 게이트 앰프를 출력 스테이지로 구동합니다.

하부 FET가 전도함에 따라 상부 FET의 소스 전압이 변화하고 상부 FET는 게이트와 소스 사이의 전위 변화로 인해 전도됩니다.

이 회로 배열의 주요 장점은 상부 전계 효과 트랜지스터(FET)를 입력(하부) FET의 출력 단자(드레인)의 부하로 배치하는 것입니다.작동 주파수에서는 상부 FET의 게이트가 효과적으로 접지되기 때문에 작동 중에 상부 FET의 소스 전압(따라서 입력 트랜지스터의 드레인)이 거의 일정한 전압으로 유지됩니다.즉, 상부 FET는 하부 FET에 대한 낮은 입력 저항을 나타내므로 하부 FET의 전압 게인이 매우 작아져 하부 FET의 드레인에서 게이트까지의 밀러 효과 피드백 캐패시턴스가 크게 감소합니다.이 전압 게인의 손실은 상부 FET에 의해 복구됩니다.따라서 상부 트랜지스터는 하부 FET를 최소한의 음(Miller) 피드백으로 작동시켜 대역폭을 향상시킵니다.

그래서 물기를 빼고 게이트 사이의 표류 정전 용량, Cdg의 충방전이 주파수 반응이 관련된 RC시간 상수 τ)Cdg RD//Rout 이상의 주파수, 즉 f)1(2πτ),는 상당히 높은 주파수 때문에 Cdg은 단지 동안 영향을 받다 RD고 출력 부하(에서 추방이라고 말한다)단순하고, 상단 FET게이트 전기적으로 자리잡혀 있다.작은.즉, 상부 FET 게이트는 C의dg 밀러 증폭에 영향을 받지 않습니다.

상부 FET 스테이지가 소스를 입력 노드(즉, Common-Gate(CG; 공통 게이트) 구성)로 단독으로 동작하는 경우 전압 게인이 양호하고 대역폭이 넓습니다.단, 입력 임피던스가 낮기 때문에 매우 임피던스가 낮은 전압 드라이버로 유효성이 제한됩니다.낮은 FET를 추가하면 입력 임피던스가 높아지기 때문에 캐스코드 스테이지를 높은 임피던스 소스로 구동할 수 있습니다.

만약 한 전형적인inductive/resistive 하중과 입력 트랜지스터의 배수(그것은, common-source(CS)구성)의 출력을 상단-FET로 교체한다면, CS구성, 하지만 캐스코 우드 구성은 잠재적으로 더 큰 이득과 많은 것을 제공 할 수 있는 cascode[의심스러운 –을 논의하]과 같은 입력 임피던스를 제공할 수 있다. 더 큰 대역 폭입니다.

안정성.

캐스코드 배치도 매우 안정적입니다.출력은 전기적으로나 물리적으로나 입력으로부터 효과적으로 격리됩니다.하부 트랜지스터는 드레인 및 소스 모두에서 거의 일정한 전압을 가지므로 게이트에 피드백할 "아무 것도" 없습니다.상부 트랜지스터는 게이트 및 소스에서 거의 일정한 전압을 가집니다.따라서 이들 노드에 상당한 전압이 존재하는 유일한 노드는 입력과 출력이며, 이들은 거의 일정한 전압의 중앙 연결과 2개의 트랜지스터의 물리적 거리에 의해 분리됩니다.따라서 실제로는 출력에서 입력으로 피드백이 거의 없습니다.금속 차폐는 효과적이며 두 트랜지스터 사이에 제공이 용이하여 필요할 때 더욱 큰 절연 효과를 발휘합니다.이는 고주파에서는 중성화가 필요한 단일 트랜지스터 앰프 회로에서는 어렵습니다.

바이어싱

그림과 같이 2개의 "스택된" FET를 사용하는 캐스코드 회로는 2개의 FET에 몇 가지 제한을 가합니다.즉, 상부 FET는 소스 전압이 충분히 높아지도록 바이어스되어야 합니다(하위 FET 드레인 전압이 너무 낮아 포화 상태가 될 수 있습니다).FET에 대해 이 조건을 보증하려면 쌍에 대한 신중한 선택 또는 상부 FET 게이트의 특수 바이어싱이 필요하며, 이로 인해 비용이 증가한다.

캐스코드 회로는 바이폴라 트랜지스터(MOSFET) 또는 심지어 1개의 FET(또는 MOSFET)와 1개의 BJT를 사용하여 구축할 수도 있습니다.이러한 회로 배열은 VHF 텔레비전 튜너에서 진공관을 사용할 때 매우 흔했습니다.

이점

캐스코드 배열은 높은 게인, 높은 대역폭, 높은 슬루 레이트, 높은 안정성 및 높은 입력 임피던스를 제공합니다.2-트랜지스터 회로에 비해 부품 수가 매우 적습니다.

단점들

캐스코드 회로에는 2개의 트랜지스터가 필요하며 상대적으로 높은 공급 전압이 필요합니다.2-FET 캐스코드의 경우 양쪽 트랜지스터가 충분한 V로DS 바이어스되어 공급전압에 [citation needed]하한치를 가해야 합니다.

듀얼 게이트 버전

듀얼 게이트 MOSFET는 종종 "원 트랜지스터" 캐스코드로[citation needed] 기능합니다.민감 VHF 수신기의 프론트 엔드에서 공통으로 듀얼 게이트 MOSFET는 입력에 연결된 1차 게이트(일반적으로 MOSFET 제조업체에 의해 "게이트 1"로 지정됨)와 2차 게이트가 접지된(우회됨) 공통 소스 앰프로 작동합니다.내부적으로는 2개의 인접 게이트로 커버되는 채널이1개 있습니다.따라서 결과 회로는 전기적으로 2개의 FET로 구성된 캐스코드입니다.일반적인 저배수에서 상부 소스 접속은 2개의 게이트 사이의 경계에 물리적으로 인접한 단일 채널의 일부분일 뿐입니다.

슈퍼헤테로다인 리시버의 믹서

캐스코드 회로는 슈퍼헤테로다인 리시버에서의 멀티믹서 회로로서 매우 유용하다.하부 게이트에서는 RF 신호가 믹서에 공급되고 상부 게이트에서는 로컬 오실레이터 신호가 믹서에[citation needed] 공급됩니다.양쪽 신호를 믹서로 곱하여 캐스코드 믹서의 상부 드레인에서 차분 주파수인 중간 주파수를 취한다.

이것은 차동-증폭기 단계를 캐스케이드하여 균형잡힌 믹서를 형성하고 길버트 셀 이중균형[citation needed] 믹서를 형성함으로써 더욱 발전되었습니다.

기타 응용 프로그램

집적회로의 등장으로 트랜지스터는 실리콘 다이 면적으로 저렴해졌다.특히 MOSFET 기술에서는 캐스케이딩을 전류 미러에 사용하여 출력 전류원의 출력 임피던스를 높일 수 있습니다.

변경된 버전의 캐스코드는 변조기(특히 진폭 변조)로도 사용할 수 있습니다.상부 장치는 오디오 신호를 공급하고, 하부 장치는 RF 앰프 장치입니다.

캐스코드는 고전압 트랜지스터를 형성하기 위해 전압 래더와 조합해도 된다.입력 트랜지스터는 저U형일CEO 수 있지만, 스택형 선형 직렬 전압 조절기로 작동하는 다른 트랜지스터는 공급 전압의 상당 부분을 견딜 수 있어야 합니다.대규모 출력 전압 스윙의 경우 캐패시터에 의해 베이스 전압이 접지되지 않아야 하며 최상위 래더 저항은 최대 공급 전압을 견딜 수 있어야 합니다.이는 선형 직렬 전압 조절기가 실제로 입력 및 출력 지정이 스왑된 전류 버퍼임을 나타냅니다.

2포트 파라미터

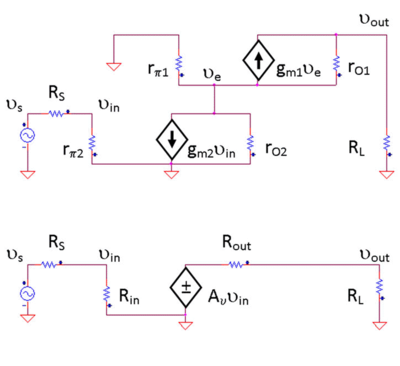

캐스코드 구성은 입력 임피던스, 출력 임피던스 및 전압 게인을 사용하여 단순 전압 증폭기(또는 보다 정확하게는 g 파라미터 2포트 네트워크)로 나타낼 수 있습니다.이러한 파라미터는 [5]아래의 대응하는 g 파라미터와 관련되어 있습니다.여기서 검토하지 않는 기타 유용한 속성은 회선 대역폭과 다이내믹 레인지입니다.

BJT cascode: 저주파 소신호 파라미터

이상화된 소신호 등가회로는 해당 주파수에서 단락회로로 동작할 수 있을 만큼 큰 전류원을 개방회로로, 캐패시터를 단락회로로 대체함으로써 회로에 대해 구성할 수 있습니다.BJT는 소형 신호 회로에 하이브리드 신호 [6]모델로 나타낼 수 있습니다.

| 정의. | 표현 | |

|---|---|---|

| 전압 게인 | ||

| 입력 저항 | ||

| 출력 저항 |

MOSFET cascode: 저주파 소신호 파라미터

마찬가지로 소신호 파라미터는 MOSFET 버전에 대해 도출할 수 있으며 MOSFET를 하이브리드 모델 등가로 대체할 수도 있습니다.이 도출은 MOSFET 게이트 전류가 0이므로 BJT의 작은 신호 모델이 기본 전류 0의 한계에서 MOSFET의 모델이 됨으로써 단순화할 수 있습니다.

| 정의. | 표현 | |

|---|---|---|

| 전압 게인 | ||

| 입력 저항 | ||

| 출력 저항 |

위의mO 공식에서 gr 요인의 조합이 자주 발생하므로 추가 검토를 요합니다.바이폴라 트랜지스터의 경우 이 제품은 다음과 같습니다(하이브리드 pi 모델 참조).

일반적인 이산 바이폴라 디바이스에서는 초기전압A V 100 100V, 실온 부근의 열전압은 VT 25 25mV로 gr 4000 4000은 비교적 큰 수치입니다mO.

Hybrid-pi 모델에 관한 기사에서 액티브모드에서의 MOSFET에 대해 알아보겠습니다.

65나노미터 기술노드인D I , 1.2mA/μ 폭에서 공급전압은 VDD = 1.1V, Vthov 165 165mV, V = V-VGSth 5 5%VDD 55 55mV이다.최소값의 2배인min L = 2 L = 0.130 μm, 표준값 ≈ μ 1/(4 V/μm L)을 취해도 1/10 2 2 V, grmO ≈ 110은 여전히 큰 [8][9]값이다.요점은 gr은 테크놀로지에 거의 관계없이 크기 때문에mO MOSFET와 바이폴라 캐스코드의 게인과 출력 저항이 매우 크다는 것입니다.그 사실은 이후의 논의에 함축되어 있다.

저주파 설계

위의 공식에서 발견된 g-파라미터는 원래 캐스코드(등가 회로)와 동일한 게인, 입력 및 출력 저항을 가진 작은 신호 전압 증폭기를 구성하는 데 사용할 수 있습니다.이 회로는 트랜지스터 기생 캐패시턴스가 중요하지 않을 정도로 낮은 주파수에서만 적용됩니다.그림에는 원래 캐스코드(그림 1)와 등가 전압 증폭기 또는 g 등가 2포트(그림 4)가 나와 있습니다.등가 회로를 사용하면 다양한 드라이버 및 부하에 대한 회로의 동작을 쉽게 계산할 수 있습니다.그림에서는 테베닌 저항S R의 테베닌 당량전압원이 증폭기를 구동하고 출력에는 간이부하저항L R이 부착되어 있다.등가 회로를 사용할 경우 앰프에 대한 입력 전압은 다음과 같습니다(분압기 참조).

- in= r R R +R \ ( \ } _ { { in } = { R _ { r _ { s + R _ { in \ { matrix} 、

이는 앰프에 들어가는 신호의 감쇠를 피하기 위해 RS < < R의in 저항을 가진 드라이버를 사용하는 것의 중요성을 나타냅니다.상기의 앰프 특성으로부터, MOSFET 캐스코드에 대해서 R은 무한하므로in, 그 경우 입력 신호의 감쇠는 발생하지 않습니다.R = r이므로in BJT 캐스코드가π2 더 제한적입니다.

마찬가지로 등가회로로부터의 출력신호는 다음과 같습니다.

저주파 회로에서는 일반적으로 고전압 게인이 바람직하기 때문에 부하에 도달하는 신호의 감쇠를 피하기 위해 저항 RL > > R의out 부하를 사용하는 것이 중요합니다.R의out 공식을 사용하여 부하에 비해 출력 저항이 충분히 작은 증폭기를 설계하거나, 그렇게 할 수 없는 경우 부하에 더 잘 맞는 전압 팔로어를 추가하는 등 수정된 회로를 결정할 수 있습니다.

이전 추정에서는 cascode 출력 저항이 매우 큰 것으로 나타났습니다.즉, 많은out 부하저항이 R>> R 조건을L 만족시키지 못한다는 것입니다(중요한 예외는 MOSFET를 부하로서 구동하는 것입니다).MOSFET는 무한한 저주파 입력 임피던스를 가집니다).단, cascode gain도 매우 크기 때문에 R > > Rout 조건을L 충족하지 못할 경우 치명적이지 않습니다.설계자가 의도하는 경우 큰 이득을 희생하여 낮은 부하 저항을 허용할 수 있습니다. R < < Rout >의 경우L 이득은 다음과 같이 단순해집니다.

- in {out}}}\약 A_{in}{\ {out {R_{fracfrac}}{L_Frac}}}{Frac}{Frac}}}{Frac}}}}}

이 이득은 단독으로 작동하는 입력 트랜지스터의 이득과 동일합니다.따라서 게인을 희생하더라도 캐스코드는 단일 트랜지스터 트랜지스터 트랜지던스 앰프와 동일한 게인을 발생시키지만 대역폭은 더 넓습니다.

증폭기는 대역폭이 넓기 때문에 로드 캐패시터가 연결되어 있을 때로드 저항기 []의 유무에 관계없이) 같은 방법으로 회로의 대역폭을 결정할 수 있습니다.필요한 가정은 부하 캐패시턴스가 충분히 커서 주파수 의존성을 제어하고 대역폭은 트랜지스터 자체의 무시된 기생 캐패시턴스에 의해 제어되지 않는다는 것입니다.

고주파 설계

고주파에서는 정확한 주파수 응답을 얻으려면 트랜지스터의 기생 캐패시턴스(게이트에서 드레인, 게이트에서 소스, 드레인에서 바디 및 바이폴라 등가물)를 하이브리드 모델 내에 포함해야 합니다.설계 목표는 또한 저주파 설계에 대해 위에서 설명한 바와 같이 전반적으로 높은 이득을 강조하는 것과는 다릅니다.고주파 회로에서는 신호 반사를 제거하고 전력 게인을 최대화하기 위해 일반적으로 앰프의 입출력 임피던스 매칭이 바람직합니다.캐스코드에서 입력 포트와 출력 포트 간의 격리는 여전히 작은 역방향 전송12 용어 g로 특징지어지며, 증폭기가 거의 일방적이기 때문에 일치하는 네트워크를 설계하기가 용이하다.

레퍼런스

- ^ Phillip A. Laplante (2005). Comprehensive Dictionary of Electrical Engineering (Second ed.). Boca Raton: CRC Press. p. 97. ISBN 0-8493-3086-6.

- ^ S. W. Amos; Roger S. Amos (2002). Newnes Dictionary of Electronics (Fourth ed.). Oxford: Newnes. pp. 46. ISBN 0-7506-4331-5.

- ^ Hunt, Frederick Vinton; Hickman, Roger Wayne (1939). "On Electronic Voltage Stabilizers" (PDF). Review of Scientific Instruments. 10 (1): 6. doi:10.1063/1.1751443. Retrieved 20 March 2016.

- ^ "Cathode Ray", "대역 III 수신을 위한 Cascode와 그 장점", Wireless World, vol. 61, 페이지 397(1955년 8월).

- ^ g-파라미터 2-포트에서 g는12 역전류 게인입니다.이러한 피드백이 발생하지 않을 경우 g = 0으로 네트워크는12 일방적이라고 불립니다.

- ^ Paul R. Gray; Paul J. Hurst; Stephen H. Lewis; Robert G. Meyer; et al. (2001). Analysis and Design of Analog Integrated Circuits (Fourth ed.). New York: Wiley. pp. 206–208. ISBN 0-471-32168-0.

- ^ Paul R. Gray; Paul J. Hurst; Stephen H. Lewis; Robert G. Meyer; et al. (2001). Analysis and Design of Analog Integrated Circuits (Fourth ed.). New York: Wiley. pp. 208–211. ISBN 0-471-32168-0.

- ^ R. Jacob Baker (2010). CMOS Circuit Design, Layout, and Simulation, Third Edition. New York: Wiley-IEEE. pp. 297–301. ISBN 978-0-470-88132-3.

- ^ W. M. C. Sansen (2006). Analog Design Essentials. Dordrecht: Springer. p. 13 (§0124). ISBN 0-387-25746-2.