커런트 미러

Current mirror커런트 미러란 회로의 다른 액티브 디바이스의 전류를 제어하고 부하에 관계없이 출력 전류를 일정하게 유지함으로써 하나의 액티브 디바이스를 통해 전류를 복사하도록 설계된 회로입니다.'복사'되는 전류는 다양한 신호 전류일 수 있으며, 때로는 그럴 수도 있습니다.개념적으로 이상적인 전류 미러는 단순히 전류 방향을 반전시키는 이상적인 반전 전류 증폭기입니다.또는 Current Controlled Current Source(CCCS; 전류 제어 소스)로 구성할 수도 있습니다.전류 미러는 회로에 바이어스 전류 및 활성 부하를 제공하는 데 사용됩니다.이상적인 전류 소스가 존재하지 않기 때문에 보다 현실적인 전류 소스를 모델링하는 데도 사용할 수 있습니다.

여기서 설명하는 회선 토폴로지는 많은 모노리식 IC에서 볼 수 있는 토폴로지입니다.팔로어(출력) 트랜지스터에 이미터 변성 저항이 없는 Widlar 미러입니다.이 토폴로지는 IC에서만 실행할 수 있습니다.이는 일치가 매우 가까워야 하고 디스켓에서는 달성할 수 없기 때문입니다.

또 다른 토폴로지는 Wilson 전류 미러입니다.윌슨 미러는 이 설계에서 초기 효과 전압 문제를 해결합니다.

전류 미러는 아날로그 회로와 혼합 VLSI 회로 모두에 적용됩니다.

미러 특성

현재의 미러를 특징짓는 세 가지 주요 사양이 있습니다.첫 번째는 전송비(전류 증폭기의 경우) 또는 출력 전류 크기(정전류 소스 CCS의 경우)입니다.두 번째는 AC 출력 저항으로, 미러에 인가되는 전압에 따라 출력 전류가 얼마나 변화하는지 결정합니다.세 번째 사양은 미러의 출력 부분에서 미러를 정상적으로 동작시키기 위해 필요한 최소 전압 강하입니다.이 최소 전압은 미러의 출력 트랜지스터를 활성 모드로 유지해야 하는 필요성에 따라 결정됩니다.미러가 동작하는 전압의 범위를 컴플라이언스 범위라고 하고, 양호한 동작과 나쁜 동작의 경계를 나타내는 전압을 컴플라이언스 전압이라고 합니다.또한 미러에는 온도 안정성 등 여러 가지 보조 성능 문제가 있습니다.

실제적인 근사치

소신호 분석의 경우 전류 미러는 동등한 노턴 임피던스로 근사할 수 있습니다.

대형 신호 손 분석에서 전류 미러는 일반적으로 이상적인 전류 소스에 의해 간단히 근사됩니다.그러나 이상적인 전류원은 다음과 같은 몇 가지 점에서 비현실적입니다.

- 그것은 무한 AC 임피던스를 가지고 있는 반면, 실용적인 거울은 유한 임피던스를 가지고 있다.

- 전압에 관계없이 동일한 전류를 공급합니다. 즉, 컴플라이언스 범위 요건이 없습니다.

- 실제 미러는 트랜지스터의 기생 용량으로 인해 한계가 있는 반면 주파수 제한이 없습니다.

- 이상적인 선원은 노이즈, 전원 전압의 변화, 컴포넌트 공차 등의 실제 영향에 대한 감도가 없습니다.

전류 미러의 회로 실현

기본 아이디어

바이폴라 트랜지스터는 가장 간단한 전류-전류 변환기로 사용할 수 있지만, 전송 비율은 온도 변화, β 공차 등에 따라 크게 달라집니다.이러한 바람직하지 않은 장애를 제거하기 위해 전류 미러는 동일한 조건에 배치되어 역특성을 갖는 2개의 계단식 전류-전압 및 전압-전류 변환기로 구성됩니다.선형이어야 하는 것은 아닙니다. 유일한 요구사항은 거울과 같은 특성입니다(예를 들어 아래의 BJT 전류 미러에서는 로그 및 지수).일반적으로 동일한 변환기를 2개 사용하지만 첫 번째 변환기의 특성은 네거티브 피드백을 적용함으로써 반전됩니다.따라서 전류 미러는 두 개의 계단식 등변환기(첫 번째 - 반전 및 두 번째 - 직접)로 구성됩니다.

기본 BJT 커런트 미러

BJT Base-Emiter 접합부에 입력량으로 전압이 인가되고 컬렉터 전류가 출력량으로 받아들여지면 트랜지스터는 지수 전압-전류 변환기 역할을 합니다.음의 피드백(단순히 베이스와 콜렉터를 결합)을 적용하면 트랜지스터가 "역전"될 수 있으며, 이제 적용된 "입력" 콜렉터 전류를 통과하도록 "출력" 베이스-이미터 전압을 조정합니다.

가장 단순한 바이폴라 전류 미러(그림 1 참조)가 이 아이디어를 구현합니다.2개의 캐스케이드 트랜지스터 스테이지가 그에 따라 역방향 및 직류 전압-전류 변환기 역할을 합니다.트랜지스터1 Q의 이미터는 접지에 연결되어 있습니다.그림과 같이 콜렉터 베이스 전압은 0입니다.이것에 의해, Q에1 걸친 전압 강하는 V, 즉BE 이 전압을 다이오드 법칙에 의해 설정해1, Q가 다이오드 접속되어 있다고 한다.('Evers-Moll 모델'도 참조).단순한 다이오드 대신 회로에 Q를 배치하는1 것이 중요합니다. 왜냐하면 Q는 트랜지스터2 Q에 V를 설정하기BE 때문입니다1.Q와2 Q가 일치할 경우1, 즉 실질적으로 동일한 디바이스 특성을 가지며, 미러 출력 전압이 선택되어2 Q의 컬렉터 베이스 전압도 0이 되면 Q에11[citation needed] 의해 설정된 V-값은BE Q의2 이미터 전류와 동일한 이미터 전류를 일치시킨Q에 발생시킵니다.Q와2 Q가 일치하기 때문에1 이들의 β0 값도 일치하므로 미러 출력 전류는 Q의1 수집기 전류와 동일합니다.

출력 트랜지스터의 임의 수집기 기반 역바이어스 V에CB 대해 미러에 의해 공급되는 전류는 다음과 같습니다.

여기서S I는 역포화 전류 또는 스케일 전류, V는T 열 전압, V는A 초기 전압입니다.이 전류는 다음과 같이 출력CB 트랜지스터 V = 0V일 때 기준 전류ref I와 관련이 있습니다.

Q의1 수집기 노드에서 키르히호프의 전류 법칙을 사용하여 찾을 수 있습니다.

기준 전류는 수집기 전류를 Q에1 공급하고 기준 전류를 두 트랜지스터에 모두 공급합니다. 두 트랜지스터의 베이스 전류가 0이면 두 베이스 전류가 같습니다(IB1 = IB2 = IB).

매개변수0 β는 V = 0 V에 대한CB 트랜지스터 β 값이다.

출력 저항

출력 트랜지스터2 Q에서 V가 0보다 크면BC 초기 효과로 인해 Q의2 수집기 전류가 Q보다1 다소 커집니다.즉, 미러에는 출력 트랜지스터의 r에o 의해 주어지는 유한한 출력(또는 노턴) 저항이 있습니다.즉, 다음과 같습니다.

여기서A V는 초기 전압이고 V는CE 출력 트랜지스터의 콜렉터 대 이미터 전압입니다.

컴플라이언스 전압

출력 트랜지스터를 활성 상태로 유지하려면 VCB 0 0V입니다.즉, 미러 동작을 올바르게 하는 가장 낮은 출력 전압인 준수 전압은 출력 전류C 레벨 I의 출력 트랜지스터와 V = 0V의CB 바이어스 조건에서 V = V이거나CVBE 위의 I-V 관계를 반전시키는 것입니다OUT.

여기서T V는 열전압이고 I는S 역포화 전류 또는 스케일 전류입니다.

확장 및 복잡성

Q가 VCB > 0 V이면2 트랜지스터는 더 이상 일치하지 않습니다.특히, 이들의 β 값은 초기 효과로 인해 다르다.

여기서A V는 초기 전압이고0 β는 V = 0V에 대한CB 트랜지스터 β입니다.초기 효과로 인한 차이 외에도 β0 값은 전류에 따라 달라지며, 두 트랜지스터는 이제 서로 다른 전류를 전달하기 때문에 트랜지스터 β 값은 달라집니다(Gummel-Poon 모델 참조).

또한 Q는 관련된 높은2 전력 소산에 의해 Q보다 상당히1 뜨거워질 수 있다.일치 상태를 유지하려면 트랜지스터의 온도가 거의 동일해야 합니다.두 트랜지스터가 같은 다이 상에 있는 집적회로 및 트랜지스터 어레이에서는 이를 달성하기 쉽습니다.그러나 두 트랜지스터가 크게 분리되면 전류 미러의 정밀도가 저하됩니다.

추가로 일치하는 트랜지스터를 동일한 베이스에 연결할 수 있으며 동일한 컬렉터 전류를 공급합니다.즉, R을 대체하는2 다양한 저항값으로 회로의 오른쪽 절반을 여러 번 복제할 수 있다.단, 오른쪽 절반 트랜지스터의 기본 전류가 0이 아니므로 추가 오른쪽 절반 트랜지스터는 Q에서 수집기1 전류를 "강제"합니다.그러면 프로그래밍된 전류가 약간 감소합니다.

미러 저항을 높이기 위해 이미터 변성이 있는 미러의 예도 참조하십시오.

다이어그램에 표시된 단순 미러의 경우β(\ \의 인 값은 1% 이상의 전류 일치를 생성합니다.

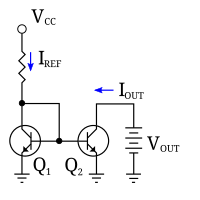

기본 MOSFET 전류 미러

그림 2와 같이 기본 전류 미러도 MOSFET 트랜지스터를 사용하여 구현할 수 있습니다.트랜지스터1 M은 포화 모드 또는 활성 모드로 동작하며, M도 마찬가지입니다2.이 설정에서는 출력 전류OUT I는 다음에 설명하듯이 I와 직접REF 관련이 있습니다.

MOSFETD I의 드레인 전류는 게이트 소스 전압과 MOSFET 장치의 기능에서 파생된 관계인 I = f(VGS, VDG)에D 의해 주어진 MOSFET의 드레인 대 게이트 전압의 함수입니다.미러의 트랜지스터1 M의 경우D I = IREF. 기준 전류REF I는 알려진 전류이며, 그림과 같이 저항을 통해 제공되거나 전압 공급 [1]변동과 무관하게 일정하게 유지되도록 "강화" 또는 "자체 바이어스" 전류 소스를 통해 제공될 수 있습니다.

트랜지스터1 M에 V = 0을 사용하면DG M의1 드레인 전류는 I = f(VGSGS, VDG=0)이므로DREF 다음과 같이 구하며, V의 값을GS 암시적으로 결정합니다.이렇게REF V의 값을GS 설정합니다.다이어그램의 회로는 트랜지스터2 M에 동일한GS V를 인가합니다.만약 M2또한 제로 VDG과 제공했다 편견을 가진 것은 M1과 M2채널 길이, 너비, 한계 값 전압 등은 관계 IOUT)f(VGS, VDG=0) IOUT)IREF 설정 적용된다 등의 속성., 출력 전류는 기준 전류와 같다 좋은 것 일치했을 때 VDG=0에 대한 출력 트랜지스터, 그리고. 둘 다 트랜지스터를 맞게 된다.e가 일치.

소스 드레인 전압은 V = VDG + V로GS 표시할DS 수 있습니다. 이 치환으로 시크만은 다음과 같습니다.Hodges 모델은 함수 fGS(VDG, V)[2]에 대한 대략적인 형식을 제공합니다.

서 Kp { K _ { }는 트랜지스터와 관련된 기술 관련 상수, W/L은 트랜지스터의 폭 대 길이 비율, S{ V_는 게이트 소스 전압, V { style 는 임계값 전압 및 변조 상수입니다. S는 드레인 소스 전압입니다.

출력 저항

채널 길이 변조 때문에 미러에는 출력 트랜지스터의 r에o 의해 주어지는 유한한 출력(또는 노턴) 저항이 있습니다(채널 길이 변조 참조).

여기서 λ = 채널 길이 변조 파라미터DS 및 V = 드레인 투 소스 바이어스입니다.

컴플라이언스 전압

출력 트랜지스터 저항을 높게 유지하려면 VDG [nb 1]0 0V입니다(베이커 [3]참조).즉, 올바른 미러 동작을 초래하는 최저 출력 전압인 준수 전압은 V = 0V인DG 출력CV 전류 레벨에서GS 출력 트랜지스터에 대해 V = V = V이거나OUT f-함수의 역수인 −1 f:

시크맨을 위해서...호지스 모형 f는−1 대략 제곱근 함수입니다.

내선번호 및 예약

이 미러의 유용한 특징은 장치 폭 W에 대한 f의 선형 의존성입니다. 이 비례는 시크만보다 더 정확한 모델에서도 대략적으로 충족됩니다.하지스 모델따라서 2개의 트랜지스터의 폭 비율을 조정함으로써 기준전류의 배수를 발생시킬 수 있다.

시크만-Hodges[4] 모델은 오늘날에도 단순히 편의상 사용되는 경우가 많지만 다소 오래된[when?] 기술에만 정확합니다.새로운 기술에 기초한[when?] 정량적 설계에서는 변경된 전류 전압 특성을 설명하는 장치에 컴퓨터 모델을 사용합니다.정확한 설계에서 설명되어야 하는 차이 중 하나는 전압 의존성에 대한 V의gs 제곱 법칙의 실패와 δV에ds 의해 제공되는 V 드레인 전압 의존성의 매우 낮은 모델링입니다ds.매우 중요한 공식의 또 다른 실패는 채널 길이 L에 대한 부정확한 의존성입니다. L-의존성의 유의한 원천은 Gray와 Meyer가 지적한 바와 같이 θ에서 비롯됩니다. 또한 θ는 보통 실험 데이터에서 [5]추출되어야 합니다.

특정 디바이스 번호 내에서도 V의th 편차가 크기 때문에 개별 버전이 문제가 됩니다.소스 퇴화 저항을 사용하여 변동을 어느 정도 보정할 수 있지만 값이 너무 커져서 출력 저항이 저하됩니다(즉, 감소).이 변동에 의해 MOSFET 버전은 IC/모놀리식 아레나에 관련지어집니다.

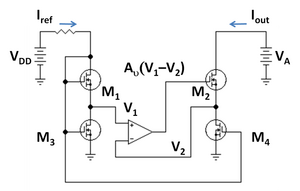

피드백 보조 전류 미러

그림 3은 출력 저항을 증가시키기 위해 음의 피드백을 사용하는 미러를 보여줍니다.op amp 때문에 이러한 회로를 게인 부스트 전류 미러라고 부르기도 합니다.준수 전압이 비교적 낮기 때문에 와이드스윙 전류 미러라고도 합니다.이 생각에 기초한 다양한 회로가 사용되고 있으며, 특히 MOSFET의 고유 출력 저항값이 낮기 때문에 MOSFET 미러에 사용됩니다.[6][7][8]그림 3의 MOSFET 버전은 그림 4에 나타나 있습니다.그림 3의 이미터 저항E R과 같은 역할을 하기 위해 MOSFET M과34 M은 오믹 모드로 동작하며 그림 3의 미러 트랜지스터1 Q 및 Q와2 같은 역할을 하며 MOSFET M과2 M은 액티브1 모드로 동작합니다.그림 3의 회로 구조에 대해 설명합니다.

OP 앰프에는 값E R의 두 이미터-레그 저항의 상단에서 전압1 V - V의2 차이가 공급됩니다.이 차이는 opamp에 의해 증폭되어 출력 트랜지스터2 Q의 베이스에 공급됩니다.인가전압A V를 증가시켜 Q에 대한2 컬렉터 베이스 역바이어스를 증가시키면 Q의2 전류가 증가하여 V가 증가하고2 Opamp로 들어가는 V - V가2 감소한다1.이것에 의해, Q의2 베이스 전압이 저하해BE, Q의2 V가 저하해 출력 전류의 증가에 대항한다.

op-amp 게인v A가 크면 매우 작은 V - V2 차이만 있으면1 Q에 필요한2 기본 전압B V를 생성할 수 있습니다.

이것에 의해, 2개의 레그 저항의 전류를 거의 같게 해, 미러의 출력 전류는 Q의1 컬렉터C1 전류 I와 거의 같게 해, 기준 전류에 의해 다음과 같이 설정된다.

여기서1 트랜지스터1 Q에 대한 β와2 Q에2 대한 β는2 Q의 컬렉터 베이스에 걸친 역바이어스가 0이 아닌 경우 Early 효과로 인해 다르다.

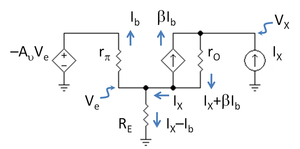

출력 저항

출력 저항의 이상적인 처리는 [nb 2]각주에 제시되어 있다.유한 이득v A를 가지지만 그 외에는 이상적인 Op A에 대한 작은 신호 분석은 그림 5에 기초한다(β, rO 및 r은π Q를 참조한다2).그림 5에 도달하려면 그림 3의 opamp의 양의 입력이 AC 접지에 있으므로 opamp에 대한 전압 입력은 단순히 음의 입력에 인가되는 AC 이미터 전압e V가 되고 입력 저항π 전체에 걸쳐 -Ave V의 전압 출력이 생성됩니다. 입력 저항에서 옴의 법칙을 사용하여 다음과 같이 작은 신호 기본 전류를b 결정합니다.

이 결과와 R R_})에 옴의을하면 V e({{e})를 제거할 수 있습니다.[nb 3]

테스트 소스X I에서 R의E 접지까지의 키르히호프의 전압 법칙은 다음을 제공합니다.

I를b 대체하고 항을 수집하면 출력 저항out R은 다음과 같습니다.

큰 게인v A µπ r / R의E 경우 이 회로를 통해 얻을 수 있는 최대 출력 저항은 다음과 같습니다.

R = r일O 때 기본out 거울에 비해 상당한 개선.

그림 4의 MOSFET 회로의 소립자 분석은 R의 공식에out βm = gπ r을 설정한 다음 r → µ로 하여π 양극성 분석에서 구한다.그 결과는

이 때 R은E 소스 레그 MOSFET3 M, M의4 저항입니다.단, 그림 3과 달리 A가 증가하면v(R이 고정값으로E 유지됨), R은out 계속 증가하며 큰v A에서는 제한값에 도달하지 않습니다.

컴플라이언스 전압

그림 3의 경우, 큰 opamp 게인은 작은E R만으로 최대out R을 달성합니다.R 값이E 작다는 것은 V가 작다는 것을2 의미하기 때문에 이 미러에 대해 낮은 컴플라이언스 전압을 허용할 수 있으며, 단순 바이폴라 미러의 컴플라이언스 전압보다2 큰 전압 V만 허용됩니다.이러한 이유로 이러한 유형의 미러는 와이드스윙 전류 미러라고도 불리는데, 이는 큰 컴플라이언스 전압을 희생해야만 큰 R을out 달성하는 다른 유형의 미러에 비해 출력 전압이 낮게 흔들릴 수 있기 때문입니다.

그림 4의 MOSFET 회로에서는 그림 3의 회로와 같이 opamp 게인v A가 클수록 주어진out R에서 R이 작아지고E 미러의 컴플라이언스 전압이 낮아집니다.

기타 전류 미러

기본 미러보다 출력 저항이 높고(출력 전압과 무관한 전류 출력을 가진 이상적인 미러에 더 가까이 접근) 온도 및 장치 파라미터 변동 및 회로 전압 변동에 덜 민감한 전류를 생성하는 정교한 전류 미러가 많이 있습니다.이러한 멀티 트랜지스터 미러 회로는 바이폴라 및 MOS 트랜지스터에 모두 사용됩니다.이러한 회로에는 다음이 포함됩니다.

메모들

- ^ 실제 MOSFET의 출력 저항은 활성 영역에 진입할 때만 증가하기 시작하여 V 0 0 V일 때만DG 최대값에 근접하기 때문에 출력 저항을 높게 유지하는 것은 MOSFET를 활성 모드로 유지하는 것 이상의 의미가 있습니다.

- ^ 무한 opamp 게인에 유효한 텍스트 내 인수의 이상적인 버전은 다음과 같습니다.op amp가 nullor로 대체되면 전압2 V = V이므로1 레그 저항의 전류는 동일한 값으로 유지됩니다.즉, 트랜지스터의 이미터 전류는 동일합니다.Q의2 V가CB 증가하면 초기 효과로 인해 출력 트랜지스터 β도0 증가합니다.β = β (1 + VCB / VA )따라서 β가 약간 증가하므로 I = IE / (β + 1)로 주어지는B Q에 대한 베이스2 전류가 감소하고 출력 전류out I = IE / (1 + 1 / β)가 약간 증가한다.계산을 해보니

- ^ Av → ,이므로e V → 0b, I → I입니다X.

「 」를 참조해 주세요.

레퍼런스

- ^ Paul R. Gray; Paul J. Hurst; Stephen H. Lewis; Robert G. Meyer (2001). Analysis and Design of Analog Integrated Circuits (Fourth ed.). New York: Wiley. p. 308–309. ISBN 0-471-32168-0.

- ^ Gray; et al. (27 March 2001). Eq. 1.165, p. 44. ISBN 0-471-32168-0.

- ^ R. Jacob Baker (2010). CMOS Circuit Design, Layout and Simulation (Third ed.). New York: Wiley-IEEE. pp. 297, §9.2.1 and Figure 20.28, p. 636. ISBN 978-0-470-88132-3.

- ^ NanoDotTek 보고서 NDT14-08-2007, 2007년 8월 12일 Wayback Machine에서 2012년 6월 17일 아카이브 완료

- ^ Gray; et al. (27 March 2001). p. 44. ISBN 0-471-32168-0.

- ^ R. Jacob Baker (7 September 2010). § 20.2.4 pp. 645–646. ISBN 978-0-470-88132-3.

- ^ Ivanov V. I., Filanovsky I. M. (2004). Operational amplifier speed and accuracy improvement: analog circuit design with structural methodology (The Kluwer international series in engineering and computer science, v. 763 ed.). Boston, Mass.: Kluwer Academic. p. §6.1, p. 105–108. ISBN 1-4020-7772-6.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ W. M. C. Sansen (2006). Analog design essentials. New York; Berlin: Springer. p. §0310, p. 93. ISBN 0-387-25746-2.

![{\displaystyle {\begin{aligned}I_{d}&=f(V_{GS},V_{DG})\\&={\frac {1}{2}}K_{p}\left({\frac {W}{L}}\right)\left(V_{GS}-V_{th}\right)^{2}\left(1+\lambda V_{DS}\right)\\&={\frac {1}{2}}K_{p}\left[{\frac {W}{L}}\right]\left[V_{GS}-V_{th}\right]^{2}\left[1+\lambda (V_{DG}+V_{GS})\right],\\\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d075d51269fe85fff8ace3eeccb118c918285ed3)

게이트 소스 전압, V

게이트 소스 전압, V

드레인 소스 전압입니다.

드레인 소스 전압입니다.

![{\displaystyle R_{\text{out}}=r_{O}\left[1+g_{m}R_{E}(A_{v}+1)\right]+R_{E}.}](https://wikimedia.org/api/rest_v1/media/math/render/svg/64ce933427c58ec5eb979a3664ccf4ff9048958c)