세라믹 콘덴서

Ceramic capacitor세라믹 콘덴서는 세라믹 재료가 유전체 역할을 하는 고정값 콘덴서입니다.두 개 이상의 세라믹 층과 전극 역할을 하는 금속 층으로 구성됩니다.세라믹 재료의 구성은 전기적 거동과 그에 따른 용도를 정의합니다.세라믹 캐패시터는 두 가지 애플리케이션 클래스로 나뉩니다.

- 클래스 1 세라믹 캐패시터는 공진 회로용으로 높은 안정성과 낮은 손실을 제공합니다.

- 클래스 2 세라믹 캐패시터는 버퍼, 바이패스 및 커플링 애플리케이션에 높은 체적 효율을 제공합니다.

세라믹 캐패시터, 특히 다층 세라믹 캐패시터(MLCC)는 연간 [1]약 1조 개의12 캐패시터를 사용하는 전자기기에서 가장 많이 생산되고 사용되는 캐패시터입니다.

특수한 형태와 스타일의 세라믹 캐패시터는 RFI/EMI 억제용 캐패시터, 피드 스루 캐패시터, 송신기용 전력 캐패시터로서 큰 사이즈로 사용됩니다.

역사

전기 비전도성 재료인 유리, 도자기, 종이, 운모가 절연체로 사용되었습니다.수십 년 후 이러한 재료는 첫 번째 콘덴서의 유전체로서 더 이상 사용하기에 적합했습니다.

마르코니의 무선 전송 장치의 초기에도, 자기 캐패시터는 송신기의 고전압 및 고주파 응용에 사용되었다.수신측에서는, 보다 작은 마이카 캐패시터가 공진 회로에 사용되었습니다.마이카 유전 콘덴서는 1909년 윌리엄 듀빌리에에 의해 발명되었다.제2차 세계대전 이전에는 운모가 미국에서 [1]가장 일반적인 콘덴서 유전체였습니다.

마이카는 천연 물질로 수량이 한정되어 있지 않습니다.그래서 1920년대 중반 독일에서 운모의 결핍과 특별한 종류의 도자기에 대한 경험으로 인해 독일에서 도자기를 유전체로 사용하는 최초의 콘덴서가 탄생하면서 새로운 세라믹 콘덴서 제품군이 탄생했습니다.최초의 세라믹 유전체로는 공진회로의 온도 보상에 대한 캐패시턴스의 선형 온도 의존성이 있고 마이카 캐패시터를 대체할 수 있기 때문에 파라유전체(루타일)가 사용되었습니다.1926년에 이러한 세라믹 콘덴서는 1940년대에 소량 생산되었고, 그 양은 증가하였다.이러한 초기 도자기의 스타일은 양면에 금속화가 주석 도금된 와이어와 접촉한 원반이었습니다.이 스타일은 트랜지스터보다 앞서 1930년대부터 1950년대까지 진공관 장비(예: 라디오 수신기)에 광범위하게 사용되었습니다.

그러나 이 부유전체는 상대적으로 유전율이 낮았기 때문에 작은 정전용량 값만 실현될 수 있었다.1930년대와 1940년대 무선 시장이 확대됨에 따라 HF 디커플링 애플리케이션의 전해 콘덴서보다 낮은 용량 값에 대한 수요가 생겼습니다.1921년에 발견된, 이산화티타늄이나 운모보다 약 10배 큰 1,000개의 유전율 범위의 강유전체 세라믹 재료인 티탄산바륨은 전자 [1][2]응용 분야에서 훨씬 더 큰 역할을 하기 시작했다.

유전율이 높을수록 캐패시턴스 값이 훨씬 높아지지만 이는 상대적으로 불안정한 전기 파라미터와 결합됩니다.따라서, 이러한 세라믹 캐패시터는 안정성이 덜 중요한 용도로만 일반적으로 사용되는 마이카 캐패시터를 대체할 수 있습니다.마이카 캐패시터에 비해 치수가 작고, 생산 비용이 낮아졌으며, 마이카 가용성에 대한 독립성이 높아짐에 따라 수용이 가속화되었습니다.

제2차 세계대전 이후 급속히 성장한 방송 산업은 결정학, 상변화, 세라믹 재료의 화학적, 기계적 최적화에 대한 이해를 심화시켰다.다양한 기본 재료의 복잡한 혼합을 통해 세라믹 콘덴서의 전기적 특성을 정밀하게 조정할 수 있습니다.세라믹 콘덴서의 전기적 특성을 구별하기 위해 표준화는 몇 가지 다른 애플리케이션 클래스(클래스 1, 클래스 2, 클래스 3)를 정의했습니다.전쟁 중과 이후 미국 및 유럽 시장에서의 개별 개발로 인해 이러한 등급의 정의가 서로 달랐으며 (EIA 대 IEC) 최근에야 (2010년 이후) IEC 표준화에 대한 세계적 조화가 이루어졌다.

1950년대부터 1970년대까지 전쟁 후 라디오 응용 프로그램에서 디스크 아래의 세라믹 콘덴서(당시 콘덴서라고 불림)의 전형적인 스타일은 내부와 외부 표면에 주석 또는 은으로 덮인 세라믹 튜브였다.여기에는 비교적 긴 단자가 저항기 및 기타 부품과 함께 개방 회로 배선의 뒤엉킨 형태를 형성하고 있습니다.

쉽게 성형할 수 있는 세라믹 재료는 고전압, 고주파(RF) 및 전력 용도에 적합한 특수하고 큰 스타일의 세라믹 캐패시터를 쉽게 개발할 수 있었습니다.

1950년대 반도체 기술의 발달로 장벽층 캐패시터 또는 IEC 클래스 3/EIA 클래스 IV 캐패시터가 도프된 강유전체 세라믹스를 사용하여 개발되었습니다.이 도프 소재는 다층 생산에는 적합하지 않았기 때문에 수십 년 후 Y5V 등급 2 캐패시터로 대체되었습니다.

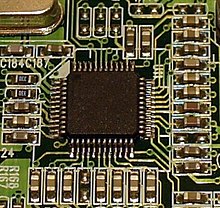

초기 스타일의 세라믹 디스크 캐패시터는 1950년대와 1970년대에 일반적인 세라믹 튜브 캐패시터보다 더 저렴하게 생산될 수 있었습니다.1961년 시작된 아폴로 계획의 한 가운데 있는 미국 회사가 여러 개의 디스크를 쌓아올려 단일 블록을 만들었다.이 "다층 세라믹 캐패시터"(MLCC)는 소형으로 대용량 [3]캐패시터를 제공했습니다.테이프 주조 및 세라믹-전극 코퍼링 공정을 사용하여 이러한 캐패시터를 생산하는 것은 제조상의 큰 과제였습니다.MLCC는 더 작은 케이스에서 더 큰 캐패시턴스 값을 필요로 하는 애플리케이션까지 적용 범위를 확장했습니다.이 세라믹 칩 캐패시터는 1980년대 전자 장치를 관통 구멍 장착에서 표면 장착 기술로 전환하는 원동력이었습니다.편광 전해 캐패시터는 편광되지 않은 세라믹 캐패시터로 교체할 수 있어 설치가 간단해집니다.

1993년 TDK는 팔라듐 베어링 전극을 훨씬 저렴한 니켈 전극으로 대체하는데 성공하여 생산 비용을 크게 절감하고 MLCC를 [4]대량 생산할 수 있게 되었다.

2012년 기준으로[update] 매년 [1]10개 이상의12 MLCC가 제조되고 있습니다.세라믹 칩 캐패시터의 스타일과 함께 세라믹 디스크 캐패시터는 전자파 간섭 억제 애플리케이션에서 안전 캐패시터로 자주 사용됩니다.이들 외에도 고전압 또는 고주파 송신기 애플리케이션용 대형 세라믹 전력 캐패시터도 발견됩니다.

세라믹 재료의 새로운 개발은 강유전체 세라믹으로 이루어졌다.이 재료는 비선형 반강유전체/강유전체 상변화를 통해 보다 높은 부피 효율로 에너지 저장을 늘릴 수 있습니다.에너지 저장(예: 기폭장치)[5]에 사용됩니다.

응용 프로그램 클래스, 정의

세라믹 콘덴서에 사용되는 다양한 세라믹 재료, 부전류 또는 강유전체 세라믹은 콘덴서의 전기적 특성에 영향을 미칩니다.이산화티타늄에 기초한 부전율 물질의 혼합물을 사용하면 지정된 온도 범위 내에서 캐패시턴스 값의 매우 안정적이고 선형적인 거동이 발생하며 고주파에서의 손실은 낮습니다.그러나 이러한 혼합물은 상대적으로 유전율이 낮기 때문에 이러한 캐패시터의 캐패시턴스 값이 상대적으로 작습니다.

세라믹 콘덴서의 캐패시턴스 값은 특정 산화물과 함께 티탄산바륨 등의 강유전체 재료를 혼합하여 얻을 수 있습니다.이러한 유전체 재료는 유전율이 훨씬 높지만 동시에 그 캐패시턴스 값은 온도 범위에 걸쳐 거의 비선형이며 고주파에서의 손실은 훨씬 높습니다.세라믹 콘덴서의 이러한 전기적 특성은 "어플리케이션 클래스"로 분류해야 합니다.응용 프로그램클래스의 정의는 표준화에서 유래합니다.2013년 현재, 국제 전기 표준 위원회(IEC)와 지금은 없어진 전자 산업 연합(EIA)의 두 가지 표준 세트가 사용되고 있습니다.

두 가지 표준에서 주어진 애플리케이션 클래스의 정의는 다릅니다.다음 표는 세라믹 캐패시터에 대한 응용 프로그램 클래스의 다양한 정의를 보여줍니다.

| 에 관한 정의 IEC/EN 60384-1 및 IEC/EN 60384-8/9/21/22 | 에 관한 정의 EIA RS-198 |

|---|---|

| 클래스 1 세라믹 콘덴서 는 공진 회로 애플리케이션에 높은 안정성과 낮은 손실을 제공합니다. | 클래스 I(또는 기입 클래스 1) 세라믹 콘덴서 공진 회로 응용에 높은 안정성과 낮은 손실을 제공하다 |

| 클래스 2 세라믹 콘덴서 높은 체적 효율을 제공하다 스무딩, 바이패스, 커플링 및 디커플링 애플리케이션용 | 클래스 II(또는 쓰기 클래스 2) 세라믹 콘덴서 용량 변화가 -15% ~ +15% 미만이고 온도 범위가 -55°C ~ +125°C 이상일 때 높은 체적 효율을 제공합니다. 스무딩, 바이패스, 커플링 및 디커플링 애플리케이션용 |

| 클래스 3 세라믹 콘덴서 더 이상 표준화되지 않은 배리어 레이어 캐패시터입니다. | 클래스 III(또는 쓰기 클래스 3) 세라믹 콘덴서 는 EIA 클래스 II보다 부피 효율이 높고 10°C~55°C의 낮은 온도 범위에서 용량 변경률이 -22%~+56%입니다. EIA 클래스 2 - Y5U/Y5V 또는 Z5U/Z5V 캐패시터로 대체할 수 있습니다. |

| - | 클래스 IV(또는 기입 클래스 4) 세라믹 콘덴서 더 이상 표준화되지 않은 배리어 레이어 캐패시터입니다. |

특히 미국의 제조업체들은 Electronic Industries Alliance(EIA) 표준을 선호했습니다.IEC 표준과 매우 유사한 많은 부분에서 EIA RS-198은 세라믹 콘덴서에 [6]대한 4가지 애플리케이션 클래스를 정의합니다.

양 규격의 클래스 번호가 다르기 때문에,[7][8] 많은 제조사의 데이터 시트에 기재되어 있는 클래스 기술을 오해하고 있습니다.EIA는 2011년 2월 11일에 운영을 중단했지만, 이전 부문은 국제 표준화 기구에 계속 서비스를 제공하고 있습니다.

다음에서는 IEC 표준의 정의가 선호되며 중요한 경우에는 EIA 표준의 정의와 비교된다.

클래스 1 세라믹 콘덴서

클래스 1 세라믹 캐패시터는 정확하고 온도를 보상하는 캐패시터입니다.전압, 온도 및 주파수가 가장 안정적입니다.이들 회로는 손실이 가장 낮기 때문에 안정성이 필수적이거나 회로에 대한 온도 효과를 보상하는 등 정확하게 정의된 온도 계수가 필요한 공진 회로 애플리케이션에 특히 적합합니다.1급 세라믹 콘덴서의 기본 재료는 이산화티타늄(TiO

2)과 같은 미세 분쇄된 부전해 물질의 과립을 혼합하여 구성되며, 이는 콘덴서가 원하는 선형 [9][10]특성을 달성하기 위해 필요한 아연, 지르코늄, 니오비움, 마그네슘, 탄탈, 코발트 및 스트론튬의 첨가물에 의해 변형됩니다.

클래스 1 캐패시터의 일반적인 캐패시턴스 온도 동작은 기본 부전율 재료(예

2: TiO)에 따라 달라집니다.화학 조성의 첨가제는 원하는 온도 특성을 정확하게 조절하기 위해 사용됩니다.클래스 1 세라믹 캐패시터는 세라믹 캐패시터 중 부피 측정 효율성이 가장 낮습니다.이는 부전율 소재의 유전율이 상대적으로 낮기 때문입니다(6~200).따라서 클래스 1 캐패시터는 낮은 범위의 캐패시턴스 값을 가집니다.

| 화학- 공식 | 상대 유전율 ε | 온도- 계수α 10−6/K |

|---|---|---|

| MgNb2O6 | 21 | −70 |

| ZnNBO26 | 25 | −56 |

| MgTa2O6 | 28 | 18 |

| ZnTa2O6 | 38 | 9 |

| (ZnMg)TiO3 | 32 | 5 |

| (ZrSn)TiO4 | 37 | 0 |

| Ba2Ti9O20 | 40 | 2 |

클래스 1의 콘덴서는 일반적으로 온도와 상당히 선형적인 온도 계수를 가지고 있습니다.이러한 콘덴서는 약 0.15%의 소산 계수로 매우 낮은 전기적 손실을 보입니다.이들은 중대한 에이징 프로세스를 거치지 않으며 캐패시턴스 값은 인가 전압과 거의 독립적입니다.이러한 특성을 통해 공진 회로 및 발진기(예를 들어 위상 잠금 루프 회로)에서 고Q 필터를 적용할 수 있습니다.

EIA RS-198 표준은 세라믹 클래스 1 캐패시터를 온도 계수를 나타내는 3자 코드로 코드합니다.첫 번째 문자는 온도(온도계수α)에 대한 캐패시턴스 변화를 ppm/K 단위로 나타냅니다.두 번째 문자는 온도 계수의 승수를 나타냅니다.세 번째 문자는 ppm/K 단위의 최대 공차를 제공합니다.모든 정격은 25 ~85 °C입니다.

| 온도계수α 10−6/K 레터 코드 | 승수 온도 계수의 번호 코드 | 공차 ppm/K 온도 계수의 레터 코드 |

|---|---|---|

| C: 0.0 | 0: −1 | G: ±30 |

| B: 0.3 | 1: −10 | 높이: ±60 |

| L: 0.8 | 2: −100 | J: ±120 |

| 답: 0.9 | 3: −1000 | K: ±250 |

| M: 1.0 | 5: +1 | L: ±500 |

| P: 1.5 | 6: +10 | M: ±1000 |

| R: 2.2 | 7: +100 | N: ±2500 |

| S: 3.3 | 8: +1000 | |

| T: 4.7 | ||

| V: 5.6 | ||

| U: 7.5 |

EIA 코드와 더불어 클래스 1 세라믹 콘덴서의 용량 의존성의 온도 계수는 일반적으로 "NP0", "N220" 등과 같은 세라믹 이름으로 표시됩니다.이러한 이름에는 온도 계수(α)가 포함됩니다.IEC/EN 60384-8/21 표준에서는 온도계수와 공차는 대응하는 EIA 코드가 추가된 두 자리 문자 코드(표 참조)로 대체됩니다.

| 세라믹스 이름 | 온도 계수α 10−6/K | α-공차 10−6/K | 서브- 학급 | IEC/EN- 편지 코드 | EIA 편지 코드 |

|---|---|---|---|---|---|

| P100 | 100 | ±30 | 1B | AG | M7G |

| NP0 | 0 | ±30 | 1B | CG | C0G |

| N33 | −33 | ±30 | 1B | HG | H2G |

| N75 | −75 | ±30 | 1B | LG | L2G |

| N150 | −150 | ±60 | 1B | PH | P2H |

| N220 | −220 | ±60 | 1B | 오른쪽 | R2H |

| N330 | −330 | ±60 | 1B | SH | S2H |

| N470 | −470 | ±60 | 1B | TH | T2H |

| N750 | −750 | ±120 | 1B | UJ | U2J |

| N1000 | −1000 | ±250 | 1층 | QK | Q3K |

| N1500 | −1500 | ±250 | 1층 | VK | P3K |

예를 들어, EIA 코드가 "C0G"인 "NP0" 캐패시터는 0 드리프트, 허용 오차는 ±30ppm/K, 코드 "P3K"인 "N1500"은 -1500ppm/K 드리프트, 최대 허용 오차는 ±250ppm/°C입니다.IEC 및 EIA 캐패시터 코드는 산업 캐패시터 코드이며 군용 캐패시터 코드와 동일하지 않습니다.

클래스 1 콘덴서는 온도계수α가 다른 콘덴서를 포함한다.특히 α±0•10−6/K, α 허용 오차가 30ppm인 NP0/CG/C0G 캐패시터는 기술적으로 매우 중요하다.이러한 콘덴서는 -55 ~ +125°C의 온도 범위에서 ±0.54%의 정전용량 변동을 가집니다.이를 통해 광범위한 온도 범위(예: 공진 회로)에서 정확한 주파수 응답을 실현할 수 있습니다.특수 온도 거동을 가진 다른 재료는 발진기 회로의 코일처럼 병렬로 연결된 구성 요소의 카운터 온도 실행을 보상하는 데 사용됩니다.클래스 1 캐패시터는 정격 캐패시턴스의 공차가 매우 작습니다.

- 다른 등급 1 세라믹 콘덴서의 이상적인 곡선 및 온도 계수의 공차 범위 표현α

클래스 2 세라믹 콘덴서

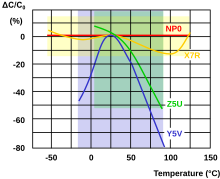

클래스 2 세라믹 캐패시터는 유전율이 높고 따라서 클래스 1 캐패시터보다 체적 효율이 우수하지만 정확도와 안정성은 낮습니다.세라믹 유전체는 온도 범위에 걸쳐 캐패시턴스의 비선형 변화를 특징으로 합니다.캐패시턴스 값도 인가 전압에 따라 달라집니다.이들은 바이패스, 커플링 및 디커플링 애플리케이션 또는 낮은 손실과 높은 캐패시턴스의 안정성이 덜 중요한 주파수 식별 회로에 적합합니다.일반적으로 마이크로포니를 나타냅니다.

클래스 2 캐패시터는 티탄산바륨(BaTiO

3)과 같은 강유전체 재료와 규산알루미늄, 규산마그네슘 및 산화알루미늄과 같은 적절한 첨가물로 제조됩니다.이러한 세라믹은 높은 유전율에서 매우 높은 유전율(200~14,000)을 가지며, 이는 전계 강도에 따라 달라집니다.따라서 클래스 2 콘덴서의 캐패시턴스 값은 비선형입니다.적용되는 온도와 전압에 따라 달라집니다.또한 클래스 2 캐패시터는 시간이 [9]지남에 따라 에이징됩니다.

단, 높은 유전율은 소형 디바이스에서 높은 캐패시턴스 값을 지원합니다.클래스 2 캐패시터는 동일한 정격의 캐패시턴스 및 전압에서 클래스 1 장치보다 훨씬 작습니다.예를 들어 전원 공급 장치의 버퍼링 및 필터링, 전기 신호의 커플링 및 디커플링 등 캐패시터가 캐패시턴스의 최소값만을 유지해야 하는 애플리케이션에 적합합니다.

클래스 2 캐패시터는 온도 범위에 따른 캐패시턴스 변화에 따라 라벨이 부착됩니다.가장 널리 사용되는 분류는 EIA RS-198 표준에 기초하고 있으며 3자리 코드를 사용합니다.첫 번째 문자는 로우엔드의 동작 온도를 나타내는 문자입니다.두 번째 문자는 하이엔드 작동 온도를 나타내고 마지막 문자는 해당 온도 범위에 걸쳐 캐패시턴스 변화를 나타냅니다.

| 레터 코드 저온 | 번호 코드 상한 온도 | 레터 코드 정전 용량 변화 온도 범위를 넘어서 |

|---|---|---|

| X = -55 °C(-67 °F) | 4 = +65 °C (+165 °F) | P = ±10 % |

| Y = -30 °C(-22 °F) | 5 = +85 °C (+185 °F) | R = ±15 % |

| Z = +10 °C(+50 °F) | 6 = +105 °C (+221 °F) | L = ±15%, +15/-40% (125°C[11] 이상) |

| 7 = +125 °C (+257 °F) | S = ±22% | |

| 8 = +150 °C (+302 °F) | T = +22/-33% | |

| 9 = +200 °C (+392 °F) | U = +22/-56% | |

| V = +22/-82% |

예를 들어 Z5U 캐패시터는 +10°C에서 +85°C까지 작동하며 캐패시턴스 변화는 최대 +22%에서 -56%까지입니다.X7R 캐패시터는 -55°C에서 +125°C까지 작동하며 캐패시턴스 변화는 최대 ±15%입니다.

일반적으로 사용되는 클래스 2 세라믹 콘덴서 재료는 다음과 같습니다.

- X8R (-55/+150, δC/C0 = ±15%)

- X7R(-55/+125°C, δC/C0 = ±15%)

- X6R (-55/+105 °C, δC/C0 = ±15 %)

- X5R(-55/+85°C, δC/C0 = ±15%)

- X7S(-55/+125, δC/C0 = ±22%)

- Z5U(+10/+85°C, δC/C0 = +22/-56%)

- Y5V(-30/+85°C, δC/C0 = +22/-82%)

IEC/EN 60384-9/22 규격에서는 다른 두 자리 코드를 사용합니다.

| 캐패시턴스 변경 코드 | 최대 캐패시 δC0/C at U = 0 | 최대 캐패시 δC0N/C = U | 온도 범위 코드 | 온도 범위 |

|---|---|---|---|---|

| 2B | ±10% | +10/−15% | 1 | -55 ~ +125 °C |

| 2C | ±20% | +20/−30% | 2 | -55 ~ +85 °C |

| 이차원 | +20/−30% | +20/−40% | 3 | -40 ~ +85 °C |

| 2E | +22/−56% | +22/−70% | 4 | -25 ~ +85 °C |

| 2층 | +30/−80% | +30/−90% | 5 | (-10 … +70) °C |

| 2R | ±15% | − | 6 | +10 … +85 °C |

| 2배 | ±15% | +15/−25% | - | - |

대부분의 경우 EIA 코드를 IEC/EN 코드로 변환할 수 있습니다.약간의 번역 에러가 발생하지만, 통상은 허용됩니다.

- X7R은 2X1과 상관

- Z5U는 2E6와 상관

- 2F4와 유사한 Y5V, 수차: δC/C0 = +30/-82%가 아닌 +30/-80%

- 2C1과 유사한 X7S, 수차: ±22%가0 아닌 δC/C = ±20%

- X8R IEC/EN 코드 없음

클래스 2 세라믹 캐패시터는 캐패시턴스 정확도와 안정성이 낮기 때문에 높은 내성이 필요합니다.

군사 타입의 경우 클래스 2 유전체는 온도 특성(TC)을 지정하지만 온도 전압 특성(TVC)은 지정하지 않습니다.X7R과 마찬가지로 밀리터리 타입 BX는 온도에 따라 15% 이상 변동할 수 없습니다.또, 최대 정격 전압에서는 +15 %/-25% 이내를 유지할 필요가 있습니다.타입 BR의 TVC 제한은 +15%/-40%입니다.

클래스 3 세라믹 콘덴서

클래스 3 장벽층 또는 반도체 세라믹 캐패시터는 최대 50,000개의 매우 높은 유전율을 가지며, 따라서 클래스 2 캐패시터보다 부피 효율성이 우수합니다.그러나 이러한 콘덴서는 정확도와 안정성이 떨어지는 등 전기적 특성이 더 나빠집니다.유전체는 온도 범위에 걸쳐 매우 높은 비선형 캐패시턴스 변화로 특징지어집니다.캐패시턴스 값은 인가되는 전압에 따라 추가로 달라집니다.또한, 그들은 시간이 지남에 따라 매우 높은 손실과 나이를 가지고 있다.

장벽층 세라믹 캐패시터는 티탄산바륨(BaTiO

3)과 같은 도프된 강유전체 재료로 만들어집니다.1980년대 중반 이 세라믹 기술이 발전함에 따라 장벽층 캐패시터가 최대 100µF까지 사용 가능해졌으며, 당시에는 더 작은 전해 캐패시터를 대체할 수 있을 것으로 보였다.

이 재료로는 다층 캐패시터를 구축할 수 없기 때문에 시장에는 납 단층 타입만 제공됩니다.[12] [13]

2013년 현재[update] 배리어 레이어 캐패시터는 더 이상 사용되지 않는 것으로 간주됩니다. 현대의 클래스 2 다층 세라믹은 보다 콤팩트한 패키지로 더 높은 용량과 더 나은 성능을 제공할 수 있기 때문입니다.따라서 이러한 콘덴서는 IEC에 의해 표준화되지 않습니다.

구조 및 스타일

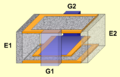

- 세라믹 콘덴서의 기본 구조

세라믹 캐패시터는 부유전체 또는 강유전체 재료의 미세 분쇄된 과립을 다른 재료와 적절히 혼합하여 원하는 특성을 달성합니다.이들 분말혼합물 중에서 세라믹은 고온에서 소결된다.세라믹은 유전체를 형성하고 금속 전극의 캐리어 역할을 합니다.오늘(2013년) 저전압 캐패시터의 경우 0.5마이크로미터[3] 크기 범위에 있는 유전체층의 최소 두께는 세라믹 분말의 입자 크기에 따라 아래쪽으로 제한됩니다.전압이 높은 캐패시터의 유전체 두께는 원하는 캐패시터의 유전체 강도에 따라 결정됩니다.

캐패시터의 전극은 금속화에 의해 세라믹 층에 퇴적됩니다.MLCC의 경우 금속화된 세라믹 층을 번갈아 적층한다.본체 양쪽에 있는 전극의 뛰어난 금속화는 접촉 단자에 연결됩니다.래커 또는 세라믹 코팅은 습기 및 기타 주변 영향으로부터 캐패시터를 보호합니다.

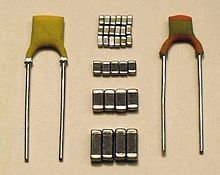

세라믹 콘덴서는 다양한 모양과 스타일로 제공됩니다.가장 일반적인 예는 다음과 같습니다.

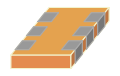

- 표면 실장용 다층 세라믹 칩 캐패시터(MLCC), 직사각형 블록

- 세라믹 디스크 캐패시터, 단층 디스크, 수지 코팅, 관통 구멍 리드 포함

- 고주파 회로에서 바이패스 목적으로 사용되는 피드스루 세라믹 캐패시터.튜브 모양, 납과 접촉하는 내부 금속화, 납땜을 위한 외부 금속화

- 세라믹 전원 캐패시터, 다양한 형태의 대형 세라믹 본체, 고전압 애플리케이션용

- 전자 장비에 사용되는 일부 다른 스타일의 세라믹 캐패시터

다층 세라믹 콘덴서(MLCC)

제조 공정

- 다층 세라믹 칩 캐패시터

MLCC는 여러 개의 개별 캐패시터를 병렬로 쌓아 단자 표면을 통해 접촉합니다.모든 MLCC 칩의 시작 재료는 정밀하게 분쇄된 파라유전체 또는 강유전체 원료 과립의 혼합물로, 정확하게 결정된 [14][15]첨가물에 의해 변형됩니다.이 가루들은 균일하게 혼합되어 있다.혼합물의 성분과 분말 입자의 크기가 10 nm에 달한다는 것은 제조사의 전문 지식을 반영합니다.

분말의 현탁액에서 적절한 바인더를 사용하여 얇은 세라믹 포일을 주조한다.이 호일은 운반용으로 감겨져 있다.다시 롤을 풀면 동일한 크기의 시트로 잘라 금속 페이스트로 화면을 인쇄합니다.이 시트는 전극이 됩니다.자동화된 프로세스에서 이러한 시트는 필요한 수의 층으로 쌓이고 압력에 의해 굳어집니다.상대 유전율 외에 층의 크기와 수에 따라 이후의 캐패시턴스 값이 결정됩니다.전극은 인접한 층에서 약간 오프셋된 교대 배열로 적층되어 있어 나중에 각각 오프셋 측(왼쪽, 오른쪽)에 연결될 수 있습니다.적층된 스택을 누른 후 개별 구성요소로 절단합니다.예를 들어 크기가 "0201"(0.5mm × 0.3mm)인 500개 이상의 층을 생산하려면 높은 기계적 정밀도가 필요합니다.

절삭 후 바인더는 스택에서 연소됩니다.그 후 1,200~1,450°C의 온도에서 소결하여 최종, 주로 결정 구조를 생성합니다.이 굽기 프로세스는 원하는 유전 특성을 생성합니다.소각 후 양단면을 청소하고 금속화한다.금속화를 통해 단부와 내부 전극이 병렬로 연결되어 캐패시터가 단자를 얻습니다.마지막으로 전기값의 100% 측정을 실시하여 제조장치에서의 자동처리를 위한 테이핑을 실시한다.

소형화

MLCC 콘덴서의 캐패시턴스 공식(C)은 레이어 수에 따라 강화된 플레이트 콘덴서의 공식에 기초하고 있습니다.

여기서 θ는 유전 유전율, A는 전극 표면적을, n은 층수를, d는 전극 사이의 거리를 나타낸다.

유전체가 얇거나 전극 면적이 클수록 정전용량 값이 커지며 유전율이 높은 유전체 재료도 커집니다.

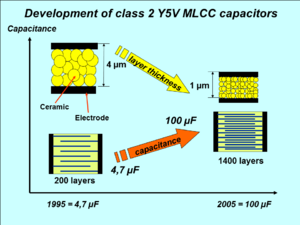

최근 수십 년 동안 디지털 전자제품의 점진적인 소형화에 따라 집적 논리회로 주변의 부품들도 축소되었습니다.MLCC를 축소하려면 유전체 두께를 줄이고 층 수를 늘려야 합니다.두 옵션 모두 엄청난 노력이 필요하며 많은 전문 지식과 연결되어 있습니다.

1995년에 유전체의 최소 두께는 4µm였다.2005년까지 일부 제조업체는 층 두께가 1µm인 MLCC 칩을 생산했습니다.2010년 현재[update] 최소 두께는 약 0.5µm이다.[1]유전체의 전계 강도가 35V/µm로 [16]증가했습니다.

이러한 콘덴서의 크기를 줄임으로써 세라믹 층을 얇게 만드는 가정인 분말 입자 크기를 줄일 수 있습니다.또, 제조 공정을 보다 정밀하게 제어할 수 있게 되어, 한층 더 많은 층을 쌓을 수 있게 되었습니다.

1995년과 2005년 사이 사이즈가 1206인 Y5V MLCC 캐패시터의 캐패시턴스는 4.[17]7μF에서 100μF로 증가했습니다.한편 (2013년) 많은 생산업체가 칩 크기 0805에서 [18]100μF의 용량 값을 가진 클래스 2 MLCC 캐패시터를 공급할 수 있습니다.

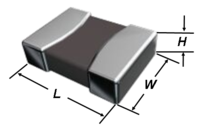

MLCC 케이스 사이즈

MLCC에는 리드가 없기 때문에 보통 리드를 가진 경쟁사보다 크기가 작습니다.PCB에 장착할 때 관통 구멍에 접근할 필요가 없으며 사람이 아닌 기계로 처리하도록 설계되었습니다.그 결과 MLCC와 같은 표면 실장 컴포넌트는 일반적으로 가격이 저렴합니다.

MLCC는 동등한 취급을 위해 표준화된 모양과 크기로 제조됩니다.초기 표준화는 미국 EIA 표준이 주도했기 때문에 MLCC 칩의 치수는 EIA에 의해 인치 단위로 표준화되었습니다.길이가 0.06인치, 폭이 0.03인치인 직사각형 칩은 "0603"으로 코딩됩니다.이 코드는 국제적이며 일반적으로 사용됩니다.JEDEC(IEC/EN)는 두 번째 메트릭 코드를 고안했습니다.EIA 코드와 멀티레이어 세라믹 칩 캐패시터의 일반적인 사이즈에 상당하는 메트릭과 치수를 다음 표에 나타냅니다.표에서 누락된 것은 높이 "H"의 측정값입니다.MLCC 칩의 높이는 레이어 수와 캐패시턴스에 따라 달라지기 때문에 일반적으로 여기에 기재되어 있지 않습니다.단, 일반적으로 높이 H는 폭 W를 넘지 않습니다.

| 그림그리기 | EIA 인치 코드 | 치수 가로×세로 인치 × 인치 | IEC/EN 미터법 코드 | 치수 가로×세로 mm × mm | EIA 인치 코드 | 치수 폭×폭 인치 × 인치 | IEC/EN 미터법 코드 | 치수 가로×세로 mm × mm | |

|---|---|---|---|---|---|---|---|---|---|

| 01005 | 0.016 × 0.0079 | 0402 | 0.4 × 0.2 | 1806 | 0.18 × 0.063 | 4516 | 4.5 × 1.6 | ||

| 015015 | 0.016 × 0.016 | 0404 | 0.4 × 0.4 | 1808 | 0.18 × 0.079 | 4520 | 4.5 × 2.0 | ||

| 0201 | 0.024 × 0.012 | 0603 | 0.6 × 0.3 | 1812 | 0.18 × 0.13 | 4532 | 4.5 × 3.2 | ||

| 0202 | 0.02 × 0.02 | 0505 | 0.5 × 0.5 | 1825 | 0.18 × 0.25 | 4564 | 4.5 × 6.4 | ||

| 0302 | 0.03 × 0.02 | 0805 | 0.8 × 0.5 | 2010 | 0.20 × 0.098 | 5025 | 5.0 × 2.5 | ||

| 0303 | 0.03 × 0.03 | 0808 | 0.8 × 0.8 | 2020 | 0.20 × 0.20 | 5050 | 5.08 × 5.08 | ||

| 0504 | 0.05 × 0.04 | 1310 | 1.3 × 1.0 | 2220 | 0.225 × 0.197 | 5750 | 5.7 × 5.0 | ||

| 0402 | 0.039 × 0.020 | 1005 | 1.0 × 0.5 | 2225 | 0.225 × 0.25 | 5664/5764 | 5.7 × 6.4 | ||

| 0603 | 0.063 × 0.031 | 1608 | 1.6 × 0.8 | 2512 | 0.25 × 0.13 | 6432 | 6.4 × 3.2 | ||

| 0805 | 0.079 × 0.049 | 2012 | 2.0 × 1.25 | 2520 | 0.25 × 0.197 | 6450 | 6.4 × 5.0 | ||

| 1008 | 0.098 × 0.079 | 2520 | 2.5 × 2.0 | 2920 | 0.29 × 0.197 | 7450 | 7.4 × 5.0 | ||

| 1111 | 0.11 × 0.11 | 2828 | 2.8 × 2.8 | 3333 | 0.33 × 0.33 | 8484 | 8.38 × 8.38 | ||

| 1206 | 0.126 × 0.063 | 3216 | 3.2 × 1.6 | 3640 | 0.36 × 0.40 | 9210 | 9.2 × 10.16 | ||

| 1210 | 0.126 × 0.10 | 3225 | 3.2 × 2.5 | 4040 | 0.4 × 0.4 | 100100 | 10.2 × 10.2 | ||

| 1410 | 0.14 × 0.10 | 3625 | 3.6 × 2.5 | 5550 | 0.55 × 0.5 | 140127 | 14.0 × 12.7 | ||

| 1515 | 0.15 × 0.15 | 3838 | 3.81 × 3.81 | 8060 | 0.8 × 0.6 | 203153 | 20.3 × 15.3 |

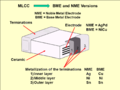

NME 및 BME 금속화

- 금속화가 X7R 세라믹 다층 칩 캐패시터의 전압 의존성에 미치는 영향

1990년대 말 다층 세라믹 칩 캐패시터 생산에서 특히 문제가 된 것은 전극과 단자에 사용되는 금속의 가격 상승이었습니다.원래 선택지는 1200~1400°C의 높은 소결 온도를 견딜 수 있는 산화되지 않는 귀금속 은과 팔라듐이었습니다.NME(Noble Metal 전극)라고 불리며 클래스 2 캐패시터에 매우 우수한 전기적 특성을 제공했습니다.이러한 금속의 가격 상승은 콘덴서 가격을 크게 증가시켰다.

비용 압박으로 인해 훨씬 저렴한 니켈과 [19]구리를 사용한 BME(Base Metal Electrode)가 개발되었습니다.

그러나 BME 금속화는 다른 전기적 특성을 생성했습니다. 예를 들어 X7R 캐패시터의 전압 의존성이 크게 증가했습니다(그림 참조).BME 메탈라이제이션에 의해 클래스 2 세라믹 콘덴서의 손실률과 임피던스 거동도 감소했습니다.

클래스 2 세라믹 캐패시터의 경우, 일반적으로 전기적 성질의 안정성에 그다지 중요하지 않은 용도에서의 사용으로 인해, NME 금속화는 클래스 1 세라믹 캐패시터에서 유지되는 반면, 이러한 부정적인 변화는 비용상의 이유로 시장에서 최종적으로 받아들여졌습니다.

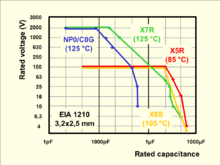

MLCC 캐패시턴스 범위

MLCC 칩의 캐패시턴스는 유전체, 크기 및 필요한 전압(정격 전압)에 따라 달라집니다.캐패시턴스 값은 약 1pF에서 시작합니다.최대 캐패시턴스 값은 생산 기법에 따라 결정됩니다.47 µF인 X7R의 경우, Y5V의 경우: 100 µF.

그림 오른쪽은 클래스 1 및 클래스 2 다층 세라믹 칩 캐패시터의 최대 캐패시턴스를 나타냅니다.세라믹 NP0/C0G 및 X7R에 대한 다음 두 표는 각 일반적인 케이스 크기에 대해 주요 제조업체인 Murata, TDK, KEMET, AVX의 최대 가용 캐패시턴스 값과 정격 전압을 나열합니다(2017년 4월 상태).

| 정격- 전압 | 케이스 사이즈, EIA 코드 | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 01005 | 0201 | 0402 | 0603 | 0805 | 1206 | 1210 | 1812 | 2220 | |

| 치수(mm) | |||||||||

| 0.4×0.2 | 0.6×0.3 | 1.0×0.5 | 1.6×0.8 | 2.0×1.25 | 3.2×1.6 | 3.2×2.5 | 4.5×3.2 | 5.7×5.0 | |

| 최대 용량 | |||||||||

| 6.3 V | 220 pF | – | – | 33nF | – | – | – | – | – |

| 10 V | 220 pF | – | 4.7nF | 33nF | 100 nF | 100 nF | 220nF | – | – |

| 16 V | 220 pF | – | 2.2nF | 15nF | 47 nF | 120 nF | 220nF | – | – |

| 25 V | 220 pF | 1.0nF | 2.2nF | 47 nF | 47 nF | 120 nF | 220nF | – | – |

| 50 V | 100pF | 220 pF | 1.5nF | 10 nF | 47 nF | 100 nF | 150nF | 220nF | 470 nF |

| 100 V | – | 100pF | 1.0nF | 4.7nF | 22nF | 100 nF | 100 nF | 150nF | 330 nF |

| 250 V | – | – | 330pF | 2.2nF | 8.2nF | 22nF | 47 nF | 100 nF | – |

| 500 V | – | – | – | – | 820 pF | 4.7nF | 10 nF | 22nF | 47 nF |

| 630 V | – | – | – | – | 1.2nF | 4.7nF | 15nF | 22nF | 47 nF |

| 1000 V | – | – | – | – | 270 pF | 1.0nF | 2.7nF | 5.6nF | 12 nF |

| 2000 V | – | – | – | – | – | 270 pf | 680 pF | 1.5nF | 3.9nF |

| 3000 V | – | – | – | – | – | – | – | 390 pF | 1.0nF |

| 정격- 전압 | 케이스 사이즈, EIA 코드 | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 01005 | 0201 | 0402 | 0603 | 0805 | 1206 | 1210 | 1812 | 2220 | |

| 치수(mm) | |||||||||

| 0.4×0.2 | 0.6×0.3 | 1.0×0.5 | 1.6×0.8 | 2.0×1.25 | 3.2×1.6 | 3.2×2.5 | 4.5×3.2 | 5.7×5.0 | |

| 최대 용량 | |||||||||

| 4 V | – | – | 2.2 µF | 2.2 µF | 22°F | 100°F | 100°F | – | – |

| 6.3 V | – | 0.1 µF | 2.2 µF | 10°F | 22°F | 47°F | 100°F | – | – |

| 10 V | 1.0nF | 0.1 µF | 2.2 . F | 10°F | 22°F | 22°F | 47°F | – | – |

| 16 V | 1.0nF | 0.1 µF | 2.2 µF | 4.7 µF | 10°F | 22°F | 22°F | – | – |

| 25 V | – | 10 nF | 0.1 µF | 2.2 µF | 10°F | 10°F | 22°F | – | 22°F |

| 50 V | – | 1.5nF | 0.1 µF | 0.47°F | 4.7 µF | 4.7 µF | 10°F | – | 10°F |

| 100 V | – | – | 4.7nF | 0.1 µF | 0.1 µF | 4.7 µF | 10°F | 3.3 µF | 10°F |

| 200 V | – | – | – | 10 nF | 56nF | 0.15°F | 0.22°F | 1.0 µF | 1.0 µF |

| 250 V | – | – | – | 2.2nF | 22nF | 0.1 µF | 0.22°F | 0.47°F | 1.0 µF |

| 500 V | – | – | – | 3.9nF | 22nF | 68 nF | 0.1 µF | 0.22°F | 0.47°F |

| 630 V | – | – | – | 1.5nF | 12 nF | 33nF | 0.1 µF | 0.15°F | 0.33°F |

| 1000 V | – | – | – | 1.0nF | 4.7nF | 22nF | 68 nF | 0.1 µF | 0.12°F |

| 2000 V | – | – | – | – | – | 2.2nF | 6.8nF | 10 nF | 22nF |

| 3000 V | – | – | – | – | – | – | – | 1.2nF | 15nF |

저ESL 스타일

- 다양한 MLCC 설계 비교

공진 주파수 영역에서 콘덴서는 노이즈 또는 전자파 간섭에 대해 최적의 디커플링 특성을 가집니다.콘덴서의 공진 주파수는 컴포넌트의 인덕턴스에 의해 결정됩니다.콘덴서의 유도 부품은 동등한 직렬 인덕턴스(ESL)로 요약됩니다(L은 인덕턴스의 전기 기호입니다).인덕턴스가 작을수록 공진 주파수는 높아집니다.

특히 디지털 신호 처리에서는 스위칭 주파수가 계속 증가하고 있기 때문에 고주파 디커플링 또는 필터 캐패시터에 대한 수요가 증가하고 있습니다.간단한 설계 변경으로 MLCC 칩의 ESL을 줄일 수 있습니다.따라서 적층전극은 종단접속과 함께 종방향으로 접속된다.이로 인해 전하 캐리어가 전극 위를 흐르는 거리가 줄어들어 [20]컴포넌트의 인덕턴스가 감소합니다.

예를 들어 X7R의 사이즈가 0.1µF이고, 공진 주파수가 약 16MHz인 경우 칩이 세로 측에 종단부가 있는 0508 사이즈의 경우 약 22MHz로 증가한다.

또 다른 방법은 디바이스를 콘덴서 배열로 형성하는 것입니다.여기에서는, 복수의 개별 캐패시터가 공통의 하우징에 짜넣어져 있습니다.병렬로 연결하면 구성 요소의 ESL 및 ESR 값이 감소합니다.

X2Y 디커플링 콘덴서

- X2Y 디커플링 콘덴서

표준 다층 세라믹 콘덴서는 내부에 2개의 외부 종단부가 접속된 다수의 대향 전극층을 적층한다.그러나 X2Y 세라믹 칩 캐패시터는 4단자 칩 디바이스입니다.칩에 내장된 세 번째 실드 전극 세트를 사용하여 쌓은 세라믹 층 중 표준 2단자 MLCC와 같이 구성됩니다.이러한 실드 전극은 캐패시터 플레이트 스택 내의 각 기존 전극을 둘러싸고 있으며 캐패시터 종단까지 2개의 추가 측면 종단부를 통해 저오믹 접촉합니다.X2Y 구조에서는 3노드의 커패시티브 회선이 형성되어 라인 투 라인 [21][22][23]및 라인 투 그라운드필터링을 동시에 제공합니다.

X2Y 세라믹 캐패시터는 2개 이상의 기존 장치를 교체할 수 있어 디지털 회로의 공급 전압에 대한 고주파 필터링 또는 노이즈 억제에 이상적이며, 자동차, 오디오, 센서 [24][25]및 기타 애플리케이션에서 DC 모터의 엄격한 EMC 요구 사항을 충족하는 데 매우 유용합니다.

X2Y 풋프린트로 인해 마운트 인덕턴스가 [26]낮아집니다.이것은 특히 클럭 레이트가 100MHz 이상인 고속 디지털 회선에서의 사용에 관심이 있습니다.여기서 회로기판의 개별 공급전압의 디커플링은 공급라인의 기생인덕턴스로 인해 실현하기 어렵습니다.기존 세라믹 캐패시터를 사용하는 표준 솔루션에서는 캐패시턴스 값이 다른 많은 기존 MLCC 칩을 병렬로 사용해야 합니다.여기서 X2Y 캐패시터는 [27]PCB에서 최대 5개의 동일한 크기의 세라믹 캐패시터를 교체할 수 있습니다.그러나 이 특정 유형의 세라믹 콘덴서는 특허가 있기 때문에 이들 부품은 여전히 비교적 고가입니다.

X2Y 캐패시터 대신 3단자 [28]캐패시터를 사용할 수 있습니다.

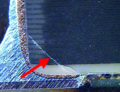

기계적 감수성

세라믹 재료는 [29]부서지기 쉽다.표면 실장 컴포넌트로서의 MLCC 칩은 기판에 직접 실장되기 때문에 굴곡 응력에 취약합니다.프린트 회로 기판(PCB)의 납땜 조인트 사이에 끼여, 진동이나 범프가 회로 기판에 영향을 주는 경우 등, 기계적 응력에 노출되는 경우가 많습니다.또한 납 컴포넌트보다 열응력에 더 민감합니다.과도한 납땜 필릿 높이는 이러한 응력을 증가시켜 칩 균열을 일으킬 수 있습니다.기계적 충격을 일으키는 모든 영향 요인 중에서 PCB에 대한 응력이 가장 중요한 [30]것으로 나타났습니다.그 이유는 이러한 응력에 의해 유도되는 힘이 PCB 및 납땜 조인트를 통해 구성 요소에 거의 감쇠되지 않은 상태로 전달되기 때문입니다.

- MLCC 칩 – 올바르게 장착됨 – 칩 균열 – 기판 굽힘 테스트

기계적 응력에 견딜 수 있는 MLCC 칩의 능력은 이른바 기판 굽힘 테스트에 의해 테스트됩니다.여기서 2개의 지지점 사이에 납땜된 MLCC 칩을 가진 테스트 PCB를 1~3mm의 경로 길이로 펀치에 의해 구부린다.경로 길이는 응용 프로그램에서 나오는 요건에 따라 달라집니다.균열이 나타나지 않으면 캐패시터는 원하는 요건을 견딜 수 있습니다.균열은 일반적으로 단락 또는 편향된 상태의 캐패시턴스 값 변화에 의해 감지됩니다.

MLCC 칩의 굽힘 강도는 세라믹의 특성, 칩의 크기 및 캐패시터의 설계에 따라 다릅니다.특별한 설계 특징이 없는 NP0/C0G 클래스 1 세라믹 MLCC 칩은 일반적인 굽힘 강도는 2mm에 달하지만, 더 큰 유형의 X7R, Y5V 클래스 2 세라믹 칩은 약 1mm의 굽힘 강도에 불과합니다.0402와 같은 작은 칩은 모든 유형의 세라믹에서 더 큰 굽힘 강도 값에 도달했습니다.

특수 설계 특징, 특히 전극의 특수 설계 및 종단에 의해 굽힘 강도를 향상시킬 수 있습니다.예를 들어 내부 단락은 반대 극성을 가진 두 전극의 접촉에 의해 발생하며, 이 전극은 종단 영역의 세라믹 차단 시 생성됩니다.전극의 겹치는 표면이 줄어들면 이를 방지할 수 있습니다.이것은 예를 들어 "Open Mode Design"(OMD)에 의해 실현됩니다.여기서는 종단 영역이 끊어지면 캐패시턴스 값이 약간 감소합니다(AVX, KEMET).

- 기계적 응력을 최소화하기 위한 다양한 MLCC 구조

"Flex-Termination" - MLCC 칩, 유연한 접점 층으로 [31]세라믹 파손을 방지합니다.

"플로팅 전극 설계"(FED) 또는 "다층 직렬 캐패시터"(MLSC)라고 하는 유사한 구조에서도 캐패시터 본체의 일부가 파손된 경우에만 캐패시턴스가 감소합니다.이 구조는 종단부에 대한 전도성 연결 없이 부유 전극으로 작동합니다.브레이크는 단락으로 이어지지 않고 정전용량 감소로 이어집니다.단, 두 구조 모두 동일한 캐패시턴스 값을 가진 표준 MLCC 버전에 비해 더 큰 설계로 이어집니다.

표준 MLCC와 관련하여 동일한 부피는 전극과 "Flexible Termination"(FT-Cap) 또는 "Soft Termination"(소프트 터미네이션)이라고 불리는 종단 사이에 전도성 폴리머의 유연한 중간층을 도입함으로써 달성됩니다.이 구조에서는 강성 금속납땜접합부가 가요성 고분자층에 반대하여 이동할 수 있으므로 [32]세라믹이 파손되지 않고 굽힘력을 흡수할 수 있다.

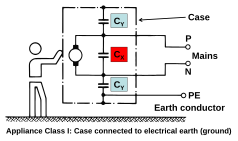

X- 및 Y 콘덴서에 의한 RFI/EMI 억제

억제 캐패시터는 주파수가 증가함에 따라 전기적 임피던스가 감소하기 때문에 효과적인 간섭 저감 컴포넌트입니다.따라서 주파수가 높을수록 전기적 노이즈와 라인 간 또는 접지에 단락됩니다.이 때문에, 기기나 기계(모터, 인버터, 전자 밸러스트, 솔리드 스테이트 릴레이 스너버, 스파크 퀀처등)가 전자파나 무선 주파수의 간섭을 송수신 하는 것은 물론, 회선간(X 캐패시터) 접속 및 회선간(Y 캐패시터) 접속의 과도현상을 방지할 수 있습니다.X 콘덴서는 대칭, 균형 또는 차등 간섭을 효과적으로 흡수합니다.Y 캐패시터는 라인 위상과 제로 전위점 사이에 라인 바이패스로 접속되어 비대칭, 언밸런스 또는 커먼 모드 [33][34][35]간섭을 흡수합니다.

- X 캐패시터 및 Y 캐패시터를 사용한 RFI/EMI 억제(안전절연 미포함 및 추가 안전절연 포함)

EMI/RFI 억제 캐패시터는 EMC 지침 EN 50081의 [36]한계를 초과하지 않도록 설계되었습니다.억제 구성요소는 10~20년 이상 주 전압에 직접 연결되므로 잠재적으로 손상되는 과전압 및 과도 전압에 노출됩니다.이러한 이유로 억제 콘덴서는 다음과 같은 국제 안전 표준의 안전 및 비발화성 요건을 준수해야 합니다.

- 유럽: EN 60384-14,

- 미국: UL 1414, UL 1283

- 캐나다: CSA C22.2, No.1, CSA C22.2, No.8

- 중국: CQC (GB/T 14472-1998)

지정된 모든 요건을 충족하는 RFI 캐패시터에는 다양한 국가 안전 표준 기관의 인증 마크가 각인되어 있습니다.전원 라인 애플리케이션의 경우, 콘덴서 본체를 함침 또는 코팅하는 코팅 및 에폭시 수지의 비인화성에 대한 특별한 요구사항이 있습니다.안전승인을 받기 위해 X 및 Y 전원라인 정격의 콘덴서는 고장날 때까지 파괴적으로 테스트됩니다.대규모 과전압 서지에 노출되어도 이러한 안전 등급의 콘덴서는 인력이나 재산을 위험에 빠트리지 않는 페일 세이프 방식으로 고장나야 합니다.

2012년 현재[update] EMI/RFI 억제에 사용되는 대부분의 세라믹 캐패시터는 PCB에 [37][38]스루홀을 장착하기 위한 리드 캐패시터였습니다. 표면 실장 기술은 점점 더 중요해지고 있습니다.이러한 이유로 최근 몇 년 동안 여러 제조업체로부터 EMI/RFI 억제를 위한 많은 MLCC 칩이 승인을 받았으며 해당 [37][39][40][41][42]표준에 명시된 모든 요건을 충족하고 있습니다.

세라믹 전원 콘덴서

- 다양한 스타일의 전력 전자용 세라믹 콘덴서

대형 전력 세라믹 콘덴서에 사용되는 재료는 대부분 소형 전력에 사용되는 재료와 매우 유사하지만 전력 시스템, 송신기 및 전기 설비에 사용되는 고전압 또는 전압 정격을 가진 세라믹 콘덴서는 역사적 이유로 별도로 분류되는 경우가 많습니다.저전력을 위한 세라믹 콘덴서의 표준화는 전기 및 기계적인 매개변수를 전자 장비에 사용하는 구성 요소로서 지향하고 있습니다.이와는 반대로 전력 콘덴서의 표준화는 현지 규제 당국에 의해 주어진 인력과 기기의 보호에 중점을 두고 있습니다.

최신 전자 기기가 이전에는 "전기 전력" 부품의 독점적 영역이었던 전력 수준을 처리할 수 있는 능력을 획득함에 따라, "전자"와 "전기" 전력 정격의 구분이 덜 명확해졌습니다.과거에는 이 두 제품군의 경계가 약 200볼트 암페어의 무효 전력이었지만, 현대의 전력 전자 제품은 증가하는 전력량을 처리할 수 있습니다.

파워 세라믹 콘덴서는 대부분 200볼트암페어보다 훨씬 높은 전압으로 규정되어 있습니다.세라믹 원료의 뛰어난 가소성과 세라믹의 높은 유전 강도는 많은 용도에 대한 솔루션을 제공하며, 파워 세라믹 캐패시터 제품군의 스타일이 매우 다양한 이유이기도 합니다.이 전력 콘덴서는 수십 년 동안 시판되어 왔습니다.안정성이 높고 손실이 적은 1등급 전력 세라믹 캐패시터 또는 부피 측정 효율성이 높은 2등급 전력 세라믹 캐패시터 요구 사항에 따라 생산됩니다.

클래스 1 파워 세라믹 캐패시터는 송신국에서의 공진회로 응용에 사용됩니다.클래스 2 전력 세라믹 캐패시터는 회로 차단기, 배전 라인, 레이저 애플리케이션의 고전압 전원, 유도로 및 전압 이중 회로에 사용됩니다.전력 세라믹 캐패시터는 2kV ~ 100kV [43]범위의 높은 정격 전압으로 공급될 수 있습니다.

이러한 파워 세라믹 콘덴서의 치수는 매우 클 수 있습니다.고출력 애플리케이션에서는 이러한 콘덴서의 손실로 인해 많은 열이 발생할 수 있습니다.이러한 이유로 일부 특수 스타일의 파워 세라믹 캐패시터는 수냉용 파이프를 갖추고 있습니다.

전기적 특성

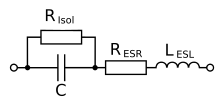

직렬 등가 회로

세라믹 캐패시터의 모든 전기적 특성은 캐패시터의 모든 손실 및 유도 파라미터를 모델링하는 이상적인 캐패시턴스와 추가 전기 컴포넌트로 구성된 직렬 등가 회로에 의해 정의 및 지정될 수 있습니다.이 직렬 등가 회로에서 콘덴서의 전기적 특성은 다음과 같이 정의됩니다.

- C, 콘덴서의 캐패시턴스,

- Rinsul, 유전체의 절연 저항, 하우징의 절연과 혼동하지 말 것

- R은ESR 캐패시터의 모든 ohmic 손실을 요약하는 등가 직렬 저항이며, 일반적으로 "ESR"로 약칭됩니다.

- L은 등가 직렬 인덕턴스로, 일반적으로 "ESL"로 약칭되는 캐패시터의 유효 자기 유도입니다ESL.

병렬 등가 회로 대신 직렬 등가 회로의 사용은 IEC/EN 60384-1에 정의되어 있습니다.

캐패시턴스 표준값 및 공차

"정격 캐패시턴스" CR 또는 "공칭 캐패시턴스" C는N 캐패시터가 설계된 값입니다.실제 캐패시턴스는 측정 주파수와 주변 온도에 따라 달라집니다.콘덴서에 대한 표준화된 조건은 20°C의 온도에서 다음과 같은 주파수로 저전압 AC 측정 방법입니다.

- 클래스 1 세라믹 콘덴서

- 1MHz에서R 100pF 이하, 측정전압 5V

- 1kHz에서R C > 100pF, 측정전압 5V

- 클래스 2 세라믹 콘덴서

- 1MHz에서R 100pF 이하, 전압 1V 측정

- 100 pF < CR ≤ 10 µF (1 kHz에서), 측정 전압 1 V

- 100R/120Hz에서 C > 10 µF, 측정전압 0.5V

콘덴서는 IEC/EN 60063에 명시된 E 시리즈 표준에 명시된 대로 기하학적으로 증가하는 다양한 선호 값으로 사용할 수 있습니다.10년당 값 수에 따라 이들은 E3, E6, E12, E24 시리즈라고 불립니다.콘덴서 값을 지정하는 데 사용되는 단위에는 피코파라드(pF), 나노파라드(nF), 마이크로파라드(θF) 및 패러드(F)가 모두 포함됩니다.

정격값에서 캐패시턴스의 허용 편차의 백분율을 캐패시턴스 허용 오차라고 합니다.실제 캐패시턴스 값은 허용 한계 내에 있어야 합니다. 그렇지 않으면 캐패시터가 사양을 벗어납니다.좁은 공간에서의 생략 표시의 경우, 각 공차의 문자 코드가 IEC/EN 60062에 규정되어 있다.

| E시리즈 | 공차 | |||

|---|---|---|---|---|

| CR > 10 pF | 레터 코드 | CR < 10 pF | 레터 코드 | |

| E96 | 1% | F | 0.1pF | B |

| E48 | 2% | G | 0.25pF | C |

| E24 | 5% | J | 0.5pF | D |

| E12 | 10% | K | 1pF | F |

| E6 | 20% | M | 2pF | G |

| E3 | −20/+50% | S | - | - |

| −20/+80% | Z | - | - | |

필요한 캐패시턴스 허용 오차는 특정 용도에 따라 결정됩니다.E24 ~ E96의 좁은 공차는 정밀 오실레이터 및 타이머와 같은 회로의 고품질 클래스 1 캐패시터에 사용됩니다.중요하지 않은 필터링 또는 커플링 회로와 같은 애플리케이션의 경우, 클래스 2 캐패시터의 경우 E12부터 E3까지의 공차 시리즈로 충분합니다.

캐패시턴스의 온도 의존성

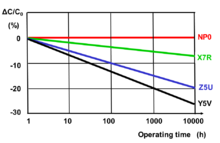

세라믹 콘덴서의 캐패시턴스는 온도에 따라 달라집니다.많은 콘덴서 타입의 다른 유전체는 온도 의존성에 큰 차이를 보입니다.온도 계수는 클래스 1 세라믹 캐패시터의 경우 섭씨 당ppm(ppm) 단위로, 클래스 2 캐패시터의 경우 총 온도 범위에서 백분율(%)로 표시됩니다.

| 콘덴서의 종류 유전체 재료 | 온도 계수 C/C0 | 어플 온도 범위 |

|---|---|---|

| 세라믹 콘덴서 클래스 1 부전율 NP0 | ±30ppm/K(±0.5%) | −55…+125 °C |

| 세라믹 콘덴서 클래스 2, 강유전체 X7R | ±15% | −55…+125 °C |

| 세라믹 콘덴서 클래스 2, 강유전체 Y5V | +22% / −82% | −30…+85 °C |

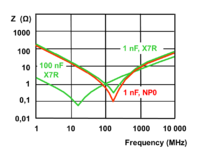

캐패시턴스의 주파수 의존성

대부분의 개별 콘덴서 유형은 주파수가 증가함에 따라 커패시턴스 변화가 크거나 작습니다.2등급 세라믹 및 플라스틱 필름의 유전 강도는 주파수가 증가함에 따라 감소합니다.따라서 주파수가 증가함에 따라 캐패시턴스 값이 감소합니다.이 현상은 유전율의 주파수 의존성의 원인이 전기 쌍극자의 시간 상수가 되는 유전체 이완과 관련이 있습니다.오른쪽에 있는 그래프는 클래스 2 캐패시터와 클래스 1 캐패시터의 일반적인 주파수 동작을 나타냅니다.

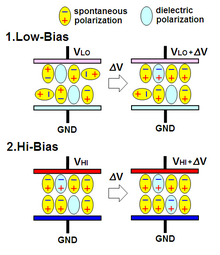

캐패시턴스의 전압 의존성

세라믹 캐패시터의 캐패시턴스도 인가 전압에 따라 변경될 수 있습니다.이 효과는 클래스 2 세라믹 캐패시터에서 더 많이 나타납니다.강유전체 재료는 인가된 [44][45]전압에 따라 달라집니다.인가 전압이 높을수록 유전율이 낮아집니다.더 높은 전압으로 측정되거나 인가되는 정전용량은 표준 측정 전압 0.5 또는 1.0V로 측정된 값의 -80%까지 떨어질 수 있습니다.이 동작은 저왜곡 필터 및 기타 아날로그 애플리케이션에서 비선형성의 작은 원인입니다.오디오 어플리케이션에서는 이것이 고조파 왜곡의 원인이 될 수 있습니다.

- 일부 등급 2 세라믹 캐패시터에 대한 캐패시턴스의 전압 의존성

위의 두 그림에서 캐패시턴스의 전압 의존성은 NME 금속화를 사용한 세라믹 캐패시터의 곡선을 보여줍니다.BME 메탈라이제이션이 있는 캐패시터의 경우 캐패시턴스의 전압 의존성이 크게 [46][47][48][49]증가했습니다.

전압 프루프루프

대부분의 콘덴서의 경우 일반적으로 각 유전체 재료 및 두께에 대해 물리적 조건의 유전체 강도 또는 파괴 전압을 지정할 수 있습니다.세라믹 캐패시터에서는 이 작업이 불가능합니다.세라믹 유전체층의 파괴 전압은 전극 재료 및 세라믹의 소결 조건에 따라 최대 10배까지 달라질 수 있습니다.오늘날 매우 얇은 세라믹 층의 전기적 특성 산란을 지정된 한계 내에서 유지하려면 프로세스 매개변수의 높은 정밀도와 제어가 필요합니다.

세라믹 콘덴서의 전압 증명은 정격 전압(UR)으로 지정됩니다.이는 상한 온도까지 캐패시터에 연속적으로 인가할 수 있는 최대 DC 전압입니다.이 보증 전압 방지는 옆 표에 표시된 전압에 따라 테스트됩니다.

또한 정기적인 수명 테스트(내구성 테스트)에서 세라믹 캐패시터의 전압 증명을 테스트 전압(U의 120R~150%)을 높여 테스트하여 안전한 구성을 보장합니다.

| 스타일. | 정격 전압 | 테스트 전압 |

|---|---|---|

| 세라믹스- 다층 작은 조각 콘덴서 (MLCC) | UR 100 100 V | 2.5UR |

| 100 V < UR 200 200 V | 1.5 UR + 100 V | |

| 200 V < UR 500500 V | 1.3UR + 100V | |

| 500 V < UR | 1.3UR | |

| 단일 레이어- 세라믹 콘덴서 | UR 500 500 V | 2.5UR |

| UR > 500 V | 1.5 UR + 500 V |

임피던스

콘덴서의 주파수 의존형 AC 저항은 Z(\ Z라고 하며, AC 회로에서 전압 대 전류의 복잡한 비율입니다.임피던스는 옴의 법칙 개념을 AC 회로로 확장하며, 규모만 있는 저항과 달리 특정 주파수에서 규모와 위상을 모두 소유합니다.

임피던스는 콘덴서가 교류 전류를 통과할 수 있는 능력을 측정하는 것입니다.이러한 의미에서 임피던스는 옴의 법칙처럼 사용될 수 있습니다.

전류 또는 전압의 피크 또는 유효값을 계산합니다.

콘덴서의 직렬 등가 회로에 나타나듯이 실제 구성 요소에는 이상적인 콘덴서 C), L L)및 저항 R이 포함됩니다.

Z(\ Z를 계산하려면 저항과 두 반응을 기하학적으로 더해야 합니다.

여기서 용량 리액턴스(용량)는

유도 리액턴스(유도)는

- L L { _ { L } = \ L _ { \ { } 。

두 반응 저항이 동일한 값( C L {\ X_}=을 갖는 특수한 공진의 경우 임피던스는 S style {에 만 결정됩니다.

세라믹 캐패시터의 데이터 시트는 임피던스 Z(\ Z만 지정합니다.일반적인 임피던스 곡선은 주파수가 증가하면 임피던스가 최소한으로 감소한다는 것을 보여줍니다.임피던스가 낮을수록 교류 전류가 캐패시터를 쉽게 통과할 수 있습니다.곡선의 최소점인 공진점에서는 X가 X와 같은L 값을 가지며C 캐패시터는 가장 낮은 임피던스 값을 나타낸다.여기서는 ohmic ESR만이 임피던스를 결정합니다.주파수가 공진을 초과하면 ESL에 의해 임피던스가 다시 증가합니다.

ESR, 소산 계수 및 품질 계수

세라믹 콘덴서의 요약 손실은 ohmic AC 손실입니다.DC 손실은 "누출 전류" 또는 "절연 저항"으로 지정되며 AC 사양으로는 무시할 수 있습니다.이러한 AC 손실은 비선형이며 주파수, 온도, 경과시간 및 일부 특수한 유형의 습도에 따라 달라질 수 있습니다.손실은 두 가지 물리적 조건으로 인해 발생합니다.

대형 콘덴서에서 이러한 손실의 가장 큰 부분은 일반적으로 주파수에 의존하는 오믹 유전 손실입니다.IEC 60384-1 표준에 관해 콘덴서의 옴 손실은 캐패시턴스 측정에 사용되는 주파수와 동일한 주파수로 측정됩니다.다음과 같습니다.

- CR hz 1 nF의 세라믹 콘덴서의 경우 100 kHz, 1 MHz(우선) 또는 10 MHz:

- 1 nF < CR 10 10 μF의 세라믹 콘덴서의 경우 1 kHz 또는 10 kHz

- CR > 10μF 세라믹 콘덴서의 경우 50/60Hz 또는 100/120Hz

콘덴서의 집약 저항 손실의 결과는 애플리케이션 요건에 따라 등가 직렬 저항(ESR), 소산 계수(DF, tan δ), 품질 계수(Q) 중 하나로 지정할 수 있습니다.

클래스 2 캐패시터는 대부분 소산 계수 tan µ로 지정됩니다.산란 계수는 X {\ - {\ 및 ESR의 탄젠트로 결정되며, 위의 벡터 다이어그램에서 가상 축과 임피던스 축 사이의 각도 θ로 나타낼 수 있습니다. "임피던스"를 참조하십시오.

L이 작을 경우 소산 계수는 다음과 같이 근사할 수 있습니다.

손실이 매우 낮은 클래스1 콘덴서는 소산계수 및 종종 품질계수(Q)로 지정됩니다.품질 계수는 소산 계수의 역수로 정의됩니다.

Q 계수는 전기 저항의 영향을 나타내며 중심 주파수 또는 공진 0에 대한 공진기의 BB})를 나타냅니다.Q 값이 높으면 공진회로의 공진 품질을 나타내는 마크입니다.

IEC 60384-8/-21/-9/-22에 따라 세라믹 캐패시터는 다음 소산 계수를 초과할 수 없습니다.

| 온도 계수 도자기의 | 최대치 소산 인자 |

|---|---|

| 100 µα > -750 | 황갈색 δ 15 • 10−4 |

| -750 µα > -120 | 황갈색 δ 20 20 • 10−4 |

| -180 αα > -3300 | 황갈색 δ 30 30−4 • |

| - 3300 ≥α > - 5600 | 황갈색 δ 40 40 • 10−4 |

| ≤ −5600 | 황갈색−4 δ 50 50 • |

| 캐패시턴스 값이 50pF 미만인 경우 소산 계수는 더 클 수 있습니다. | |

| 정격 전압 콘덴서의 | 최대치 소산 인자 |

|---|---|

| v 10 V | 황갈색 δ 350 • 10−4 |

| 캐패시턴스 값이 50pF 미만인 경우 소산 계수는 더 클 수 있습니다. | |

세라믹 콘덴서의 옴 손실은 주파수, 온도 및 전압에 따라 달라집니다.또한 클래스 2 캐패시터 측정은 에이징에 따라 달라집니다.세라믹 재료마다 온도 범위와 작동 주파수에 따라 손실이 다릅니다.클래스 1 캐패시터의 변경은 한 자리수 범위이지만 클래스 2 캐패시터의 변경은 훨씬 큽니다.

HF 사용, 인덕턴스(ESL) 및 자기공진 주파수

전기공진은 특정 공진주파수의 세라믹 캐패시터에서 발생하며 캐패시터 임피던스와 어드미턴스의 가상부분이 서로 상쇄된다.X가C X만큼 높은L 이 주파수를 자가 공진 주파수라고 하며 다음과 같이 계산할 수 있습니다.

여기서 f는 헤르츠 단위의 공진 주파수, L은 헨리의 인덕턴스, C는 패러드의 캐패시턴스입니다.

캐패시턴스 C 및 인덕턴스 L이 작을수록 공진 주파수가 높아집니다.자기공진 주파수는 임피던스가 최소를 통과하는 최소 주파수입니다.어떤 AC 어플리케이션에서도 자기공진 주파수는 캐패시터를 용량성 성분으로 사용할 수 있는 가장 높은 주파수입니다.공진 이상의 주파수에서는 ESL에 의해 임피던스가 다시 증가합니다.즉, 캐패시터는 캐패시터의 ESL과 동일한 인덕턴스와 특정 주파수에서 ESR과 동일한 저항을 가진 인덕터가 됩니다.

산업용 콘덴서의 ESL은 주로 플레이트를 외부로 연결하는 데 사용되는 리드 및 내부 연결부에 의해 발생합니다.큰 캐패시터는 작은 캐패시터보다 ESL이 높은 경향이 있습니다.이는 플레이트까지의 거리가 길고 밀리미터마다 인덕턴스가 증가하기 때문입니다.

매우 작은 캐패시턴스 값(pF 이상) 범위에서 사용할 수 있는 세라믹 캐패시터는 최대 100MHz의 고주파수에 적합한 더 작은 캐패시턴스 값을 이미 벗어났습니다(위의 공식 참조).리드가 없고 전극에 근접하기 때문에 MLCC 칩은 f.e. 리드 타입에 비해 기생 인덕턴스가 현저히 낮아 고주파 애플리케이션에 적합합니다.또한 칩의 가로쪽이 아닌 세로쪽 전극에 접촉함으로써 기생 인덕턴스를 더욱 저감할 수 있다.

NP0/C0G 한 세트와 X7R 세라믹 캐패시터 한 세트의 자기 공진 주파수는 다음과 같습니다.[50]

| 10 pF | 100pF | 1 nF | 10 nF | 100 nF | 1°F | |

|---|---|---|---|---|---|---|

| C0G(클래스 1) | 1550MHz | 460 MHz | 160MHz | 55 MHz | ||

| X7R(클래스 2) | 190MHz | 56 MHz | 22 MHz | 10 MHz |

X7R의 주파수 응답은 C0Gs보다 우수합니다.단, 클래스 2 캐패시터는 클래스1보다 훨씬 작기 때문에 기생 인덕턴스가 낮아야 합니다.

에이징

강유전체 클래스 2의 세라믹 캐패시터 캐패시턴스는 시간이 지남에 따라 감소합니다.이 동작을 "에이징"이라고 합니다.노화는 강유전체에서 발생하며, 여기서 유전체 내의 편광 영역은 전체 편광에 기여합니다.유전체 내 편광 영역의 열화는 시간이 지남에 따라 유전율을 감소시켜 구성요소가 [51]노화됨에 따라 클래스 2 세라믹 캐패시터의 캐패시턴스가 감소합니다.[52]

노화는 로그 법칙을 따릅니다.이 법칙은 예를 들어 20°C에서 1시간에서 10시간까지의 기간 동안 정의된 온도에서 납땜 복구 시간 후 10년간 정전용량의 감소를 백분율로 정의합니다.이 법칙은 로그이기 때문에 용량 손실의 백분율은 1시간에서 100시간 사이에서는 2배, 1시간에서 1000시간 사이에서는 3배가 됩니다.따라서 에이징은 시작 부근에서 가장 빠르고 캐패시턴스 값은 시간이 지남에 따라 효과적으로 안정됩니다.

클래스 2 콘덴서의 에이징 속도는 주로 사용되는 재료에 따라 달라집니다.경험의 법칙은 세라믹의 온도 의존도가 높을수록 노화율이 높다는 것입니다.X7R 세라믹 캐패시터의 일반적인 에이징은 10년당[53] 약 2.5%입니다.Z5U 세라믹 캐패시터의 에이징 속도는 현저하게 높아져 10년당 최대 7%가 될 수 있습니다.

2등급 콘덴서의 에이징 프로세스는 구성 [2]요소를 퀴리점 이상으로 가열하여 반전시킬 수 있습니다.

클래스 1 콘덴서는 클래스 2와 같은 강유전체 에이징을 경험하지 않습니다.그러나 높은 온도, 높은 습도 및 기계적 응력과 같은 환경적 영향은 장기간에 걸쳐 작은 되돌릴 수 없는 정전용량 감소로 이어질 수 있으며, 때로는 노화라고도 불립니다.P 100 및 N 470 클래스 1의 캐패시턴스 변화는 1% 미만이며, N 750 ~ N 1500 세라믹의 캐패시턴스는 2% 이하입니다.

절연 저항 및 자가 방전 상수

유전체의 저항은 무한하지 않으므로 DC "누출 전류"가 일정 수준 발생하며, 이는 자가 방전에 기여합니다.세라믹 콘덴서의 경우 콘덴서의 직렬 등가 회로에서 콘덴서와 병렬로 배치된 이 저항을 "절연 저항ins R"이라고 합니다.절연 저항은 환경과 관련하여 외부 절연과 혼동해서는 안 됩니다.

콘덴서 전압 감소 시 자가 방전 속도는 다음 공식을 따릅니다.

저장된 DC 0 및 자가 방전 상수 사용

, s의 캐패시터 이 초기값의 37%로 떨어졌습니다.

단위 MΩ(10Ω)에6 주어진 절연 저항과 초 단위의 자가 방전 상수는 유전체 절연 품질에 중요한 매개 변수입니다.이러한 시간 값은 예를 들어 콘덴서가 샘플 및 홀드 회로 또는 작동 증폭기와 같이 릴레이 또는 전압 값을 저장하는 타이밍 구성요소로 사용되는 경우 중요합니다.

해당 표준에 따라 클래스 1 세라믹 캐패시터는 C 10 10 nF의R 캐패시터일 경우 R ω 10,000 MΩ, C > 10R nF의 캐패시터일 경우 100s 100 s이다ins.클래스ins 2 세라믹 캐패시터는 C n 25 nF의R 캐패시터일 경우 R ω 4,000 MΩ, C > 25R nF의 캐패시터일 경우 100s 100 s이다.

절연 저항과 그에 따른 자가 방전 시간 속도는 온도에 따라 달라지며 60°C당 약 1MΩ의 온도 증가에 따라 감소합니다.

유전체 흡수(비누)

유전체 흡수는 오랫동안 충전된 콘덴서가 불완전하게 방전되는 효과를 일컫는 명칭입니다.이상적인 콘덴서는 방전 후에도 0V로 유지되지만, 실제 콘덴서는 유전체 완화, 침전 또는 배터리 동작이라고도 하는 현상인 시간 지연 쌍극자 방전에서 발생하는 소량의 전압을 발생시킵니다.

| 콘덴서의 종류 | 유전체 흡수 |

|---|---|

| 클래스 1 세라믹 콘덴서, NP0 | 0.3 ~ 0.6% |

| 클래스 2 세라믹 콘덴서, X7R | 2.0~2.5% |

캐패시터 유전체 흡수는 문제가 되지 않지만 장기 정수 적분자, 샘플 홀드 회로, 스위치드 캐패시터 아날로그-디지털 변환기 및 매우 낮은 왜곡 필터와 같은 일부 응용 프로그램에서는 캐패시터가 완전 방전 후 잔류 전하를 회복하지 않는 것이 중요합니다.흡수율이 낮은 or를 지정한다.유전체 흡수에 의해 발생하는 단자의 전압은 경우에 따라 전자회로의 기능에 문제를 일으키거나 작업자의 안전을 위협할 수 있습니다.충격을 방지하기 위해 전원 콘덴서와 같은 매우 큰 콘덴서는 대부분 사용 [54]전에 분리한 단락선과 함께 출고됩니다.

마이크로포니

강유전체 세라믹을 사용하는 모든 클래스 2 세라믹 캐패시터는 압전성을 나타내며 마이크로포닉스, 마이크로포니 [55]또는 오디오 애플리케이션에서 압전 효과를 가집니다.마이크로포니는 전자 부품이 기계적 [56]진동을 많은 경우 바람직하지 않은 소음인 전기 신호로 변환하는 현상을 말합니다.민감한 전자 프리앰프는 일반적으로 이러한 [56]영향을 피하기 위해 1등급 세라믹 및 필름 캐패시터를 사용합니다.

역마이크로폰 효과에서는 콘덴서 플레이트 간의 변화하는 전계가 물리력을 발휘하여 [56]스피커로서 이동한다.고전류 임펄스 부하 또는 높은 리플 전류는 캐패시터로부터 음향음을 발생시킬 수 있지만 캐패시터를 방전시켜 유전체에 [57][58][59]부하를 줍니다.

납땜

세라믹 콘덴서는 납땜 응력으로 인해 전기 파라미터가 변경될 수 있습니다.솔더 배스의 열, 특히 SMD 스타일의 경우 단자와 전극 사이의 접촉 저항의 변화를 일으킬 수 있습니다.강유전체 클래스 2 세라믹 캐패시터의 경우 납땜 온도가 퀴리점보다 높습니다.유전체 내의 편광 영역은 과거로 돌아가 클래스 2 세라믹 콘덴서의 에이징 프로세스가 [2]다시 시작되고 있습니다.

따라서 납땜 후 약 24시간의 복구 시간이 필요합니다.캐패시턴스 값인 ESR과 같은 일부 전기 파라미터를 회복한 후 누출 전류가 불가역적으로 변화합니다.콘덴서의 스타일에 따라 낮은 비율 범위에 변화가 있습니다.

추가 정보

표준화

모든 전기, 전자 부품 및 관련 기술에 대한 표준화는 비영리 비정부 국제 표준 [61][62]기구인 국제 전기 표준 위원회([60]IEC)에 의해 주어진 규칙을 따릅니다.

전자기기에 사용되는 콘덴서의 특성 정의 및 테스트 방법은 일반 사양에 명시되어 있습니다.

- IEC 60384-1, 전자기기에 사용하기 위한 고정 콘덴서 - 제1부: 일반 사양

표준화된 유형으로 승인을 위해 전자 장비에 사용하기 위해 세라믹 캐패시터가 충족해야 하는 시험 및 요건은 다음 섹션 사양에 명시되어 있습니다.

- IEC 60384-8, 세라믹 유전체의 고정 콘덴서, 클래스 1

- IEC 60384-9, 세라믹 유전체의 고정 콘덴서, 클래스 2

- IEC 60384-21, 세라믹 유전체의 고정 표면 마운트 다층 캐패시터, 클래스 1

- IEC 60384-22, 세라믹 유전체의 고정 표면 실장 다층 캐패시터, 클래스 2

탄탈 콘덴서 교환

다층 세라믹 캐패시터는 비용, 신뢰성 및 크기가 경쟁력을 갖추면서 바이패스 또는 고주파 스위치 모드 전원 공급기와 같은 애플리케이션에서 탄탈 및 저용량 알루미늄 전해 캐패시터를 대체하는 데 점점 더 많이 사용되고 있습니다.많은 애플리케이션에서 ESR이 낮기 때문에 더 낮은 공칭 캐패시턴스 [63][64][65][66][67]값을 사용할 수 있습니다.

세라믹 콘덴서의 특징 및 단점

세라믹 콘덴서의 특징과 단점은 메인 문서 "Capacter types #types of types"를 참조하십시오.

마킹

각인 표시

세라믹 콘덴서가 허용 가능한 경우, 다른 대부분의 전자 구성 요소와 마찬가지로 제조업체, 유형, 전기적 및 열적 특성 및 제조 날짜를 나타내는 인쇄 표시가 있습니다.이상적인 경우, 크기가 충분한 경우 캐패시터는 다음과 같이 표시됩니다.

- 제조원의 이름 또는 상표

- 제조자의 형식 명칭

- 정격 캐패시턴스

- 정격 캐패시턴스 공차

- 정격 전압 및 전원 특성(AC 또는 DC)

- 기후 범주 또는 정격 온도

- 제조 연도 및 월(또는 주)

- 안전 표준의 인증 마크(안전 EMI/RFI 억제 캐패시터용)

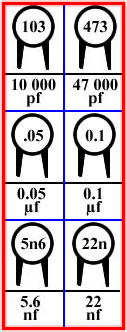

크기가 작은 캐패시터에서는 제한된 공간에 모든 관련 정보를 표시하기 위해 약식 표기법을 사용합니다.가장 일반적으로 사용되는 형식은 XYZ J/K/M Volts V입니다. 여기서 XYZ는 캐패시턴스(XY × 10Z pF로 계산됨), J, K 또는 M은 공차(±5%, ±10%, ±20%)를 나타내며 Volts는 작동 전압을 나타냅니다.

예

- 본체에 105K 330V라는 텍스트가 있는 캐패시터는 10 × 105 pF = 1µF(K = ±10%)의 정전용량을 가지며 작동 전압은 330V입니다.

- 다음 텍스트가 473M 100V인 캐패시터는 작동 전압이 100V일 때 473 × 10 pF = 47 nF(M = ±20%)의 캐패시턴스를 가집니다.

용량, 공차 및 제조일은 IEC/EN 60062에 따라 짧은 코드로 식별할 수 있습니다.정격 캐패시턴스(마이크로패러드)의 쇼트 마크의 예:

- 47 47 = 0.47 µF

- 4°7 = 4.7°F

- 47°F = 47°F

제조 일자는 국제 표준에 따라 인쇄되는 경우가 많습니다.

- 버전 1: 연도/주 숫자 코드로 코딩합니다. "1208"은 "2012, week number 8"입니다.

- 버전 2: 연도 코드/월 코드로 코딩,

연도 코드: "R" = 2003, "S" = 2004, "T" = 2005, "U" = 2006, "V" = 2007, "W" = 2008, "X" = 2009, "A" = 2010, "B" = 2011, "C" = 2012, "D" = 2013 등

월 코드: "1" ~ "9" = 1월 ~ 9월, "O" = 10월, "N" = 11월, "D" = 12월

「X5」는 「2009년, 5월」이 됩니다.

MLCC 칩과 같은 매우 작은 캐패시터에서는 마킹이 불가능합니다.여기서는 제조사의 추적성만이 유형을 식별할 수 있습니다.

컬러 코딩

최신 콘덴서의 식별에는 상세한 색 코딩이 없습니다.

제조원 및 제품

2012년 현재[update] 전 세계 운영 제조업체의 개요와 제품군을 다음 표에 나타냅니다.

| 제조원 | 제품 범위 | |||||

|---|---|---|---|---|---|---|

| MLCC 1kV 미만 | MLCC v 1 kV | 리드 콘덴서 | RFI/EMI 억제. 콘덴서 | 피드 스루 콘덴서 | 힘 콘덴서 | |

| 에이펙스[68] 인테크 | X | – | X | X | – | – |

| AVX/교세라,[69] ATC, 아메리칸 테크니컬[70] 세라믹스 | X | X | X | X | X | X |

| 코소닉 엔터프라이즈[71] | X | X | X | X | – | – |

| 디어본[72] | – | – | – | – | – | X |

| Dover Technologies (CMP)[73] Novacap,[74] Syfer[75]) | X | X | X | X | X | – |

| 뒤빌리에[76] | X | X | X | X | X | – |

| 홀리스톤 HEC[77] | X | X | X | X | X | – |

| 화펑전자(CINETECH)[78] | X | X | – | – | – | – |

| 요한슨 유전체 [79]주식회사 | X | X | X | X | – | – |

| 케이콘[80] | X | X | X | X | X | X |

| KEMET Corporation, Arcotronics, Evox Rifa[81] | X | X | X | X | – | X |

| KOA 코퍼레이션 스피어 일렉트로닉스 [82]주식회사 | X | – | X | – | X | – |

| 모건 일렉트로[83] 세라믹스 | – | – | X | – | – | X |

| 무라타 제조 주식회사유한회사[84] | X | X | X | X | X | X |

| NIC[85] | X | X | X | X | – | – |

| NCC, Europe Chemi-Con[86] | X | X | X | – | – | – |

| Passive Plus, Inc. | X | X | X | X | – | – |

| Presidio Components, Inc.[87] | X | X | X | – | – | X |

| 프로스퍼시 유전체(PDC)[88] | X | X | – | X | – | – |

| 삼성전기유한회사[89] | X | X | – | – | X | – |

| 삼화 콘덴서[90] 그룹 | X | X | X | – | X | – |

| 다이요유덴[91] | X | – | – | – | – | – |

| TDK (TDK Corporation)[92] | X | X | X | X | X | X |

| Tecate[93] 그룹 | X | X | X | X | – | – |

| 투소닉스[94] | – | X | X | X | X | – |

| 유니온 테크놀로지 코퍼레이션(UTC)[95] | X | X | X | X | X | – |

| Vishay Intertechnology Inc, Vitramon, CeraMite[96] | X | X | X | X | – | X |

| 월신[97] 테크놀로지 | X | X | X | X | – | – |

| Würth Electronik eiSos GmbH & Co. KG[98] | X | X | – | X | – | – |

| Yageo, Phycomp[99] | X | – | – | – | – | – |

| 유에토네[100] | X | – | X | X | – | – |

「 」를 참조해 주세요.

레퍼런스

- ^ a b c d e Ho, J.; Jow, T. R.; Boggs, S. (2010). "Historical introduction to capacitor technology". IEEE Electrical Insulation Magazine. 26: 20–25. doi:10.1109/MEI.2010.5383924. S2CID 23077215.다운로드Wayback Machine에서 2016-12-05를 아카이브

- ^ a b c Waugh, Mark D. "Design solutions for DC bias in multilayer ceramic capacitors" (PDF). Murata. Archived from the original (PDF) on May 13, 2012.

- ^ a b "Murata, Technical Report, Evolving Capacitors". Archived from the original on June 17, 2012.

- ^ "MLCC Shortages and Why They Might Last Longer than Expected". www.ttiinc.com. Retrieved 2019-10-20.

- ^ Hackenberger, W.; Kwon, S.; Alberta, E. "Advanced Multilayer Capacitors Using High Energy Density Antiferroelectric Ceramics" (PDF). TRS Technologies Inc. Archived from the original (PDF) on 2013-09-29.

- ^ "CLASS III –General Purpose High-K Ceramic Disk Capacitors" (PDF). Chroma Technology Co., Ltd. Archived from the original (PDF) on July 20, 2013.

- ^ "Kemet: Ceramic leaded Capacitors F-3101F06/05" (PDF). Archived from the original (PDF) on 2008-10-10.

- ^ 세라믹 세라믹스

- ^ a b Otto Zinke; Hans Seither (2002), Widerstände, Kondensatoren, Spulen und ihre Werkstoffe (in German) (2. ed.), Berlin: Springer

- ^ W.S. Lee, J. Yang, T. Y. Su, Y. L. Hu, Yageo:In: 패시브 컴포넌트 산업, 2004년, 26ff Ultra High-Q NP0 MLCC (전기통신용[permanent dead link] Ag 내부 전극 포함)

- ^ "High Temperature - X8R/X8L Dielectric AVX".

- ^ "Semiconductive (Barrier Layer Type) Capacitor , Class III : Semi- conductive type". Yellow Stone corp. Archived from the original on August 30, 2012.

- ^ Hitano. "CERAMIC DISC CAPACITORS-(Semi Conductive) CLASS 3 TYPE S, Y5P… Y5V" (PDF).

{{cite web}}: CS1 maint :url-status (링크) - ^ Kahn, M. "MULTILAYER CERAMIC CAPACITORS–MATERIALS AND MANUFACTURE, TECHNICAL INFORMATION" (PDF). AVX Corporation. Archived from the original (PDF) on July 25, 2012.

- ^ APITech. "Ceramic Capacitors". info.apitech.com. Retrieved 2021-09-13.

- ^ "Intel Voices Concerns Over Quality of High Capacitance Ceramic Chip Capacitors". Archived from the original on 2013-10-12. Retrieved 2012-12-14.

- ^ Tsubota, Shoji. "High-Capacitance Capacitors by Murata Make Smaller Power Supplies" (PDF). Archived from the original (PDF) on November 5, 2012. AEI 2005년 12월

- ^ "Taiyo Yuden Introduces World's First 100 μF EIA 0805 Size Multilayer Ceramic Capacitor" (PDF).

- ^ Nagoshi, Yuki (November 2009). "Wielding Base Metal Yields Cheaper, Stable Class X2 Capacitors". AEI.

- ^ AVX, 저인덕턴스 캐패시터 2013년 5월 16일 웨이백 머신에 보관

- ^ X2Y 감쇠기 LLC

- ^ X2Y 테크놀로지의 개요

- ^ Syfer, X2Y 테크놀로지

- ^ 다층 세라믹 EMI 필터, 시퍼[영구 데드링크]

- ^ "X2Y Technology overview Johanson". Archived from the original on 2013-08-31. Retrieved 2013-08-11.

- ^ 집적회로를 위한 최적의 디커플링 네트워크를 위한 설계자의 로드맵인 디커플링 캐패시터

- ^ X2Y 캐패시터 테크놀로지

- ^ 3단자 콘덴서 구조(Murata)

- ^ "Avoiding Pad Cratering and Capacitor Cracking webinar DFR Solutions".

- ^ O’Malley, P.; Wang, D.; Duong, H.; Lai, Anh; Zelle, Z. (May 25, 2011). "Ceramic Capacitor Failures and Lessons Learned" (PDF). Proceedings of the 55th Annual NDIA Fuze Conference. Archived from the original (PDF) on 2012-01-13.

- ^ Staubli, P.; Prymak, J.; Blais, P.; Long, B. (25–28 September 2006). "Improving Flex Capabilities with Modified MLC Chip Capacitors" (PDF). Proceedings of CARTS Europe 2006. Archived from the original (PDF) on 2013-09-29.

{{cite journal}}: CS1 maint: 날짜 형식(링크 - ^ Sloka, Bill; Skamser, Dan; Phillips, Reggie; Hill, Allen; Laps, Mark; Grace, Roy; Prymak, John; Randall, Michael; Tajuddin, Aziz (March 26–29, 2007). "Flexure Robust Capacitors" (PDF). Proceedings from CARTS USA 2007.

{{cite journal}}: CS1 maint: 날짜 형식(링크 - ^ Vishay, 일반 기술 정보, 무선 간섭 억제 콘덴서

- ^ 일리노이 콘덴서 회사EMI/RFI 억제 캐패시터

- ^ 캐패시터, (RFI/EMI)웨이백 기계에 보관된 AC 주전원의 노이즈 억제 캐패시터의 일반 기술 정보 2014-01-04

- ^ "Electromagnetic Compatibility (EMC) Legislation: Directive 89/336/EC". ec.europa.eu. Archived from the original on 2012-07-05. Retrieved 2012-08-02.

- ^ a b Murata, 세라믹 콘덴서, 안전기준 인정/EA&MS법 준수 [1]

- ^ Vishay, 캐패시터 - 세라믹 - RFI 클래스 X/Y Vishay, 캐패시터 - 세라믹 - RFI 클래스 X/Y 2012년 8월 15일 웨이백 머신에 보관

- ^ Syfer의 MLCC 안전 캐패시터는 클래스 Y2/X1 및 X2 요건을 충족합니다.Syfer의 MLCC 안전 캐패시터는 클래스 Y2/X1 및 X2 요건을 충족합니다.

- ^ Walsin, Multilayer 세라믹 캐패시터, TUV Safety Certified X1/Y2 Series (S2) PDF

- ^ Johanson AC 안전 캐패시터, Type SC 세라믹 칩 캐패시터 PDF 2013년 8월 31일 Wayback Machine에서 보관

- ^ YAGEO, 표면 실장 세라믹 멀티 레이어 캐패시터, 고전압 SC 타입: NP0/X7R PDF

- ^ AVX, 고전압 세라믹 콘덴서 15~100kV, Strontium 기반 유전체, 시리즈 HP/HW/HK, 2012년 7월 25일 Wayback Machine에 보관

- ^ Skelly, A.; Waugh, M. D. (October 2009). "Understanding DC Bias Characteristics in High-Capacitance MLCCs". Ceramic Industry Magazine.

- ^ Istvan Novak, Oracle-America Inc, DesignCon 2011, DC 및 AC 콘덴서의 바이어스 의존도, [2]

- ^ 세라믹 칩 캐패시터의 기본, Johanson Electricics, [3] 2015-01-28 Wayback Machine에서 아카이브됨, 노트/training/jdi_mlcc-basics_2007-12.PDF[permanent dead link]

- ^ M. Fortunato, Maximum 통합 제품, 세라믹 캐패시터의 온도와 전압 변화 또는 4.7µF 캐패시터가 0.33µF 캐패시터가 되는 이유, 2012년 12월 4일, [4]

- ^ 2015년 2월 15일 웨이백 머신에 보관된 콘덴서의 전압계수, 비교 및 솔루션

- ^ Murata, 데이터시트 X7R, 10°F, 25V, GRM31CR71E106KA12#, PDF

- ^ Syfer 테크놀로지

- ^ K. W. Plessner (1956), "Ageing of the Dielectric Properties of Barium Titanate Ceramics", Proceedings of the Physical Society. Section B (in German), vol. 69, no. 12, pp. 1261–1268, Bibcode:1956PPSB...69.1261P, doi:10.1088/0370-1301/69/12/309

- ^ Tsurumi, Takaaki; Shono, Motohiro; Kakemoto, Hirofumi; Wada, Satoshi; Saito, Kenji; Chazono, Hirokazu (2008). "Mechanism of capacitance aging under DC-bias field in X7R-MLCCS". Journal of Electroceramics. 21 (1–4): 17–21. doi:10.1007/s10832-007-9071-0. S2CID 110489189.

- ^ Christopher England, Johanson 유전체, 세라믹 콘덴서 에이징 심플화 웨이백 머신에 2012-12-26년 아카이브

- ^ Ken Kundert 캐패시터의 유전체 흡수 모델링

- ^ Satoshi Isitobi, Murata, Murata Addresses in Mobile, A/V 디바이스: CS1 maint: 제목으로 아카이브된 복사(링크)

- ^ a b c "Capacitors for Reduced Microphonics and Sound Emission" (PDF). KEMET. February 2007. Archived (PDF) from the original on April 2, 2019.

- ^ "Are your military ceramic capacitors subject to the piezoelectric effect?". KEMET. July 27, 2004. Archived from the original on June 19, 2012.

- ^ "FAQ about Singing Capacitors (Piezoelectric Effect)" (PDF). TDK. December 2006. Archived (PDF) from the original on April 2, 2019.

- ^ "Piezoelectric Noise: MLCC Ringing ‐ Singing" (PDF). NIC Components. May 2015. Archived (PDF) from the original on April 2, 2019.

- ^ IEC 홈페이지

- ^ IEC 웹 스토어

- ^ IEC/EN/DIN 표준, Beuth-Verlag

- ^ 파워 일렉트로닉스 테크놀로지 - 다층 세라믹스 또는 탄탈

- ^ 요한슨 유전체, "고급 세라믹 솔루션", Tantalum 대체[permanent dead link] PDF

- ^ Texas Instruments, 세라믹 캐패시터가 LDO의 Tantalum 캐패시터를 대체함, 어플리케이션 리포트 SLVA214A – 2005년 8월– 2006년 10월 개정 PDF

- ^ Rutronik, Tantalum 캐패시터를 MLCC PDF로 교체하기 위한 가이드라인 2015-07-10 Wayback Machine에서 보관

- ^ Kemet, 폴리머 알루미늄, 세라믹, 탄탈 캐패시터 중 하나를 선택하는 방법: CS1 maint: 제목으로 아카이브된 복사(링크)

- ^ "Apex Intec". Archived from the original on 2014-04-27. Retrieved 2015-09-19.

- ^ AVX

- ^ 아메리칸 테크니컬 세라믹스

- ^ "Cosonic Enterprise". Archived from the original on 2013-01-11. Retrieved 2012-12-28.

- ^ "Dearborne". Archived from the original on 2012-11-15. Retrieved 2012-12-28.

- ^ Dover는 2012년 7월 28일 Wayback Machine에서 아카이브 완료

- ^ 노바캅

- ^ "Syfer". Archived from the original on 2007-11-29. Retrieved 2008-03-28.

- ^ 뒤빌리에

- ^ "HolyStone". Archived from the original on 2013-01-29. Retrieved 2012-12-28.

- ^ 화펑 일렉트로닉스

- ^ 요한슨 유전체 주식회사

- ^ 케이콘

- ^ 케메트

- ^ KOA Speer Electronics, Inc.

- ^ "Morgan Electro Ceramics". Archived from the original on 2012-06-15. Retrieved 2012-12-28.

- ^ 무라타

- ^ NIC

- ^ Europe Chemi-Con, 2012년 11월 26일 Wayback Machine에서 아카이브 완료

- ^ "Presidio Components, U.S. Manufacturer of Space and Military Quality Ceramic Capacitors for RF, Microwave, High Temperature, Fiberoptic, high frequency, and custom commercial applications".

- ^ 프로스퍼시 유전체2012년 12월 28일 Wayback Machine에서 아카이브 완료

- ^ 삼성전기유한회사

- ^ 삼화 콘덴서 그룹, 2012년 12월 27일 웨이백 머신에 보관

- ^ 다이요유덴

- ^ TDK

- ^ Tecate 그룹

- ^ 투소닉스

- ^ 유니온 테크놀로지 코퍼레이션

- ^ Vishay Intertechnology Inc.

- ^ Walsin Technology, 2013년 1월 5일 Wayback Machine에서 아카이브

- ^ Würth Electronik 온라인 카탈로그 - 세라믹 콘덴서

- ^ 야지오

- ^ 2012년 6월 21일 Wayback Machine에서 Yuetone 아카이브 완료

!["Flex-Termination" - MLCC chips, a flexible contact layer prevents breaking of the ceramic.[31]](http://upload.wikimedia.org/wikipedia/commons/thumb/f/fc/MLCC-FlexTerm-Crack.svg/120px-MLCC-FlexTerm-Crack.svg.png)

작을 경우 소산 계수는 다음과 같이 근사할 수 있습니다.

작을 경우 소산 계수는 다음과 같이 근사할 수 있습니다.

캐패시터

캐패시터