임계값 전압

Threshold voltage

일반적으로 전계효과 트랜지스터(FET)의th 임계값 전압은 소스와 드레인 단자 사이에 전도 경로를 만드는 데 필요한 최소 게이트-소스 전압GS (th) V입니다.이는 전력 효율을 유지하기 위한 중요한 확장 요소입니다.

접합 전계효과 트랜지스터(JFET)를 참조할 때 임계값 전압을 [1][2]핀치오프 전압이라고 합니다.절연 게이트 전계효과 트랜지스터(IGFET)에 적용되는 핀치오프는 전류가 꺼지지 않더라도 높은 소스 드레인 바이어스 하에서 전류 포화 동작을 일으키는 채널 핀치를 의미하기 때문에 다소 혼란스럽습니다.핀치오프와 달리 임계값 전압이라는 용어는 모호하지 않으며 전계효과 트랜지스터에서 동일한 개념을 나타냅니다.

기본 원칙

n채널 인핸스먼트 모드디바이스에서는 트랜지스터 내에 도전채널이 자연스럽게 존재하지 않으며, 이를 작성하기 위해서는 정의 게이트 대 소스 전압이 필요하다.양전압은 체내에서 자유롭게 떠다니는 전자를 게이트 쪽으로 끌어당겨 전도성 채널을 형성합니다.하지만 먼저, FET의 몸에 첨가된 도판트 이온에 대항하기 위해 게이트 근처에 충분한 전자를 끌어당겨야 합니다. 이것은 고갈 영역이라고 불리는 이동 캐리어가 없는 영역을 형성합니다. 그리고 이것이 발생하는 전압이 FET의 임계값 전압입니다.게이트 대 소스 전압이 추가로 상승하면 더 많은 전자가 게이트로 끌어당겨 소스에서 드레인까지 전도성 채널을 생성할 수 있습니다. 이 과정을 반전이라고 합니다.P 채널 "확장 모드" MOS 트랜지스터의 경우 그 반대입니다.VGS = 0일 때 장치는 "OFF"이고 채널은 개방/비연결입니다.음(-ve) 게이트 전압을 p형 "향상 모드" MOSFET에 적용하면 채널 전도성이 "ON"으로 전환됩니다.

반면 n채널 고갈모드 디바이스는 트랜지스터 내에 자연스럽게 존재하는 도전채널을 가진다.따라서 역치전압이라는 용어는 이러한 소자의 온에는 쉽게 적용되지 않고 대신 전자가 쉽게 흐를 수 있을 정도로 채널이 넓은 전압레벨을 나타낸다.이 흐름의 용이성 임계값은 p채널 고갈 모드 장치에도 적용됩니다.이 모드에서는 게이트에서 본체/소스로의 음전압이 게이트 절연체/반도체 인터페이스에서 양전하를 띤 홀을 강제로 떼어냄으로써 고갈층을 형성하고 고정적이고 음전하를 띤 리셉터 이온의 캐리어 프리 영역을 노출시킵니다.

음의 게이트 소스 전압인 n채널 고갈 MOS 트랜지스터의 경우, -VGS는 트랜지스터 "OFF"를 전환하는 자유 전자의 전도성 채널을 고갈시킵니다(따라서 이름이 지정됨).마찬가지로 p 채널 "감소 모드" MOS 트랜지스터의 게이트 소스 전압이 양의 경우 +VGS는 채널의 빈 구멍을 제거하여 "OFF"로 전환합니다.

와이드 평면 트랜지스터에서 임계값 전압은 기본적으로 드레인-소스 전압과 독립적이며, 따라서 잘 정의된 특성이지만, 드레인 유도 장벽 저하로 인해 현대 나노미터 크기의 MOSFET에서는 덜 명확합니다.

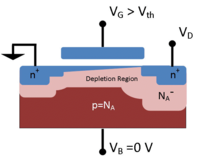

그림에서 소스(왼쪽)와 드레인(오른쪽)에는 n+라는 라벨이 부착되어 있어 도핑이 심한(파란색) n-영역을 나타냅니다.고갈층 도판트는 (분홍색) 고갈층의 이온이 음전하되어 있고 구멍이 거의 없음을 나타내기 위해 N으로 표시되어A− 있습니다.벌크(빨간색)에서 벌크 전하를 중립으로 만드는 구멍 수 p = N입니다A.

게이트 전압이 임계값 전압(왼쪽 그림)보다 낮으면 "향상 모드" 트랜지스터가 꺼지고 이상적으로는 드레인에서 트랜지스터 소스로 전류가 흐르지 않습니다.실제로 게이트 바이어스에 따라 작고 기하급수적으로 변화하지만 임계값(하위 임계값 누출) 미만의 게이트 바이어스에도 전류가 존재합니다.

게이트 전압이 임계값 전압(오른쪽 그림)보다 높으면 산화물-실리콘 인터페이스에서 채널에 많은 전자가 존재하기 때문에 "확장 모드" 트랜지스터가 켜지고, 드레인에서 소스로 전하가 흐를 수 있는 저저항 채널이 생성됩니다.임계값을 크게 초과하는 전압의 경우 이 상황을 강반전이라고 합니다.V > 0이면 채널이D 테이퍼화 됩니다.이는 저항성 채널의 전류로 인한 전압 강하가 드레인 접근에 따라 채널을 지탱하는 산화물 필드를 감소시키기 때문입니다.

바디 이펙트

차체가 임계값 전압에 영향을 미치기 때문에(소스에 연결되지 않은 경우) 차체가 임계값 전압에 영향을 미치기 때문에 차체 효과는 임계값 의 변화량(V B {SB이 소스 벌크 전압의 변화와 거의 동일한 양만큼 변화하는 것입니다.이것은 세컨드 게이트라고 생각할 수 있으며, 때로는 백 게이트라고 불리기도 하며, 따라서 바디 효과는 [3]백 게이트 효과라고 불리기도 합니다.

증강 모드 nMOS MOSFET의 경우, 임계값 전압에 대한 신체 효과는 시크만에 따라 계산됩니다.Hodges [4]모델은 다음 방정식을 사용하여 이전 프로세스 [clarification needed]노드에 정확합니다.

서 V T 은 기판 바이어스 존재 시 임계값 전압, SB는 소스-바디 기판 바이어스, F({2\는 표면 전위, T({F})는 표면 전위입니다.는 기판 바이어스 제로 임계값 전압, ( / x ) NA \ \ left ( t { } / \ { } \ right \ rt { \ _ { \ text } N _ { }}}}}}}}}는 본체 의 입니다는 산화물 유전율, 는 실리콘의 유전율, (\A는 도핑 ,q(\q)는 소전하이다.

산화물 두께에 대한 의존성

90 nm CMOS 프로세스와 같은 특정 기술 노드에서 임계값 전압은 산화물의 선택과 산화물 두께에 따라 달라집니다.위의 차체 으로 T V_{은 산화물 두께 인 \ 및 O X에 정비례한다.

따라서 산화물 두께가 얇을수록 임계값 전압이 낮아집니다.이것이 개선되는 것처럼 보일 수 있지만 비용이 없는 것은 아닙니다. 산화물 두께가 얇을수록 장치를 통과하는 역치 이하 누출 전류가 높아지기 때문입니다.따라서 90nm 게이트 산화물 두께의 설계 사양을 1nm로 설정하여 누출 [5]전류를 제어한다.이런 종류의 터널링,[6] 파울러-노르하임 터널링입니다.

서 C 1 0(\은 이고 x는 게이트 산화물을 가로지르는 전계입니다.

설계 피쳐를 90nm로 축소하기 전에는 산화물 두께를 만들기 위한 이중 산화물 접근 방식이 이 문제에 대한 일반적인 해결책이었습니다.90 nm 공정 기술에서는 일부 경우에 [7]삼산화물 방식을 채택했습니다.하나의 표준 얇은 산화물은 대부분의 트랜지스터에, 다른 하나는 I/O 드라이버 셀에, 그리고 다른 하나는 메모리 앤 패스 트랜지스터 셀에 사용됩니다.이는 CMOS 기술의 역치 전압에 대한 산화물 두께 특성에 따른 것이다.

온도 의존성

산화물 두께가 역치 전압에 영향을 미치는 경우와 마찬가지로 온도는 CMOS 장치의 역치 전압에 영향을 미친다.차체 효과 섹션의 방정식 일부 확장

여기서 F \ _는 접점 전위의 k {\k}는 볼츠만 T {\ T는 온도,q {\q}는 기본 전하, { 은 도핑 파라미터, {은 고유 전위입니다.도핑 매개 변수입니다.

표면 전위는 온도와 직접적인 관계가 있음을 알 수 있습니다.위에서 보면 임계값 전압은 직접적인 관계가 없지만 영향과 독립적이지 않습니다.이 변동은 [8]도핑 수준에 따라 일반적으로 -4 mV/K와 -2 mV/K 사이입니다.30°C의 변경 시 90-nm 기술 노드에 일반적으로 사용되는 500mV 설계 매개변수와 상당한 차이가 발생합니다.

무작위 도판트 변동에 대한 의존성

랜덤 도판트 변동(RDF)은 주입된 불순물 농도의 변동으로 인한 프로세스 변동의 한 형태입니다.MOSFET 트랜지스터에서는 채널 영역의 RDF가 트랜지스터의 특성, 특히 임계값 전압을 변경할 수 있습니다.새로운 공정 기술에서는 도판트의 총 수가 [9]적기 때문에 RDF가 더 큰 효과를 발휘합니다.

동일한 [10]제조공정에서 소자간 역치전압의 변동을 초래하는 도판트 변동을 억제하기 위한 연구가 진행되고 있다.

「 」를 참조해 주세요.

레퍼런스

- ^ "Junction Field Effect Transistor (JFET)" (PDF). ETEE3212 Lecture Notes.

This is called the threshold, or pinch-off, voltage and occurs at vGS=VGS(OFF).

- ^ Sedra, Adel S.; Smith, Kenneth C. "5.11 THE JUNCTION FIELD-EFFECT TRANSISTOR (JFET)" (PDF). Microelectronic Circuits.

For JFETs the threshold voltage is called the pinch-off voltage and is denoted VP.

- ^ Marco Delaurenti, 박사학위 논문, 고속 VLSI 회로의 설계 및 최적화 기술(1999)Wayback Machine에서 2014-11-10년 아카이브 완료

- ^ NanoDotTek 보고서 NDT14-08-2007, 2007년 8월 12일

- ^ 스기이, 와타나베, 스가타니.90 nm 이상 발전용 트랜지스터 설계.(2002)

- ^ S. M. Sze, 반도체 장치 물리학, 뉴욕, 제2판: Wiley and Sons, 1981, 페이지 496–504.

- ^ 아닐 텔리케팔리, Xilinx Inc, 90 nm FPGA 설계 시 전력 고려사항(2005)[1]

- ^ Weste와 Esraghian, CMOS VLSI 설계의 원리: 시스템 관점, 제2판, (1993) 페이지 48 ISBN 0-201-53376-6

- ^ Asenov, A.Huang, 랜덤 도판트 유도 임계값 전압 강하 및 0.1μm 미만의 MOSFET 변동: 3차원 "원자" 시뮬레이션 연구, 전자 장치, IEEE 트랜잭션, 45, 문제: 12

- ^ Asenov, A.Huang, 에피택셜 및 γ-도프 채널을 가진 0.1μm 미만의 MOSFET에서 랜덤 도판트 유도 임계값 전압 변동 억제, 전자 디바이스, IEEE 트랜잭션, 46, 문제: 8

기판 바이어스 존재 시 임계값 전압,

기판 바이어스 존재 시 임계값 전압,  표면 전위,

표면 전위,  기판 바이어스 제로 임계값 전압,

기판 바이어스 제로 임계값 전압,  본체

본체

실리콘의 유전율,

실리콘의 유전율,

게이트 산화물을 가로지르는 전계입니다.

게이트 산화물을 가로지르는 전계입니다.

접점 전위의

접점 전위의

온도,

온도, 고유 전위입니다.도핑 매개 변수입니다.

고유 전위입니다.도핑 매개 변수입니다.