관리 데이터 입출력

Management Data Input/OutputManagement Data Input/Output(MDIO; 관리 데이터 입력/출력)은 Serial Management Interface(SMI; 시리얼 관리 인터페이스) 또는 Media Independent Interface Management(MIIM; 미디어 독립 인터페이스)용 IEEE 802.3 표준의 이더넷패밀리에 대해 정의된 시리얼 버스입니다.MII는 Media Access Control(MAC; 미디어 액세스컨트롤) 디바이스를 Ethernet Physical Layer(PHY; 이더넷물리층) 회선에 접속합니다.MDIO를 제어하는 MAC 디바이스는 Station Management Entity(SME; 스테이션 관리 엔티티)라고 불립니다.

MII와의 관계

MII에는 2개의 신호 인터페이스가 있습니다.

- 이더넷 프레임 데이터를 송수신하기 위한 이더넷 MAC에 대한 데이터 인터페이스.

- PHY 관리 인터페이스인 MDIO는 동작 전에 각 PHY를 설정하기 위해 PHY의 제어 레지스터와 상태 레지스터를 읽고 쓰고 동작 중에 링크 상태를 감시하기 위해 사용됩니다.

전기 사양

MDIO 인터페이스는 다음 2개의 신호에 의해 구현됩니다.

- MDIO Interface Clock(MDC): MAC 디바이스에 의해 PHY로 구동되는 클럭.

- MDIO 데이터: 양방향, PHY는 읽기 작업 종료 시 레지스터 데이터를 제공하도록 데이터를 구동합니다.

버스는 마스터로서 1개의 MAC만을 지원하며 최대 32개의 PHY 슬레이브를 가질 수 있습니다.

MDC는 최소 400ns의 주기(최대 주파수 2.5MHz에 대응)로 주기적일 수 있습니다.다만, 새로운 칩을 사용하면, 보다 고속의 액세스가 가능합니다.예를 들어 DP83640은 MDC의 최대 클럭환율을 25MHz로 지원합니다.

MDIO에는 최악의 경우 총 누출 전류 32PHY와 1MAC를 고려하여 1.5kΩ~10kΩ의 특정 풀업 저항이 필요합니다.

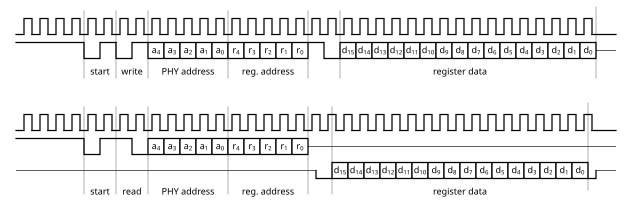

버스 타이밍(조항 22)

레지스터 액세스 전에 PHY 디바이스는 일반적으로 32개의 프리암블을 MDIO 회선상에서 MAC에 의해 송신해야 합니다.액세스는 16개의 제어 비트와 16개의 데이터 비트로 구성됩니다.제어 비트는 2개의 시작 비트, 2개의 액세스타입 비트(읽기 또는 쓰기), PHY 주소(5비트), 레지스터 주소(5비트) 및 2개의 "턴어라운드" 비트로 구성됩니다.

write 명령어 실행 중 MAC은 주소와 데이터를 제공합니다.읽기 명령의 경우 PHY는 턴어라운드비트 시간 동안 MDIO 회선을 인계받아 요청된 레지스터 데이터를 MAC에 공급하고 MDIO 회선을 해방합니다.

MAC가 MDIO 회선을 구동할 때는 클럭의 MDC의 상승 에지 전에 10ns(셋업 시간)의 안정된 값을 보증해야 합니다.또한 MDIO는 MDC의 상승 에지 후에 10ns(홀드 시간)의 안정된 상태를 유지해야 합니다.

PHY가 MDIO 회선을 구동하는 경우 PHY는 [1]클럭의 상승 에지 후에 0 ~300 ns의 MDIO 신호를 제공해야 합니다.따라서 최소 클럭 주기가 400ns(2.5MHz 최대 클럭환율)이므로 MAC는 클럭의 로우 사이클 후반부에 안전하게 MDIO를 샘플링할 수 있습니다.

MDIO 패킷 포맷(조항 22)

| MDIO 패킷 포맷 | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 비트: | 0 | 1 | 2 | 3 | 4 | 8 | 9 | 13 | 14 | 15 | 16 | 31 | ||||||||||||||||||||

| 0 | PRE_32 | |||||||||||||||||||||||||||||||

| 32 | 세인트 | 동작 | PA5 | RA5 | TA | D16 | ||||||||||||||||||||||||||

PRE_32

MDIO 헤더의 첫 번째 필드는 Preamble입니다.프리암블 중에 MAC는 32비트(모두 '1')를 MDIO 회선상에 송신합니다.

세인트

Start 필드는 2비트로 구성되며 항상 '01' 조합이 포함됩니다.

동작

Opcode는 2비트로 구성됩니다.가능한 연산 코드는 '10'을 읽거나 '01'을 쓰는 두 가지가 있습니다.

PA5

5비트, PHY 주소

RA5

[ Register Address ]필드는 쓰기 또는 읽기 레지스터를 나타냅니다.5비트 길이입니다.

TA

턴어라운드 필드의 길이는 2비트입니다.데이터를 PHY에 쓸 때 MAC은 MDIO 행에 '10'을 씁니다.데이터를 읽을 때 MAC은 MDIO 행을 해방합니다.

D16

16비트, 데이터이것은 OP 필드의 값에 따라 SME 또는 PHY에서 전송할 수 있습니다.

Z

MDIO를 등록합니다.

명령어

IEEE 802.3 Part 3 에서는[1], 다른 opcode 와 start 시퀀스를 사용합니다.레지스터를 읽고 쓰는 2개의 시리얼 트랜잭션으로서 opcode 00(설정 주소) 및 11(read)/01(write)/10(read increment)을 이용한다.

레퍼런스

- ^ a b "IEEE 802.3 Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) access method and Physical Layer specification". IEEE. Retrieved April 30, 2020.