소켓 FM2

Socket FM2 | |

| 유형 | PGA-ZIF |

|---|---|

| 칩 폼 팩터 | PGA |

| 연락처 | 904 |

| FSB 프로토콜 | Unified Media Interface(UMI; 통합 미디어 인터페이스) |

| 전임자 | FM1 |

| 후계자 | FM2+ |

이 문서는 CPU 소켓 시리즈의 일부입니다. | |

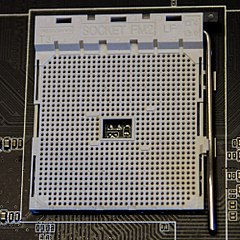

소켓 FM2는 AMD의 데스크톱 Trinity 및 리치랜드 APU와 이들을 기반으로 한 Athlon X2 및 Athlon X4 프로세서가 메인보드에 접속하기 위해 사용하는 CPU 소켓입니다.FM2는 2012년 [1]9월 27일에 개국했다.새로운 FM2 CPU 소켓을 탑재한 메인보드도 새로운 A85X 칩셋의 [2]AMD를 사용합니다.

소켓은 FM1과 매우 유사하며, 중앙의 5×7 보이드, 각 모서리에서 3개의 핀이 누락되고 몇 개의 추가 키 핀이 누락된 31×31 그리드를 기반으로 합니다.Socket FM1과 비교하여 2개의 키핀을 이동시키고 1개의 키핀을 분리하여 904개의 [3]핀을 남겼습니다.

사용 가능한 칩셋에 대해서는 Fusion 컨트롤러 허브(FCH)를 참조하십시오.

스팀 롤러 기반의 'Kaveri' APU는 지원되지 않습니다.「소켓 FM2+(FM2r2)」및 「소켓 FP3(BGA-)」를 참조해 주세요.?)[4]

히트 싱크

AMD 소켓 AM2, 소켓 AM2+, 소켓 AM3, 소켓 AM3+ 및 소켓 FM2의 경우 히트 싱크를 메인보드에 고정하기 위한 4개의 구멍은 가로 길이 48mm 및 96mm의 직사각형에 배치되어 있습니다.따라서 냉각 솔루션은 서로 교환할 수 있어야 합니다.

기능의 개요

다음 표에 AMD의 APU 기능을 나타냅니다(참조 항목:AMD 액셀러레이션 처리 장치 목록).

| 플랫폼 | 고출력, 표준전력 및 저전력 | 저전력 및 초저전력 | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 코드명 | 서버 | 기본의 | 토론토 | |||||||||||||||||

| 마이크로 | 교토 | |||||||||||||||||||

| 데스크톱 | 성능 | 르누아르 | 세잔 | |||||||||||||||||

| 메인스트림 | 라노 | 삼위일체 | 리치랜드 | 카베리 | Kaveri 리프레시(고다바리프레시 | 카리조 | 브리스톨 능선 | 레이븐 리지 | 피카소 | |||||||||||

| 엔트리 | ||||||||||||||||||||

| 기본의 | 카비니 | |||||||||||||||||||

| 모바일. | 성능 | 르누아르 | 세잔 | 렘브란트 | ||||||||||||||||

| 메인스트림 | 라노 | 삼위일체 | 리치랜드 | 카베리 | 카리조 | 브리스톨 능선 | 레이븐 리지 | 피카소 | ||||||||||||

| 엔트리 | 달리 | |||||||||||||||||||

| 기본의 | 데스나, 온타리오, 자케이트 | 카비니 주, 테마시 | 비마, 멀린스 | 카리조 L | 스토니리지 | |||||||||||||||

| 내장 | 삼위일체 | 흰머리 독수리 | 멀린 팔콘, 갈색 매 | 큰뿔올빼미 | 그레이 호크 | 온타리오, 자카테 | 카비니 | 스텝 이글, 크라운 이글 LX 패밀리 | 프레리 팔콘 | 밴딩 케스트렐 | ||||||||||

| 방출된 | 2011년 8월 | 2012년 10월 | 2013년 6월 | 2014년 1월 | 2015 | 2015년 6월 | 2016년 6월 | 2017년 10월 | 2019년 1월 | 2020년 3월 | 2021년 1월 | 2022년 1월 | 2011년 1월 | 2013년 5월 | 2014년 4월 | 2015년 5월 | 2016년 2월 | 2019년 4월 | ||

| CPU 마이크로아키텍처 | K10 | 스택드라이버 | 증기 롤러 | 굴착기 | "엑스커베이터+"[5] | 선 | 젠플러스 | 젠 2 | 젠3 | Zen 3 이상 | 밥캣 | 재규어 | 푸마 | 푸마+[6] | "엑스커베이터+" | 선 | ||||

| ISA | x86-64 | x86-64 | ||||||||||||||||||

| 소켓 | 데스크톱 | 하이엔드 | — | — | ||||||||||||||||

| 메인스트림 | — | AM4 | — | |||||||||||||||||

| 엔트리 | FM1 | FM2 | FM2+[a] | — | ||||||||||||||||

| 기본의 | — | — | AM1 | — | ||||||||||||||||

| 다른. | FS1 | FS1+, FP2 | FP3 | FP4 | FP5 | FP6 | FP7 | FT1 | FT3 | FT3b | FP4 | FP5 | ||||||||

| PCI Express 버전 | 2.0 | 3.0 | 4.0 | 2.0 | 3.0 | |||||||||||||||

| Fab. (nm) | GF32 SHP (HKMGSOI) | GF 28SHP (HKMG 벌크) | GF 14LPP (FinFET 벌크) | GF 12LP (FinFET 벌크) | TSMCN7 (FinFET 벌크) | TSMC N6 (FinFET 벌크) | TSMC N40 (표준) | TSMC N28 (HKMG 벌크) | GF 28SHP (HKMG 벌크) | GF 14LPP (FinFET 벌크) | ||||||||||

| 다이 면적(mm2) | 228 | 246 | 245 | 245 | 250 | 210[7] | 156 | 180 | 210 | 75 (+28 FCH) | 107 | ? | 125 | 149 | ||||||

| 최소 TDP(W) | 35 | 17 | 12 | 10 | 15 | 4.5 | 4 | 3.95 | 10 | 6 | ||||||||||

| 최대 APU TDP(W) | 100 | 95 | 65 | 45 | 18 | 25 | ||||||||||||||

| 최대 재고 APU 기준 클럭(GHz) | 3 | 3.8 | 4.1 | 4.1 | 3.7 | 3.8 | 3.6 | 3.7 | 3.8 | 4.0 | 3.3 | 1.75 | 2.2 | 2 | 2.2 | 3.2 | 2.6 | |||

| 노드당[b] 최대 APU 수 | 1 | 1 | ||||||||||||||||||

| APU당 최대 CPU[c] 코어 수 | 4 | 8 | 2 | 4 | 2 | |||||||||||||||

| CPU 코어당 최대 스레드 수 | 1 | 2 | 1 | 2 | ||||||||||||||||

| i386, i486, i586, CMOV, NOL, i686, PAE, NX 비트, CMPXCHG16B, AMD-V, RVI, ABM 및 64 비트 LAHF/SAHF | ||||||||||||||||||||

| IOMMU[d] | — | |||||||||||||||||||

| BMI1, AES-NI, CLMUL 및 F16C | — | |||||||||||||||||||

| 움직임 | — | |||||||||||||||||||

| AVIC, BMI2, RDRAND | — | |||||||||||||||||||

| ADX, SHA, RDSEED, SMAP, SMEP, XSAVEC, XSAVES, XRSTors, CLFLUSHOPT 및 CLZERO | — | — | ||||||||||||||||||

| WBNOINVD, CLWB, RDPID, RDPRU 및 MCOMMIT | — | — | ||||||||||||||||||

| 코어당 FPU 수 | 1 | 0.5 | 1 | 1 | 0.5 | 1 | ||||||||||||||

| FPU당 파이프 수 | 2 | 2 | ||||||||||||||||||

| FPU 파이프 폭 | 128비트 | 256비트 | 80비트 | 128비트 | ||||||||||||||||

| CPU 명령 집합 SIMD 수준 | SSE4a[e] | AVX | AVX2 | SSE3 | AVX | AVX2 | ||||||||||||||

| 3DNow! | — | — | ||||||||||||||||||

| FMA4, LWP, TBM 및 XOP | — | — | — | — | ||||||||||||||||

| FMA3 | ||||||||||||||||||||

| 코어당 L1 데이터 캐시(KiB) | 64 | 16 | 32 | 32 | ||||||||||||||||

| L1 데이터 캐시 관련성(방법) | 2 | 4 | 8 | 8 | ||||||||||||||||

| 코어당 L1 명령 캐시 수 | 1 | 0.5 | 1 | 1 | 0.5 | 1 | ||||||||||||||

| 최대 APU 총 L1 명령 캐시(KiB) | 256 | 128 | 192 | 256 | 64 | 128 | 96 | 128 | ||||||||||||

| L1 명령 캐시의 어소시에이티비티 | 2 | 3 | 4 | 8 | 2 | 3 | 4 | |||||||||||||

| 코어당 L2 캐시 수 | 1 | 0.5 | 1 | 1 | 0.5 | 1 | ||||||||||||||

| 최대 APU 합계 L2 캐시(MiB) | 4 | 2 | 4 | 1 | 2 | 1 | ||||||||||||||

| L2 캐시 어소시에이티비티(웨이) | 16 | 8 | 16 | 8 | ||||||||||||||||

| APU 총 L3 캐시(MiB) | — | 4 | 8 | 16 | — | 4 | ||||||||||||||

| APU L3 캐시 관련성(방법) | 16 | 16 | ||||||||||||||||||

| L3 캐시 스킴 | 피해자. | 피해자. | ||||||||||||||||||

| 최대 재고 DRAM 지원 | DDR3-1866 | DDR3-2133 | DDR3-2133, DDR4-2400 | DDR4-2400 | DDR4-2933 | DDR4-3200, LPDDR4-4266 | DDR5-4800, LPDDR5-6400 | DDR3L-1333 | DDR3L-1600 | DDR3L-1866 | DDR3-1866, DDR4-2400 | DDR4-2400 | ||||||||

| APU당 최대 DRAM 채널 수 | 2 | 1 | 2 | |||||||||||||||||

| APU당 최대 재고 DRAM 대역폭(GB/s) | 29.866 | 34.132 | 38.400 | 46.932 | 68.256 | 102.400 | 10.666 | 12.800 | 14.933 | 19.200 | 38.400 | |||||||||

| GPU 마이크로아키텍처 | 테라스케일 2(VLIW5) | 테라스케일3(VLIW4) | GCN 제2세대 | GCN 제3세대 | GCN 제5세대[8] | RDNA 제2세대 | 테라스케일 2(VLIW5) | GCN 제2세대 | GCN 제3세대[8] | GCN 제5세대 | ||||||||||

| GPU 명령 세트 | TeraScale 명령 집합 | GCN 명령 세트 | RDNA 명령 세트 | TeraScale 명령 집합 | GCN 명령 세트 | |||||||||||||||

| 최대 재고 GPU 기본 클럭(MHz) | 600 | 800 | 844 | 866 | 1108 | 1250 | 1400 | 2100 | 2400 | 538 | 600 | ? | 847 | 900 | 1200 | |||||

| GPU 기반[f] GPU 최대 재고 수 | 480 | 614.4 | 648.1 | 886.7 | 1134.5 | 1760 | 1971.2 | 2150.4 | 3686.4 | 86 | ? | ? | ? | 345.6 | 460.8 | |||||

| 3차원[g] 엔진 | 최대 400:20:8 | 최대 384:24:6 | 최대 512:32:8 | 최대 704:44:16[9] | 최대 512:32:8 | 768:48:8 | 80:8:4 | 128:8:4 | 최대 192:?: | 최대 192:?: | ||||||||||

| IOMMUv1 | IOMMUv2 | IOMMUv1 | ? | IOMMUv2 | ||||||||||||||||

| 비디오 디코더 | UVD 3.0 | UVD 4.2 | UVD 6.0 | VCN 1.0[10] | VCN 2.1[11] | VCN 2.2[11] | VCN 3.1 | UVD 3.0 | UVD 4.0 | UVD 4.2 | UVD 6.0 | UVD 6.3 | VCN 1.0 | |||||||

| 비디오 인코더 | — | VCE 1.0 | VCE 2.0 | VCE 3.1 | — | VCE 2.0 | VCE 3.1 | |||||||||||||

| AMD Fluid Motion | ||||||||||||||||||||

| GPU 전력 절약 | PowerPlay | PowerTune | PowerPlay | PowerTune[12] | ||||||||||||||||

| True Audio | — | ? | — | |||||||||||||||||

| 프리싱크 | 1 2 | 1 2 | ||||||||||||||||||

| HDCP[h] | ? | 1.4 | 1.4 2.2 | ? | 1.4 | 1.4 2.2 | ||||||||||||||

| 플레이레디[h] | — | 3.0 미정 | — | 3.0 미정 | ||||||||||||||||

| 지원되는 디스플레이[i] | 2–3 | 2–4 | 3 | 3(표준) 4 (모바일, 내장) | 4 | 2 | 3 | 4 | ||||||||||||

/drm/radeon[j][15][16] | — | — | ||||||||||||||||||

/drm/amdgpu[j][17] | — | — | ||||||||||||||||||

- ^ FM2+ 굴착기 모델: A8-7680, A6-7480 및 Athlon X4 845.

- ^ PC는 하나의 노드입니다.

- ^ APU는 CPU와 GPU를 결합합니다.둘 다 코어가 있어요

- ^ 펌웨어 지원이 필요합니다.

- ^ SSE4는 없습니다.SSE3는 없습니다.

- ^ 단정도 성능은 FMA 연산에 기초하여 베이스(또는 부스트) 코어 클럭 속도에서 계산됩니다.

- ^ 유니파이드 셰이더: 텍스처 매핑 단위: 렌더 출력 단위

- ^ a b 보호된 비디오 콘텐츠를 재생하려면 카드, 운영 체제, 드라이버 및 응용 프로그램 지원도 필요합니다.이를 위해서는 호환되는 HDCP 디스플레이도 필요합니다.HDCP는 특정 오디오 형식의 출력에 필수적이며 멀티미디어 설정에 추가적인 제약을 가합니다.

- ^ 3개 이상의 디스플레이를 공급하려면 추가 패널이 기본 DisplayPort를 [14]지원해야 합니다.또는 액티브한 DisplayPort-to-DVI/HDMI/VGA 어댑터를 사용할 수 있습니다.

- ^ a b DRM(Direct Rendering Manager)은 Linux 커널의 컴포넌트입니다.이 표의 지원은 최신 버전을 나타냅니다.

외부 링크

- ^ van Miltenburg, Olaf (2012-09-27). "AMD introduceert Trinity-apu's voor de desktop". Tweakers.

- ^ Hugosson, Jacob (2011-10-03). "AMD Piledriver 10% faster than Bulldozer". NordicHardware. Archived from the original on 2012-10-22. Retrieved 2011-10-04.

- ^ Chris Angelini (September 26, 2012), "Socket Compatibility And The A85X FCH", Tom's Hardware: 6, retrieved 2012-12-10

- ^ "Report: Upcoming Socket FM2+ Will Support Older Trinity and Richland APUs". 6 June 2013.

- ^ "AMD Announces the 7th Generation APU: Excavator mk2 in Bristol Ridge and Stoney Ridge for Notebooks". 31 May 2016. Retrieved 3 January 2020.

- ^ "AMD Mobile "Carrizo" Family of APUs Designed to Deliver Significant Leap in Performance, Energy Efficiency in 2015" (Press release). 20 November 2014. Retrieved 16 February 2015.

- ^ "The Mobile CPU Comparison Guide Rev. 13.0 Page 5 : AMD Mobile CPU Full List". TechARP.com. Retrieved 13 December 2017.

- ^ a b "AMD VEGA10 and VEGA11 GPUs spotted in OpenCL driver". VideoCardz.com. Retrieved 6 June 2017.

- ^ Cutress, Ian (1 February 2018). "Zen Cores and Vega: Ryzen APUs for AM4 – AMD Tech Day at CES: 2018 Roadmap Revealed, with Ryzen APUs, Zen+ on 12nm, Vega on 7nm". Anandtech. Retrieved 7 February 2018.

- ^ Larabel, Michael (17 November 2017). "Radeon VCN Encode Support Lands in Mesa 17.4 Git". Phoronix. Retrieved 20 November 2017.

- ^ a b "AMD Ryzen 5000G 'Cezanne' APU Gets First High-Res Die Shots, 10.7 Billion Transistors In A 180mm2 Package". wccftech. Aug 12, 2021. Retrieved August 25, 2021.

{{cite web}}: CS1 maint :url-status (링크) - ^ Tony Chen; Jason Greaves, "AMD's Graphics Core Next (GCN) Architecture" (PDF), AMD, retrieved 13 August 2016

- ^ "A technical look at AMD's Kaveri architecture". Semi Accurate. Retrieved 6 July 2014.

- ^ "How do I connect three or More Monitors to an AMD Radeon™ HD 5000, HD 6000, and HD 7000 Series Graphics Card?". AMD. Retrieved 8 December 2014.

- ^ Airlie, David (26 November 2009). "DisplayPort supported by KMS driver mainlined into Linux kernel 2.6.33". Retrieved 16 January 2016.

- ^ "Radeon feature matrix". freedesktop.org. Retrieved 10 January 2016.

- ^ Deucher, Alexander (16 September 2015). "XDC2015: AMDGPU" (PDF). Retrieved 16 January 2016.

- ^ a b Michel Dänzer (17 November 2016). "[ANNOUNCE] xf86-video-amdgpu 1.2.0". lists.x.org.

- btarunr (2011-07-25). "AMD's Next Gen. Korona High-End Desktop Platform to Fuse Processor with Northbridge". TechPowerUp.

- "APU依然当家 AMD明年各平台产品线曝光".