웨이퍼(전자제품)

Wafer (electronics)전자공학에서 웨이퍼(슬라이스 또는 [1]기판이라고도 함)는 결정 실리콘(c-Si)과 같은 반도체의 얇은 조각으로 집적회로의 제작과 태양광 발전학에서 태양 전지의 제조에 사용됩니다.웨이퍼는 웨이퍼에 내장된 마이크로 전자 장치의 기판 역할을 합니다.도핑, 이온 주입, 식각, 다양한 재료의 박막 증착, 사진 석면 패턴 제작 등 많은 미세 제작 공정을 거칩니다.마지막으로 웨이퍼 다이싱에 의해 개별 마이크로회로를 분리하여 집적회로로서 패키지화한다.

역사

이 섹션은 확장해야 합니다.추가하시면 됩니다. (2015년 1월) |

반도체 또는 실리콘 웨이퍼 산업에서 웨이퍼라는 용어는 1950년대에 일반적으로 게르마늄 또는 실리콘과 같은 반도체 재료의 얇은 둥근 슬라이스를 의미하는 용어로 사용되었습니다.둥근 모양은 보통 Czochralski 방법을 사용하여 생성된 단결정 잉곳에서 비롯됩니다.실리콘 웨이퍼는 1940년대에 [2][3]처음 도입되었다.

1960년까지 실리콘 웨이퍼는 MEMC/SunEdison과 같은 회사에 의해 미국에서 제조되었습니다.1965년, 미국인 엔지니어 에릭 오.에른스트, 도널드 J.허드와 제라드 실리는 IBM에서 일하는 동안 최초의 고용량 에피택셜 장치에 대해 특허 US3423629A를[4] 출원했습니다.

실리콘 웨이퍼는 섬코, 신에쓰화학,[5] 헴록반도체, 실트로닉 등의 회사가 만든다.

생산.

형성

웨이퍼는 순도가 99.999999%(9N)[6] 이상인 [6]매우 순수하고 결함이 거의 없는 단일 결정 재료로 구성됩니다.결정성 웨이퍼를 형성하는 한 가지 과정은 폴란드 화학자 Jan Czochralski에 의해 발명된 Czochralski 방법으로 알려져 있습니다.이 과정에서 실리콘이나 게르마늄 등 고순도 단결정 반도체로 이루어진 원통형 잉곳(boule)을 [7][8]녹여 종결정(seed crystaline)을 형성한다.실리콘의 경우 붕소나 인 등의 공여 불순물 원자를 용융 내성 재료에 정밀하게 첨가하여 결정 도핑을 할 수 있으므로 n형 또는 p형 외인성 반도체로 바꿀 수 있다.

그런 다음 부울을 웨이퍼 톱(와이어 톱의 일종)으로 슬라이스하고, 평탄도를 개선하기 위해 기계가공하고, 기계 가공 단계에서 결정 손상을 제거하기 위해 화학적으로 식각한 후 마지막으로 연마하여 [9]웨이퍼를 형성합니다.태양광 발전용 웨이퍼의 크기는 100~200mm 정사각형이며 두께는 100~500μm입니다.[10]전자제품은 직경 100~450mm의 웨이퍼 크기를 사용합니다.제조된 가장 큰 웨이퍼는 직경이 450mm이지만 [11]아직 일반적으로 사용되지 않습니다.

클리닝, 텍스처링, 식각

웨이퍼는 불필요한 입자를 제거하기 위해 약한 산으로 세척됩니다.실리콘 웨이퍼 표면에 오염이 없는지 확인하기 위한 몇 가지 표준 세척 절차가 있습니다.가장 효과적인 방법 중 하나는 RCA 클린입니다.태양 전지에 사용할 경우 웨이퍼는 거친 표면을 만들어 표면적을 증가시키고 효율성을 증가시키도록 텍스처링됩니다.생성된 PSG(인산규산유리)는 식각 [12]시 웨이퍼 가장자리에서 제거됩니다.

웨이퍼 속성

표준 웨이퍼 크기

실리콘

실리콘 웨이퍼는 25.4mm(1인치)에서 300mm(11.8인치)[13][14]까지 다양한 직경으로 사용할 수 있습니다.속칭 팹이라고 하는 반도체 제조 플랜트는, 생산하기 위해서 사용되는 웨이퍼의 직경에 의해서 정의됩니다.직경은 점차 증가하여 처리량을 개선하고 비용을 절감하며, 현재 사용되는 300mm의 최첨단 팹은 450mm를 [15][16]채택할 것을 제안하고 있습니다.인텔, TSMC 및 삼성은 450mm의 "프로토타입"(연구용) 팹의 출현에 대해 개별적으로 연구를 진행했지만,[17] 여전히 심각한 장애물이 남아 있습니다.

| 웨이퍼 크기 | 표준 두께 | 도입년도 | 웨이퍼당 중량 | 웨이퍼당 100mm2(10mm) 다이 |

|---|---|---|---|---|

| 1 인치 (25 mm) | 1960 | |||

| 2인치(51mm) | 275μm | 1969 | 9 | |

| 3인치(76mm) | 375μm | 1972 | 29 | |

| 4 인치 (100 mm) | 525μm | 1976 | 10그램 | 56 |

| 4.9 인치 (125 mm) | 625μm | 1981 | 95 | |

| 150 mm (5.9 인치, 통상은 「6 인치」라고 불립니다) | 675μm | 1983 | 144 | |

| 200 mm (7.9 인치, 통상은 「8 인치」라고 불립니다) | 725μm | 1992 | 53그램 | 269 |

| 300 mm (11.8 인치, 통상은 「12 인치」라고 불립니다) | 775μm | 2002 | 125그램[18] | 640 |

| 450mm(17.7인치) (표준)[19] | 925μm | – | 342그램 | 1490 |

| 675mm(26.6인치)(이론적)[20] | 알 수 없는 | – | 알 수 없는 | 3427 |

실리콘 이외의 소재를 사용해 성장한 웨이퍼는 같은 직경의 실리콘 웨이퍼와 두께가 다르다.웨이퍼 두께는 사용된 소재의 기계적 강도에 따라 결정됩니다. 웨이퍼는 취급 시 균열 없이 자체 중량을 지탱할 수 있을 정도로 두꺼워야 합니다.표로 나타낸 두께는 해당 공정이 도입된 시기와 관련이 있으며, 현재 IBM BiCMOS7WL 공정은 8인치 웨이퍼에 있지만 두께는 200μm에 불과합니다.두께와 직경에 [citation needed]따라 웨이퍼의 무게가 증가합니다.

웨이퍼 크기의 과거 증가

식각공정 등의 웨이퍼 제조공정 단위는 웨이퍼 면적 증가에 비례하여 더 많은 칩을 생산할 수 있으며, 단가 제조공정 단가는 웨이퍼 면적보다 더 느리게 상승한다.이는 웨이퍼 크기를 늘리기 위한 비용 기준이었습니다.200mm 웨이퍼에서 300mm 웨이퍼로의 전환은 2000년 초에 시작되었으며, 약 30-40%[21] 동안 다이당 가격을 낮췄습니다.직경이 큰 웨이퍼는 웨이퍼당 더 많은 다이(Die)를 허용합니다.

태양광 발전

이 섹션은 확장해야 합니다.추가해서 도움을 드릴 수 있습니다. (2020년 7월) |

M1 웨이퍼 크기(156.75mm)는 2020년 현재 중국에서 단계적으로 폐지되는 단계다.다양한 비표준 웨이퍼 사이즈가 생겨났기 때문에 M10 규격(182 mm)을 완전히 채택하기 위한 노력이 진행 중입니다.다른 반도체 제조 공정과 마찬가지로 다양한 유형의 장치 [citation needed]제조 공정의 차이에도 불구하고 이러한 크기 증가 시도의 주된 원동력은 비용 절감이었습니다.

결정 방향

웨이퍼는 규칙적인 결정구조를 가진 결정체로부터 성장하며, 실리콘은 5.430710Ω(0.5430710nm)[22]의 격자 간격의 다이아몬드 입방정 구조를 가진다.웨이퍼로 절단하면 표면이 결정 방향이라고 하는 몇 가지 상대적인 방향 중 하나로 정렬됩니다.방향은 (100) 또는 (111) 면이 [22]실리콘에 가장 일반적인 밀러 지수로 정의됩니다.단결정의 많은 구조적 및 전자적 특성이 매우 이방적이기 때문에 방향성은 중요하다.이온 주입 깊이는 웨이퍼의 결정 방향에 따라 달라지는데, 각 방향이 이송 [23]경로를 제공하기 때문입니다.

웨이퍼 분할은 일반적으로 잘 정의된 몇 가지 방향으로만 발생합니다.분할면을 따라 웨이퍼를 스코어링하면 웨이퍼를 개별 칩("다이즈")으로 쉽게 다이싱할 수 있으므로 평균 웨이퍼 상의 수십억 개의 개별 회로 소자를 여러 개별 [citation needed]회로로 분리할 수 있습니다.

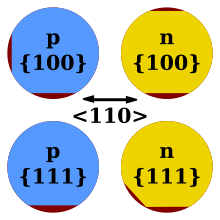

결정학적 방향 노치

직경 200mm 미만의 웨이퍼에는 웨이퍼의 결정면(일반적으로 {110}면)을 나타내는 평면이 하나 이상 절단되어 있습니다.이전 세대의 웨이퍼에서는 다른 각도의 플랫 한 쌍이 도핑 유형을 추가로 전달했습니다(규칙은 그림 참조).직경 200mm 이상의 웨이퍼는 도핑 [24]유형을 시각적으로 표시하지 않고 하나의 작은 노치를 사용하여 웨이퍼 방향을 전달합니다.

불순물 도핑

실리콘 웨이퍼는 일반적으로 100% 순수 실리콘은 아니지만 초기 불순물 도핑 농도는 cm당 103~10원자의1316 붕소, 인, 비소 또는 안티몬으로 형성되며, 용융액에 첨가되어 웨이퍼를 벌크 n형 또는 p형 [25]중 하나로 정의한다.단결정 실리콘의 원자 밀도가 cm당3 5×10인22 것과 비교하면 순도는 99.9999% 이상이다.웨이퍼에는 초기에 일부 간극 산소 농도를 제공할 수도 있습니다.탄소 및 금속 오염을 [26]최소화합니다.특히 전이 금속은 전자 [27]응용을 위해 10억분의 1 이하의 농도로 유지해야 한다.

450 mm 웨이퍼

과제들

생산성 향상 가능성에도 불구하고 450mm 전환에 상당한 저항이 있습니다.[21] 투자 수익률 부족에 대한 우려 때문입니다.또한 다이 간/엣지 투 에지 웨이퍼 변동 증가와 추가적인 에지 결함과 관련된 문제도 있습니다.450mm 웨이퍼는 300mm 웨이퍼보다 4배 이상 비싸고 장비비는 20~50%[28]가량 오를 것으로 예상된다.대형 웨이퍼용 반도체 제조장비가 비싸면 450mm 팹(반도체 제조설비 또는 공장)의 비용이 증가한다.리소그래프 제작자인 Chris Mack은 2012년에 450mm 웨이퍼의 전체 다이당 가격이 300mm 웨이퍼에 비해 10-20%밖에 절감되지 않을 것이라고 주장했는데, 이는 전체 웨이퍼 처리 비용의 50% 이상이 리소그래피와 관련이 있기 때문입니다.더 큰 450mm 웨이퍼로 변환하면 웨이퍼 [citation needed]면적이 아닌 웨이퍼 개수와 관련된 식각과 같은 공정 작업에만 다이당 가격이 절감됩니다.리소그래피와 같은 공정 비용은 웨이퍼 면적에 비례하며, 웨이퍼가 커도 다이 [29]비용에 대한 리소그래피의 기여도가 줄어들지 않습니다.

니콘은 2015년 450mm 리소그래피 장비를, 2017년 [30][31]양산할 계획이었다.ASML은 2013년 11월 칩 제조사 [32]수요 시기 불확실성을 이유로 450mm 리소그래피 장비 개발을 중단했다.

2012년 뉴욕주(SUNY Poly/College of Nanoscale Science and Engineering(CNSE), 인텔, TSMC, 삼성, IBM, 글로벌파운드리, 니콘사 등으로 구성된 그룹이 SEMCH와 유사한 글로벌 450mm 컨소시엄(G450C, 유사)이라는 민관 제휴를 맺었다.제조 인프라, 장비 프로토타입 및 도구를 통해 450mm 웨이퍼 레벨로 업계 전환을 조정할 수 있습니다."[33][34]CNSE는 2014년 중반 SEMIC [35]West에서 450mm 풀 패턴 웨이퍼를 최초로 공개한다고 발표했다.G450C는 2017년 초 450mm 웨이퍼 연구를 공개하지 않은 이유로 [36][37][38]해체하기 시작했다.다양한 소식통들은 그룹의 종말이 당시 SUNY [38][37][39]Poly의 CEO였던 Alain E. Kaloyeros에 대한 입찰 조작 혐의로 이루어진 후 일어났다고 추측하고 있다.300mm 제조 최적화가 비용이 많이 드는 450mm 전환보다 더 저렴하다는 사실을 업계가 깨달은 것도 [38]한몫했을 수 있습니다.

450mm의 연대표는 미정입니다.2012년에는 450mm 생산이 2017년부터 시작될 것으로 예상됐지만 전혀 [40][41]예상하지 못했다.마크 더컨 당시 마이크론테크놀로지 최고경영자(CEO)는 2014년 2월 450mm 채택이 무기한 연기되거나 중단될 것으로 예상했다."450mm가 발생할 것이라고는 확신할 수 없지만, 실제로 발생할 수 있는 정도라면, 앞으로 갈 길이 멀어요.마이크론이 적어도 [42]향후 5년간 450mm에 많은 돈을 쓸 필요는 없습니다.

그러기 위해서는 설비 커뮤니티에 많은 투자가 필요합니다.그리고 결국 고객이 그 기기를 구입하도록 하는 가치도 의심스럽다고 생각합니다."[43]2014년 3월 현재 Intel Corporation은 2020년까지 (20년 [44]말까지) 450mm 도입을 예상하고 있습니다.semiengineering.com의 Mark LaPedus는 2014년 중반에 칩 제조업체들이 450mm의 채택을 "예측 가능한 미래"로 연기했다고 보고했습니다.이 보고서에 따르면 일부 관측통들은 2018년부터 2020년까지를 예상한 반면, VLSI Research의 CEO인 G. Dan Hutchson은 2020년부터 [45]2025년까지 450mm 팹이 생산될 것으로 예상하지 않았다.

이번 조치로 300mm, 25200mm웨이퍼를 살해하여 로드된 SMIF에 대해 4.8kilograms[47][48][18]의 무게는 25300mm웨이퍼가 적재된 때문이기도 한 FOUP 300mm웨이퍼에 대해 7.5kilograms[46]weighs 완전 자동화 공장 대 200mm웨이퍼에 거의 자동화 공장, 300mm웨이퍼를 이용하여 주요 변화가 필요하다.두번 요구하는공장 노동자들의 체력 양, 그리고 증가하는 피로.300mm FOUP에는 핸들이 있어 손으로 움직일 수 있습니다.450mm FOUP는 450mm 웨이퍼 25개를 장착했을 때 무게가 45kg이므로[49] FOUP를 수동으로 처리하기 위해 크레인이[50] 필요하며 핸들은 더 이상 FOUP에 없습니다.FOUP는 무라텍이나 다이후쿠의 자재 취급 시스템을 사용하여 이동한다.이러한 주요 투자는 닷컴 버블에 따른 경기 침체기에 이루어졌으며, 그 결과 당초 450mm로 업그레이드되는 것에 큰 거부감을 갖게 되었다.최대 450mm의 램프업에서는 크리스털 잉곳은 3배 더 무겁고(총 중량 1톤) 냉각에 2-4배 더 오래 걸리며 프로세스 시간은 [51]두 배로 증가합니다.450mm 웨이퍼를 개발하려면 상당한 엔지니어링, 시간 및 비용이 필요합니다.

분석 다이카운트 추정

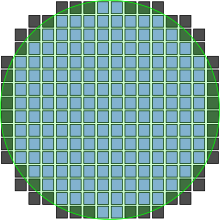

제조사들은 다이당 비용을 최소화하기 위해 단일 웨이퍼로 만들 수 있는 다이 수를 최대화하고자 합니다. 웨이퍼 다이싱의 제약으로 인해 다이는 항상 정사각형 또는 직사각형 모양을 갖습니다.일반적으로 이것은 해석 솔루션이 없는 계산적으로 복잡한 문제이며, 다이의 면적뿐만 아니라 가로 세로 비율(사각형 또는 직사각형)과 낙서선 또는 톱 차선의 폭, 정렬 및 테스트 구조물이 차지하는 추가 공간과 같은 기타 고려 사항에 따라 달라집니다.총 DPW 공식은 물리적으로 완전한 다이를 만드는 데 사용할 수 없기 때문에 손실된 웨이퍼 면적만을 설명하며, 총 DPW 계산은 결함 또는 파라미터 [citation needed]문제로 인한 항복 손실을 설명하지 않습니다.

그러나 웨이퍼당 총 다이 수(DPW)는 웨이퍼 대 다이 면적비의 1차 근사 또는 바닥 함수부터 추정할 수 있다.

어디에

- d는 웨이퍼 직경입니다(일반적으로 mm 단위).

- 의 폭(또는 톱니차선의 경우 공차+공차)을 포함한 각 다이의 크기(2).

이 공식은 웨이퍼에 들어갈 수 있는 다이의 수가 웨이퍼의 면적을 개별 다이의 면적으로 나눈 값을 초과할 수 없음을 나타냅니다.웨이퍼 표면에 완전히 배치되지 않은 부분 패턴의 다이스 면적을 포함하므로 항상 실제 최선의 경우 총 DPW를 과대 평가합니다(그림 참조).이 부분적인 무늬의 다이는 완전한 IC를 나타내지 않기 때문에 기능성 [citation needed]부품으로 판매할 수 없습니다.

일반적으로 이 간단한 공식은 가장자리 부분 다이를 고려하여 가장자리 보정을 추가합니다. 일반적으로 다이의 면적이 웨이퍼의 전체 면적에 비해 클 때 더 중요합니다.다른 제한 케이스(최종적으로 작은 다이 또는 무한히 큰 웨이퍼)에서는 에지 보정은 무시할 [citation needed]수 있다.

보정 계수 또는 보정 용어는 일반적으로 De [52]Vries가 인용하는 형식 중 하나를 취합니다.

- d면적비 – 둘레/(다이 대각선 길이))

- W ( 4 ) exp ( - S / DPW = \ ( { \ \ \ d^ { { ){\지수 인수에 의해 축척된 면적비)

- W † S ( - ) ( \ DPW =\ d^ { { 2다항식 인수로 스케일링된 면적비).

이러한 분석 공식을 브루트포스 계산 결과와 비교한 연구에 따르면 보정 계수를 단일성 위 또는 아래 값으로 조정하고 선형 다이 S를 대체함으로써 실제 다이 크기 및 석면비 범위에 걸쳐 공식을 보다 정확하게 만들 수 있습니다.가로 세로 비율이 [52]큰 다이의 ( ) /2 ( (H /) 평균 측면 길이):

- W ( S ) exp ( - S/d ) { \ style = \ left ( { \ \ display \ pi { 2 } } { 。

- W S ( - 1. S ) \ = frac \ displaystyle \ d^ {2 } { 1.

화합물 반도체

전자 산업에서 사용되는 웨이퍼에는 실리콘이 널리 사용되는 반면, 다른 화합물 III-V 또는 II-VI 재료도 사용되었습니다.Czochralski 방식으로 생산된 III-V 반도체인 GaAs(GaAs), 질화갈륨(GaN), 탄화실리콘(SiC) 등도 일반적인 웨이퍼 소재이며 GaN과 사파이어가 LED [8]제조에 광범위하게 사용되고 있다.

「 」를 참조해 주세요.

레퍼런스

- ^ Laplante, Phillip A. (2005). "Wafer". Comprehensive Dictionary of Electrical Engineering (2nd ed.). Boca Raton, Florida: CRC Press. p. 739. ISBN 978-0-8493-3086-5.

- ^ Reinhard Voelkel (2012). "Wafer-scale micro-optics fabrication". Advanced Optical Technologies. 1 (3): 135. Bibcode:2012AdOT....1..135V. doi:10.1515/aot-2012-0013. S2CID 137606531.

{{cite journal}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ T. Doi; I.D. Marinescu; Syuhei Kurokawa (2012). Advances in CMP Polishing Technologies, Chapter 6 – Progress of the Semiconductor and Silicon Industries – Growing Semiconductor Markets and Production Areas. Elsevier. pp. 297–304. doi:10.1016/B978-1-4377-7859-5.00006-5.

{{cite book}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ "High capacity epitaxial apparatus and method". google.com.

- ^ "Part 3: From 20 mm to 450 mm: The Progress in Silicon Wafer Diameter Nodes Report Series 04: Semiconductor Technology Now".

- ^ a b SemiSource 2006: Semiconductor International의 보충판.2005년 12월레퍼런스 섹션:칩 만드는 법디자인 뉴스에서 개작.리드 일렉트로닉스 그룹

- ^ Levy, Roland Albert (1989). Microelectronic Materials and Processes. pp. 1–2. ISBN 978-0-7923-0154-7. Retrieved 2008-02-23.

- ^ a b Grovenor, C. (1989). Microelectronic Materials. CRC Press. pp. 113–123. ISBN 978-0-85274-270-9. Retrieved 2008-02-25.

- ^ Nishi, Yoshio (2000). Handbook of Semiconductor Manufacturing Technology. CRC Press. pp. 67–71. ISBN 978-0-8247-8783-7. Retrieved 2008-02-25.

- ^ "Silicon Solar Cell Parameters". Retrieved 2019-06-27.

- ^ "Evolution of the Silicon Wafer". F450C.

- ^ "Wet Process". Omron Industrial Automation. Archived from the original on February 4, 2009. Retrieved November 26, 2008.

- ^ a b "Evolution Of Silicon Wafer F450C". F450C. Retrieved 2015-12-17.

- ^ "Silicon Wafer". Archived from the original on 2008-02-20. Retrieved 2008-02-23.

- ^ "Intel, Samsung, TSMC reach agreement about 450mm tech". intel.com.

- ^ 프레젠테이션/PDF/FEP.pdf ITRS 프레젠테이션(PDF)[영구 데드링크]

- ^ LaPedus, Mark (January 14, 2009). "450-mm fab debate surfaces". EE Times. Aspencore. Retrieved 2021-05-09.

As reported, Intel, TSMC and Samsung are separately pushing for the advent of 450-mm prototype fabs by 2012

- ^ a b c d e "450 mm Wafer Handling Systems". December 7, 2013. Archived from the original on December 7, 2013.

- ^ LaPedus, Mark. "Industry agrees on first 450-mm wafer standard". EETimes.

- ^ "The Evolution of AMHS". www.daifuku.com. Archived from the original on 2019-04-08. Retrieved 2018-12-02.

- ^ a b Undeveloped. "semiconductor.net – Domain Name For Sale". Undeveloped. Archived from the original on 2018-08-21. Retrieved 2018-08-20.

- ^ a b O'Mara, William C. (1990). Handbook of Semiconductor Silicon Technology. William Andrew Inc. pp. 349–352. ISBN 978-0-8155-1237-0. Retrieved 2008-02-24.

- ^ Nishi, Yoshio (2000). Handbook of Semiconductor Manufacturing Technology. Boca Raton, Florida: CRC Press. pp. 108–109. ISBN 978-0-8247-8783-7. Retrieved 2008-02-25.

- ^ Föll, Helmut (October 2019). "Wafer Flats". University of Kiel. Retrieved 2008-02-23.

{{cite web}}: CS1 maint :url-status (링크) - ^ Widmann, Dietrich (2000). Technology of Integrated Circuits. Springer. p. 39. ISBN 978-3-540-66199-3. Retrieved 2008-02-24.

- ^ Levy, Roland Albert (1989). Microelectronic Materials and Processes. pp. 6–7, 13. ISBN 978-0-7923-0154-7. Retrieved 2008-02-23.

- ^ Rockett, Angus (2008). The Materials Science of Semiconductors. p. 13. ISBN 978-0-387-25653-5.

- ^ Steve Schulz. "Collaborative advantage: Design impact of 450mm transition". EETimes. Retrieved 2022-03-08.

- ^ "Lithoguru Musings of a Gentleman Scientist". life.lithoguru.com. Retrieved 2018-01-04.

- ^ "Nikon appointing head of precision equipment business as new president" (Press release). Japan: Nikon Corp. semiconportal. May 20, 2014.

Nikon plans to introduce 450mm wafer lithography systems for volume production in 2017.

- ^ LaPedus, Mark (2013-09-13). "Litho Roadmap Remains Cloudy". semiengineering.com. Sperling Media Group LLC. Retrieved July 14, 2014.

Nikon planned to ship 'early learning tools' by 2015. 'As we have said, we will be shipping to meet customer orders in 2015,' said Hamid Zarringhalam, executive vice president at Nikon Precision.

- ^ "ASML 2013 Annual Report Form (20-F)" (XBRL). United States Securities and Exchange Commission. February 11, 2014.

In November 2013, following our customers’ decision, ASML decided to pause the development of 450 mm lithography systems until customer demand and the timing related to such demand is clear.

- ^ "G450C: a Global 450mm Consortium". VLSI Research. Retrieved 2021-07-26.

- ^ "The Bumpy Road To 450mm". Semiconductor Engineering. 2013-05-17. Retrieved 2021-07-26.

- ^ "World's First Fully Patterned 450mm Wafers Unveiled at SEMICON West SUNY Polytechnic Institute". sunypoly.edu. Retrieved 2021-07-26.

- ^ "450mm Officially On Hold 450mm.com". 450mm. 2017-01-17. Archived from the original on 2021-07-26. Retrieved 2021-07-26.

- ^ a b Rulison, Larry (2017-01-10). "Future of SUNY Poly's 450mm program in doubt". Times Union. Retrieved 2021-07-26.

- ^ a b c Rulison, Larry (2017-01-14). "NY: Demise of G450C wasn't over money". Times Union. Retrieved 2021-07-26.

- ^ "450mm Officially On Hold…". January 17, 2017. Archived from the original on July 26, 2021. Retrieved July 26, 2021.

- ^ Dylan McGrath. "First 450-mm fabs to ramp in 2017, says analyst". EETimes. Retrieved 2022-03-08.

- ^ "Construction of 450mm Fab 'Well Underway'". EETimes. 2013-08-15. Retrieved 2022-03-08.

- ^ Manners, David (2014-02-11). "450mm May Never Happen, says Micron CEO". Electronics Weekly. Retrieved 2022-02-03.

- ^ "450mm May Never Happen, says Micron CEO". electronicsweekly.com. 11 February 2014.

- ^ "Intel says 450 mm will deploy later in decade". 2014-03-18. Retrieved 2014-05-31.

- ^ LaPedus, Mark (2014-05-15). "Is 450mm Dead In The Water?". semiengineering.com. California: Sperling Media Group LLC. Archived from the original on 2014-06-05. Retrieved 2014-06-04.

Intel and the rest of the industry have delayed the shift to 450 mm fabs for the foreseeable future, leaving many to ponder the following question—Is 450 mm technology dead in the water? The answer: 450 mm is currently treading water.

- ^ "MW 300GT Wafer Cases Shin-Etsu Polymer Co., Ltd". www.shinpoly.co.jp.

- ^ "SMIF Pod-Chung King Enterprise Co., Ltd". www.ckplas.com.

- ^ "Wafer Cassette-Chung King Enterprise Co., Ltd". www.ckplas.com.

- ^ "Standing out from the Crowd on 450mm 450mm News and Analysis". Archived from the original on 2019-05-27. Retrieved 2019-05-27.

- ^ "H-Square Ergolift Cleanroom Lift Carts". www.h-square.com. Archived from the original on 2019-05-27. Retrieved 2019-05-27.

- ^ Undeveloped. "semiconductor.net – Domain Name For Sale". Undeveloped. Archived from the original on 2018-08-21. Retrieved 2018-08-20.

- ^ a b Dirk K. de Vries (2005). "Investigation of gross die per wafer formulas". IEEE Transactions on Semiconductor Manufacturing. 18 (February 2005): 136–139. doi:10.1109/TSM.2004.836656. S2CID 32016975.