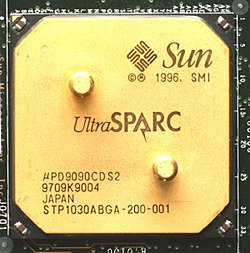

Ultra SPARC

UltraSPARC 200MHz UltraSPARC 마이크로프로세서 | |

| 일반 정보 | |

|---|---|

| 개시. | 1995 |

| 단종 | 1997 |

| 설계자 | Sun Microsystems |

| 성능 | |

| 최대 CPU 클럭 속도 | 143MHz ~200MHz |

| 아키텍처 및 분류 | |

| 명령 집합 | SPARC V9 |

| 물리 사양 | |

| 코어 |

|

| 역사 | |

| 전임자 | 슈퍼 SPARC II |

| 후계자 | UltraSPARC II |

UltraSPARC는 Sun Microsystems가 개발하고 Texas Instruments가 제작한 마이크로프로세서이며, 1995년 중반에 도입되었습니다.64비트 SPARC V9 명령 집합 아키텍처(ISA)를 구현하는 최초의 Sun 마이크로프로세서입니다.마크 트램블레이는 공동 마이크로아키텍트였습니다.

마이크로아키텍처

UltraSPARC는 명령을 순서대로 실행하는 4가지 슈퍼스칼라 마이크로프로세서입니다.9단계의 정수 파이프라인이 있습니다.

기능 단위

실행 유닛은 SuperSPARC에 비해 클럭 주파수를 높이기 위해 간략화되었습니다.간단한 예로 ALU가 SuperSPARC와 달리 캐스케이드되지 않아 클럭 주파수가 제한되지 않았습니다.

정수 레지스터 파일에는 32개의 64비트엔트리가 있어요SPARC ISA는 8개의 레지스터 창을 사용하므로 실제 레지스터 수는 144개입니다.레지스터 파일에는 7개의 읽기 포트와 3개의 쓰기 포트가 있습니다.정수 레지스터 파일은 두 개의 산술 로직 유닛과 로드/스토어 유닛에 레지스터를 제공합니다.두 개의 ALU는 모두 산술, 논리 및 시프트 명령을 실행할 수 있지만 곱셈 및 나눗셈 명령을 실행할 수 있는 것은 한 개뿐입니다.

부동소수점 유닛은 5개의 기능 유닛으로 구성됩니다.하나는 부동소수점 덧셈과 뺄셈, 하나는 곱셈, 하나는 나누기, 그리고 제곱근이다.두 개의 장치는 VIS(Visual Instruction Set)에서 정의된 SIMD 명령을 실행하기 위한 것입니다.부동소수점 레지스터 파일에는 32개의 64비트 레지스터가 포함되어 있습니다.5개의 읽기 포트와 3개의 쓰기 포트가 있습니다.

캐시

UltraSPARC에는 프라이머리와 세컨더리의 2가지 캐시 레벨이 있습니다.명령용과 데이터용 2개의 프라이머리 캐시가 있습니다.둘 다 용량이 16KB입니다.

UltraSPARC에는 필수 외부 세컨더리 캐시가 필요했습니다.캐시는 통합되며 용량은 512KB~4MB이며 직접 매핑됩니다.단일 사이클로 데이터를 반환할 수 있습니다.비율이 지원되지 않았기 때문에 외부 캐시는 마이크로프로세서와 동일한 주파수로 클럭된 동기 SRAM으로 구현됩니다.데이터 버스를 통해 액세스합니다.

제조

그것은 380만 개의 트랜지스터를 포함하고 있었다.Texas Instruments의 EPIC-3 공정에서 제조되었으며, 이 공정은 4단계 금속으로 이루어진 0.5μm의 상보 금속 산화물 반도체(CMOS) 공정입니다.UltraSPARC는 Texas Instruments가 0.5μm 공정까지 확장성이 뛰어나지 않고 성능 향상이 거의 없다고 주장했기 때문에 BiCMOS 공정에서 제작되지 않았습니다.이 프로세스는 TI의 MVP Digital Signal Processor(DSP; 디지털 신호 프로세서)에서 완벽하게 이루어졌으며, SuperSPARC에서 발생하는 제조 문제를 피하기 위해 UltraSPARC를 조립하기 위해 사용되기 전에 4레벨의 금속과 0.55 피처 사이즈 등 일부 기능이 누락되었습니다.

패키지

UltraSPARC는 521 접촉 플라스틱 볼 그리드 어레이(PBGA)로 패키지화되어 있습니다.