라이트 에치

Wright etch라이트 에치(Wright-Jenkins etch)는 트랜지스터, 마이크로프로세서, 메모리 및 기타 구성품을 만드는 데 사용되는 <100>-와 <111> 지향의 p- 및 n형 실리콘 웨이퍼의 결함을 밝히는 데 있어 우선적인 에치다.그러한 결함을 밝히고, 식별하고, 교정하는 것은 무어의 법칙이 예측한 길을 따라 진척되기 위해 필수적이다.1976년 마거릿 라이트 젠킨스(1936~2018)가 AZ 피닉스의 모토로라 주식회사에서 연구개발(R&D)에 근무하면서 개발했다.1977년에 출판되었다.[1]이 식각제는 최소 표면 거칠기 또는 외부 피팅으로 명확하게 정의된 산화 유발 적층 결함, 탈구, 소용돌이 및 변형 상태를 드러낸다.이러한 결함은 반바지 및 완성된 반도체 소자(트랜지스터 등)가 절연된 접합부에 부딪힐 경우 전류 누출의 원인으로 알려져 있다.상온에서 비교적 낮은 에치 속도(분당 약 1마이크로미터)는 에치 제어를 제공한다.이 식각제의 긴 저장 수명은 용액을 대량으로 저장할 수 있게 한다.[1]

에치 공식

라이트 에치의 구성은 다음과 같다.

- 60ml 농축 HF(수소화산)

- 30ml 농축 HNO3(Nitric acid)

- 2g Cu(NO3)2 . 3HO2 (Copper II Nitrate 3hydrate)

- 60ml 농축 CHCOOH3(아세트산)

- 60ml HO2(이온수)

용액을 혼합할 때, 질산동 구리를 지정된 양의 물에 먼저 용해하여 최상의 결과를 얻는다. 그렇지 않으면 혼합 순서는 중요하지 않다.

에치 메커니즘

라이트 에치는 실리콘 표면의 일반적인 결함에 대한 잘 정의된 에치 수치를 지속적으로 산출한다.이 속성은 공식에서 선택된 화학 물질의 상호작용에 기인한다.로빈스와 슈워츠는[2][3][4] HF, HNO3 및 HO2 시스템과 HF, HNO3, HO2 및 CHCOOH3(초산) 시스템을 사용하여 실리콘의 화학 식각을 자세히 설명했다.간단히 말해서, 실리콘 에칭은 2단계 과정이다.첫째, 실리콘의 상단 표면은 적절한 산화제에 의해 수용성 산화물로 변환된다.그리고 나서 결과 산화층은 적절한 용매, 보통 HF에 용해되어 표면에서 제거된다.이것은 에치 사이클 동안 연속적인 과정이다.수정 결함을 묘사하기 위해서는 결점 부위를 주변보다 느리거나 빠른 속도로 산화시켜 우선 에치 공정에서 마운드나 핏을 형성해야 한다.

현재 시스템에서는 실리콘이 HNO3, CrO3 용액(이 경우 pH가 낮기 때문에 CrO272− 이온을 함유하고 있음 - 크롬산 위상도를 참조)과 Cu(NO3)로 산화된다.2강한 산화제인 디크롬산 이온은 주요 산화제로 간주된다.공식에 명시된 HNO와3 CrO3 용액의 비율은 우월한 식각면을 생성한다.다른 비율의 경우 바람직하지 않은 마감재가 발생한다.소량 Cu(NO3)를 추가하면서 결함의 정의가 강화되었다.2따라서 Cu(NO3)2는 결점 현장의 국부적 미분산화율에 영향을 미치는 것으로 생각된다.아세트산을 첨가한 덕분에 에칭된 실리콘의 배경 표면이 매끈하게 마무리되었다.이러한 효과는 식각 중 거품이 생기는 것을 막는 아세트산의 습윤 작용에 기인한다는 이론이 있다.

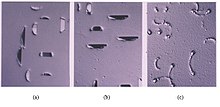

결함을 보여주기 위한 모든 실험 우선 식각은 세척 및 산화 웨이퍼에서 수행되었다.모든 산화는 1200°C에서 증기로 75분간 수행되었다.그림 1 (a)는 Wright etch 30분 후 <100> 지향 웨이퍼에서 산화 유발 적층 결함을 보여주고, (b)와 (c) 20분 후 각각 <100>-와 <111> 지향 웨이퍼에서 탈구 구멍을 보여준다.[1]

그림 1 (a)는 Wright 에치 30분 후 <100> 지향, 7-10Ω-cm의 붕소 도포 웨이퍼에 산화 유발 적층 결함을 나타낸다(이 그림의 A 화살표는 표면을 교차하는 결함의 형태를 가리키고, B는 벌크 결함을 가리킨다).그림 1 (b)와 (c)는 20분 후 각각 <100>-와 <111> 지향 웨이퍼에 탈구 구멍을 보여준다.[1]

요약

이 에치 공정은 사전 가공된 광택 실리콘 웨이퍼의 무결성을 판단하거나 웨이퍼 가공 중 어느 지점에서나 유발될 수 있는 결함을 드러내는 빠르고 신뢰할 수 있는 방법이다.라이트 에치는 시르틀과[5] 세코 에칭이 밝힌 수치와 비교했을 때 적층 단층 및 탈구 에칭 수치를 밝히는 데 우수하다는 것이 입증됐다.[6]

이 에치는 다양한 웨이퍼 가공 단계에서 전기 소자의 고장 분석에 널리 사용된다.[7][8]이에 비해 라이트 에치는 실리콘 결정의 결함을 밝히는 데 선호되는 식각제였다.[7][8]

그림 2는 각각 라이트 에치, 세코, 시르틀 에치 이후의 <100> 지향 웨이퍼에 대한 산화 유발 적층 결함 디라인의 비교를 보여준다.[1]

그림 3은 라이트 에치, 세코, 시르틀 에치 이후의 <100> 지향 웨이퍼에 대한 탈구 피트의 서열을 비교한 것이다.최종 그림 4는 라이트 에치, 세코, 시르틀 에치(Sirtl etch)와 각각 에칭한 후 <111> 지향 웨이퍼에 나타난 탈구 구덩이를 비교한 것이다.[1]

그림 3은 산화 및 우선 에칭 후 <100> 지향, 10-20Ω-cm, 붕소 도핑 웨이퍼의 탈구 디라인화를 비교한 것이다. (a)[1] 20분 후 라이트 에치, (b) 10분 후 세코 에치 및 (c) 6분 Sirtl 에치.

그림 4는 산화 및 우선 에칭 후 <111> 지향, 10-20Ω-cm, 붕소 도포 웨이퍼의 탈구 디라인화를 비교한 것이다. (a) 10분 후 라이트 에치, (b) 10분 후 세코 에치 및 (c) 3분 Sirtl 에치.화살표는 미끄러진 방향을 가리킨다.[1]

참조

- ^ a b c d e f g h i j k l Wright Jenkins, Margaret (May 1977) [1976-08-27, 1976-12-16]. "A New Preferential Etch for Defects in Silicon Crystals". Journal of the Electrochemical Society. Motorola Incorporated, Motorola Semiconductor Products Group, Phoenix, Arizona, USA: The Electrochemical Society (ECS). 124 (5): 757–759. doi:10.1149/1.2133401. Retrieved 2019-04-06.

- ^ Robbins, Harry; Schwartz, Bertram (June 1959) [1958-04-30]. "Chemical Etching of Silicon: Part I. The System HF, HNO3, H2O, and HC2H3O2". Journal of the Electrochemical Society. The Electrochemical Society (ECS). 106 (6): 505–508. doi:10.1149/1.2427397.

- ^ Robbins, Harry; Schwartz, Bertram (February 1960) [1959-04-06]. "Chemical Etching of Silicon: Part II. The System HF, HNO3, H2O, and HC2H3O2". Journal of the Electrochemical Society. The Electrochemical Society (ECS). 107 (2): 108–111. doi:10.1149/1.2427617.

- ^ Robbins, Harry; Schwartz, Bertram (August 1961) [1960-08-08, 1960-12-28]. "Chemical Etching of Silicon: Part III. A Temperature Study in the Acid System". Journal of the Electrochemical Society. The Electrochemical Society (ECS). 108 (4): 365–372. doi:10.1149/1.2428090.

- ^ Sirtl, Erhard; Adler, Annemarie (August 1961). "Chromsäure-Flussäure als Spezifisches System zur Ätzgrubenentwicklung auf Silizium". Zeitschrift für Metallkunde (ZfM) (in German). 52 (8): 529–534. NAID 10011334657.

- ^ Secco d'Aragona, F. (July 1972) [1971-12-20, 1972-03-03]. "Dislocation Etch for (100) Planes in Silicon". Journal of the Electrochemical Society. The Electrochemical Society (ECS). 119 (7): 948–951. doi:10.1149/1.2404374.

- ^ a b Su, Garth K.; Jin, Da; Kim, Sung-Rae; Chan, Tze-Ho; Balan, Hari; Lin, Yung-Tao; Han, Kyung-Joon; Hsia, Steve (December 2003). "CMOS: Defect Avoidance - Pipeline Defects in Flash Devices Associated with Rings OSF" (PDF). Semiconductor Manufacturing: 144–151. Archived from the original (PDF) on 2016-03-03. Retrieved 2019-04-06.

- ^ a b "Chapter 6". Defect Etching in Silicon. 2002. Archived from the original on 2019-04-06. Retrieved 2019-04-06.