작동 증폭기 애플리케이션

Operational amplifier applications이 글에서는 대표적인 운영 증폭기 용도에 대해 설명한다.비이상 작동 증폭기의 등가 회로는 유한 입력 임피던스, 0이 아닌 출력 임피던스, 유한 게인을 가진다.실제 op-amp는 도표와 같이 여러 가지 비이상적 특징을 가지고 있지만 여기서는 단순화된 개략도 표기법을 사용하며, 기기 선택 및 전원 공급 연결과 같은 많은 세부 사항은 표시하지 않는다.작동 증폭기는 부정적인 피드백과 함께 사용하도록 최적화되었으며, 이 기사는 부정적인 피드백 어플리케이션에 대해서만 논한다.긍정적인 피드백이 필요한 경우, 대조군이 일반적으로 더 적합하다.자세한 내용은 비교기 응용 프로그램을 참조하십시오.null

현실적 고려

작동 증폭기 매개 변수 요구 사항

특정 기기가 응용 프로그램에 사용되려면 특정 요건을 충족해야 한다.작동 증폭기는 반드시

- 큰 개방 신호 게인(초기 집적 회로 예에서 20만 전압 게인 획득) 및

- 피드백 네트워크에 존재하는 값과 관련하여 큰 입력 임피던스를 가지고 있다.

이러한 요건이 충족되면, op-amp는 이상적인 것으로 간주되며, 가상 접지의 방법을 사용하여 아래 op-amp 회로의 '행동'을 빠르고 직관적으로 파악할 수 있다.null

구성 요소 사양

실제 솔리드 스테이트 op-amp 회로에 사용되는 저항기는 일반적으로 KΩ 범위에 있다.1MΩ보다 훨씬 큰 저항기는 과도한 열 소음을 유발하고, 바이어스 또는 누출 전류로 인해 회로 작동이 상당한 오류에 노출될 수 있다.null

입력 바이어스 전류 및 입력 오프셋

실용적인 작동 증폭기는 바이어스 요구사항(양극성 접합 트랜지스터 기반 입력의 경우) 또는 누출(MOSFET 기반 입력의 경우)으로 인해 각 입력에서 작은 전류를 끌어낸다.null

이러한 전류는 입력에 연결된 저항을 통해 흐르며 이러한 저항에서 작은 전압 강하를 생성한다.피드백 네트워크의 적절한 설계는 아래와 같이 입력 편향 전류 및 공통 모드 이득과 관련된 문제를 완화시킬 수 있다.경험적 접근 규칙은 각 입력 단자의 임피던스가 "돌봄"이 동일한지 확인하는 것이다.null

입력 바이어스 전류가 일치하지 않는 범위까지 유효 입력 오프셋 전압이 존재하게 되어 회로 성능에 문제가 발생할 수 있다.많은 상용 op-amp 제품들은 입력의 균형을 맞추기 위해 작동 증폭기를 조정하는 방법을 제공한다(예: 전위차계에 부착된 외부 전압 선원과 상호작용할 수 있는 "오프셋 null" 또는 "균형" 핀).또는 오프셋 효과의 균형을 맞추기 위해 입력 중 하나에 조정 가능한 외부 전압을 추가할 수 있다.설계가 하나의 입력을 접지 단락 회로로 변환하도록 요구하는 경우, 그 단락은 오프셋 문제를 완화하도록 조정될 수 있는 가변 저항으로 대체될 수 있다.null

MOSFET 기반 입력 단계를 사용하는 작동 증폭기에는 많은 설계에서 무시할 수 있는 입력 누출 전류가 있다.null

전원 공급 효과

아래의 (간단한) 작동 증폭기 설계에는 전원 공급기가 표시되지 않지만, 그럼에도 불구하고 이 설계는 존재하며 작동 증폭기 회로 설계에 매우 중요할 수 있다.null

공급소음

전원 공급 장치 결함(예: 전원 신호 리플, 0이 아닌 소스 임피던스)은 이상적인 작동 증폭기 동작에서 현저한 편차를 초래할 수 있다.예를 들어, 작동 증폭기는 출력이 전원 공급기 입력에 나타나는 신호를 얼마나 잘 거부할 수 있는지를 나타내는 지정된 전원 공급기 거부 비율을 가지고 있다.전원 공급 입력은 설계의 거의 모든 구성 요소에 의해 전력 공급이 사용되기 때문에 대형 설계에서 소음이 자주 발생하며, 인덕턴스 효과는 전류가 모든 구성 요소에 동시에 전달되는 것을 방지한다.그 결과, 어떤 구성품이 대규모 전류 주입을 필요로 할 때(예: 한 상태에서 다른 상태로 자주 전환되는 디지털 구성품) 근처의 구성품은 전원 공급 장치에 연결될 때 처짐을 경험할 수 있다.이 문제는 각 전원 공급 장치 핀과 접지에 연결된 바이패스 캐패시터를 적절히 사용하면 완화할 수 있다.구성 요소에 의해 전류의 버스트가 필요한 경우, 구성 요소는 가까운 캐패시터로부터 전류를 직접 수신하여 전원 공급을 우회할 수 있다(그 다음 전원 공급기에 의해 천천히 재충전됨).null

신호 경로에서 전원 공급 전류 사용

또한, 전원 공급 장치에서 작동 증폭기로 유입되는 전류는 작동 증폭기의 기능을 증대시키는 외부 회로에 대한 입력으로 사용될 수 있다.예를 들어, 작동 증폭기의 출력은 증폭기에 의해 생성된 안전 범위를 벗어나는 신호를 생성하기 위해 필요하기 때문에 특정 고게인 애플리케이션에 적합하지 않을 수 있다.이 경우 외부 푸시-풀 증폭기는 작동 증폭기 안팎으로 전류에 의해 제어될 수 있다.따라서 작동 증폭기는 음의 피드백 경로가 그러한 범위를 훨씬 벗어나 큰 출력 신호를 포함하도록 허용하면서 공장 지정 범위 내에서 작동할 수 있다.[1]null

증폭기

첫 번째 예는 차동 증폭기인데, 여기서 인버팅, 비인버팅 및 SUM 앰프, 전압 추종자, 통합자, 차별화자 및 집레이터를 포함한 다른 많은 응용 프로그램을 파생할 수 있다.null

디퍼렌셜 앰프(차이 앰프)

입력 간 전압 차이를 증폭한다.null

- "차동증폭기"라는 이름은 이 페이지에도 나와 있는"차동증폭기"와 혼동해서는 안 된다.

표시된 회로는 두 전압의 차이를 계산하여 일부 게인수를 곱한다.출력 전압

또는 공통 모드 입력 V와com 차이 입력 V의dif 함수로 표현된다.

출력 전압은

이 회로가 입력 단자의 전압 차이에 비례하는 신호를 생성하기 위해서는 V 용어의com 계수(공통 모드 이득)가 0 또는 0이어야 한다.

이 제약조건이[nb 1] 있는 상태에서, 이 회로의 공통 모드 제거 비율은 무한히 크고, 출력은 무한히 크다.

여기서 단순 표현 Rf/R은1 디퍼렌셜 앰프의 폐쇄 루프 게인을 나타낸다.null

폐쇄 루프 이득이 단합일 경우 특별한 경우는 다음과 같이 차등 추종자가 된다.

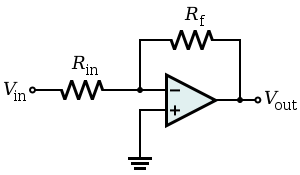

인버팅 증폭기

인버팅 앰프는 해당 회로의 비인버팅 입력 V가2 접지되고, 인버팅 입력 V가1 상기 V와in 함께 식별되는 디퍼렌셜 앰프의 특수한 경우다.폐쇄 루프 이득은 Rf/R이므로in

- = -R V V in R_{\in}text{}}}V_{\in}\ .

위의 단순화된 회로는 R과2 R의g 한계에 있는 차동 증폭기와 매우 작다.그러나 이 경우 회로는 R과f R의in 불일치로 인해 입력 바이어스 전류 드리프트에 취약해진다.

위의 게인 방정식을 직관적으로 보려면 R:로in 전류를 계산하십시오.

그런 다음 이 동일한 전류가f R을 통과해야 함을 상기하십시오(V− = V+ = 0).

기계적 비유는 V 노드−(R과in Rf 사이)를 지상의 전위에 있는 풀크럼으로 하는 시소이다.V는in 풀크럼에서 R의in 길이에 있고, V는out R의f 길이에 있다.V가in "지하"로 내려갈 때 출력 V는out 시소의 균형을 맞추기 위해 비례적으로 상승하며, 그 반대도 마찬가지다.[2]null

op-amp의 음극 입력이 가상 접지 역할을 하므로 이 회로의 입력 임피던스는 R과in 동일하다.

비반입 증폭기

비인버팅 앰프는 해당 회로의 인버팅1 입력 V가 접지된 디퍼렌셜 앰프의 특수한 경우로서, 비인버팅 입력 V는2 위의 V와in 함께 R1 ≫ R으로2 식별된다. 바로 위의 회로를 참조한다.

- .

이 게인 방정식을 직관적으로 보려면 가상 접지 기법을 사용하여 저항기1 R:

그런 다음 이 동일한 전류가2 R을 통과해야 한다는 점을 상기한다. 따라서:

인버팅 앰프와 달리 비인버팅 앰프는 1 이하의 이득이 있을 수 없다.

기계적 비유는 R의1 한 단자가 지반 전위에 있는 2등급 레버를 말한다.V는in 풀크럼에서 R의1 길이에 있고out, V는2 R의 길이에 있다.V가in "지상"으로 상승할 때 출력out V는 레버에 비례하여 상승한다.null

단순화된 비삽입 증폭기의 입력 임피던스는 높음:

여기서 Z는dif 차동 신호에 대한 op-amp의 입력 임피던스, A는OL op-amp의 개방 루프 전압 이득(주파수에 따라 달라짐), B는 피드백 계수(입력으로 되돌아가는 출력 신호의 비율)이다.[3][4]이상적인OL op-amp의 경우, A 무한과 Zdif 무한으로 입력 임피던스도 무한하다.그러나 이 경우 회로는 V와+ V− op-amp 입력을 구동하는 임피던스 사이의 불일치로 인해 입력 바이어스 전류 드리프트에 취약하게 된다.null

피드백 루프도 마찬가지로 출력 임피던스를 감소시킨다.

여기서 Z는out 피드백이 있는 출력 임피던스, Z는OL 오픈 루프 출력 임피던스다.[4]null

전압 추종자(유니티 버퍼 앰프)

로드 효과를 제거하기 위한 버퍼 앰프로 사용된다(예: 소스 임피던스가 높은 장치를 입력 임피던스가 낮은 장치에 연결).null

- =현실적으로 op-amp 자체의 차동 입력 임피던스(1MΩ ~ 1TΩ)에 op-lamp의 오픈 루프 게인을 곱한 값)

이 피드백 시스템은 강한(즉, 통합 이득) 피드백과 실제 작동 증폭기의 비이상적 특성 때문에 안정성 여유가 나쁜 경향이 있다.따라서 시스템은 충분한 용량성 부하에 연결되면 불안정할 수 있다.이 경우, 지연 보상 네트워크(예: 저항을 통해 전압 추종자에 부하를 연결하는 것)를 사용하여 안정성을 회복할 수 있다.운용 증폭기용 제조자 데이터 시트는 외부 보상망의 구성요소 선택을 위한 지침을 제공할 수 있다.또는 보다 적절한 내부 보상이 있는 다른 작동 증폭기를 선택할 수 있다.null

입력 및 출력 임피던스는 비반복 증폭기와 같은 방식으로 B=1로 피드백 루프의 영향을 받는다.[3][4]null

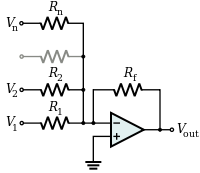

SUM 증폭기

SUM 앰프는 몇 개의 (가중) 전압을 합한 값:

- = 2= = n 및 독립된 경우

- = 2= = n= = 일 때

- 출력이 반전됨

- n번째 입력의 입력 임피던스는 Z = R -{\은(는) 가상 접지)

계측 증폭기

매우 높은 입력 임피던스, 높은 공통 모드 제거, 낮은 DC 오프셋 및 매우 정확하고 낮은 노이즈 측정 시 사용되는 기타 특성 결합

오실레이터

빈교 오실레이터

매우 낮은 왜곡 사인파를 생성한다.전구 또는 다이오드의 형태로 음의 온도 보정을 사용한다.null

필터

작동 증폭기는 고역 통과, 저역 통과, 대역 통과, 거부 및 지연 기능을 제공하는 능동 필터의 구조에 사용할 수 있다.op-amp의 높은 입력 임피던스와 이득은 요소 값의 직접적인 계산을 가능하게 하며, 필터 또는 후속 단계의 단계 로딩 효과에 대한 우려는 거의 없이 원하는 필터 위상의 정확한 구현을 가능하게 한다.그러나 활성 필터를 구현할 수 있는 빈도는 제한적이다. 증폭기의 동작이 필터의 기본 설계에서 가정된 이상적인 동작에서 크게 벗어나면 필터 성능이 저하된다.null

비교기

작동 증폭기는 필요한 경우 대조군으로 작용하도록 강제될 수 있다.입력 전압 간의 가장 작은 차이는 엄청나게 증폭되어 출력이 거의 공급 전압으로 스윙하게 된다.단, 출력량이 슬루 레이트가 더 높고 전원 공급 레일에 도달할 수 있기 때문에 이 목적에 전용 비교기를 사용하는 것이 보통 더 좋다.일부 op-amps는 입력에 대조군으로 사용을 금지하는 클램핑 다이오드가 있다.[5]null

통합 및 차별화

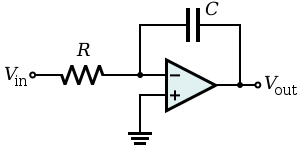

통합업체 전환

통합자는 아날로그 컴퓨터, 아날로그-디지털 변환기, 파동 쉐이핑 회로에서 주로 사용된다.null

입력 신호 Vin(t)를 시간 간격 t, t0 < t < t)에1 걸쳐 통합(및 반전)하며, 출력 전압은 시간1 t = t

여기서 Vout(t0)는 시간 t = t에서0 회로의 출력 전압을 나타낸다.이는 출력 전압이 시간 t0 < t < t > t에1 따라 입력 전압의 시간 적분에 비례하는 양만큼 변화한다고 말하는 것과 같다.null

이 회로는 DC에서 단일 폴(= 0 {\ = 0을 가진 로우패스 전자 필터로 볼 수 있다.null

실제 애플리케이션에서 커패시터 C가 주기적으로 방전되지 않는 한 출력 전압은 결국 작동 증폭기의 작동 범위 밖으로 표류한다.이는 다음과 같은 모든 조합에 기인할 수 있다.

- 입력 V에는in 0이 아닌 DC 성분이 있으며,

- 입력 바이어스 전류가 0이 아닌 경우,

- 입력 오프셋 전압이 0이 아니다.[6]

약간 더 복잡한 회로는 두 번째 문제를 개선시킬 수 있고, 어떤 경우에는 첫 번째 문제도 개선시킬 수 있다.null

여기서 피드백 저항기 R은f 캐패시터 C에f 대한 방전 경로를 제공하는 반면, 비반복 입력 R의n 직렬 저항기는 정확한 값이 되면 입력 바이어스 전류와 공통 모드 문제를 완화한다.이 값은 R과i R의f 병렬 저항 또는 속기 표기법을 사용하는 값이다.

입력 신호와 출력 신호의 관계는 이제

차별화 요소 반전

시간 경과에 따른 (반전) 신호 구별:

서 및 은(는) 시간의 함수다.null

반전 차별화기의 전송 기능은 원점에 단일 0을 가진다(즉, 여기서 각도 주파수 = 0 차별화 증폭기의 하이패스 특성은 회로가 아날로그 서보 루프(예: 파생상품 이득이 큰 PID 컨트롤러)에서 사용될 때 안정성 문제로 이어질 수 있다.특히, 근본 위치 분석에서 알 수 있듯이, 피드백 이득의 증가는 차별화 요소에 의해 도입된 DC 제로에서 한계 안정성을 향해 폐쇄 루프 폴을 구동할 것이다.null

합성 원소

인덕턴스 집광기

인덕터를 시뮬레이션한다(즉, 비용이 많이 드는 인덕터를 사용하지 않고 인덕턴스를 제공한다).회로는 캐패시터를 통해 흐르는 전류가 인덕터를 통과하는 전압으로 작용한다는 사실을 이용한다.이 회로에 사용되는 캐패시터는 시뮬레이션하는 인덕터보다 기하학적으로 작고, 캐패시턴스는 환경변화에 따른 가치변동의 영향을 덜 받는다.이 회로가 물리적 인덕터보다 우수할 수 있는 애플리케이션은 가변 인덕턴스를 시뮬레이션하거나 매우 큰 인덕턴스를 시뮬레이션하고 있다.null

이 회로는 인덕터의 후방 EMF 특성에 의존하는 용도에 제한적이다. 이 효과는 집광기 회로에서 op-amp의 전압 공급으로 제한되기 때문이다.null

음극 임피던스 컨버터(NIC)

모든 신호 발생기에 대해 음수 값을 갖는 저항을 생성한다.null

이 경우 입력 전압과 입력 전류 사이의 비율(입력 저항 포함)은 다음과 같다.

일반적으로 성분 1 은 저항기가 될 필요가 없으며 임피던스로 설명할 수 있는 모든 성분이 될 수 있다.null

비선형

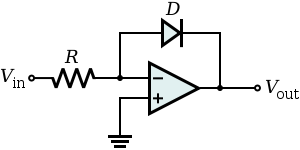

정밀 정류기

수동 정류기 회로에서 전방 바이어스 다이오드를 통과하는 전압 강하 V는F 원하지 않는다.이 활성 버전에서는 음의 피드백 루프에서 다이오드를 연결하면 문제가 해결된다.op-amp는 부하에 걸친 출력 전압을 입력 전압과 비교하고 자체 출력 전압을 V 값으로F 증가시킨다.그 결과 전압 강하 V는F 보상되고, 회로는 VF = 0V로 이상적인(슈퍼) 다이오드로 매우 가깝게 동작한다.

이 회로는 느린 음의 피드백과 많은 비이상적인 op-amps의 낮은 슬루 레이트로 인해 고주파에서 속도 제한이 있다.null

로그 출력

입력 전압 V와in 출력 전압 Vout 사이의 관계는 다음과 같다.

여기서 나는S 포화 전류, V는T 열전압이다.null

작동 증폭기가 이상적이라고 간주되면, 뒤집는 입력 핀은 사실상 접지되므로, 소스에서 저항기로 흐르는 전류(따라서 op-amp 입력이 전류를 끌어들이지 않기 때문에 다이오드를 통해 출력으로 가는 전류)가 된다.

다이오드를 통과하는 전류D 위치알려진 바와 같이 다이오드의 전류와 전압의 관계는

이 값은 전압이 0보다 클 때 다음과 같이 근사치할 수 있다.

이 두 공식을 함께 넣고 출력 전압이 다이오드에 걸친 전압의 음수(Vout = -VD)임을 고려하면 관계가 증명된다.null

이 구현에서는 온도 안정성 및 기타 비이상적인 영향을 고려하지 않는다.null

지수출력

의 입력 전압 와 출력 전압 전압 사이의 관계는 다음과 같다.

서 I S 은(는) 포화 전류로, V V_은 열전압이다.null

작동 증폭기의 이상을 고려하여 음극 핀은 사실상 접지되어 있으므로 다이오드를 통과하는 전류는 다음과 같이 주어진다.

전압이 0보다 클 경우 다음과 같이 근사치를 계산할 수 있다.

출력 전압은 다음에 의해 주어진다.

기타 응용 프로그램

참고 항목

메모들

- ^ 관계의 왼쪽을 뒤집는 입력의 폐쇄 루프 이득으로, 오른쪽을 비반복 입력의 이득으로 생각한다면, 이 두 양을 일치시키면 1 및 }}의 공통 모드 전압에 무감각한 출력을 제공한다

참조

- ^ 폴 호로위츠와 윈필드 힐, 전자기술.2부.케임브리지 대학교 출판부, 1989년 ISBN0-521-37095-7

- ^ 기본 전자 이론, Delton T.호른, 4번가McGraw-Hill Professional, 1994, 페이지 342–343.

- ^ a b "Benefits of Negative Feedback". HyperPhysics. Retrieved 2018-05-07.

- ^ a b c Simpson, Robert E. (1987). "7.2 Negative Voltage Feedback". Introductory electronics for scientists and engineers (2nd ed.). Boston: Allyn and Bacon. p. 291. ISBN 0205083773. OCLC 13821010.

input impedance of an amplifier without negative feedback is increased by adding negative feedback. .. .. output impedance .. is decreased ..

- ^ http://e2e.ti.com/blogs_/archives/b/thesignal/archive/2012/03/14/op-amps-used-as-comparators-is-it-okay.aspx

- ^ "AN1177 Op-Amp Precision Design: DC Errors" (PDF). Microchip. 2 January 2008. Archived (PDF) from the original on 2013-01-11. Retrieved 26 December 2012.

추가 읽기

외부 링크

| Wikibook Electronics는 Op-Amps라는 주제에 관한 페이지를 가지고 있다. |

- "Single supply op-amp circuit collection" (PDF). (163 KiB)

- "Op-amp circuit collection" (PDF). (2980 KiB)

- "A Collection of Amp Applications" (PDF). (1.06MiB) – 아날로그 장치 응용 프로그램 노트

- "Basic OpAmp Applications" (PDF). (173 KiB)

- "Handbook of operational amplifier applications" (PDF). (2.00 MiB) – Texas Instruments Application 노트

- 2009-04-08년 웨이백 기계에 보관된 작동 증폭기를 사용한 저측 전류 감지

- "Log/anti-log generators, cube generator, multiply/divide amp" (PDF). Archived from the original (PDF) on 2008-05-09. (165KiB)

- 선형 변수 성분의 로그 변수 이득

- D에 의한 작동 증폭기를 이용한 임피던스 및 입장 변환.H. 신골드

- 사진과 실제 파형을 포함한 매우 실용적이고 읽기 쉬운 고속 앰프 기술

- 단일 공급 op-amp 회로 수집

- 사용하지 않는 op-amp를 적절하게 종료

(는) 포화

(는) 포화