위들러 전류 소스

Widlar current source

Widlar 전류 소스는 출력 트랜지스터에만 대한 이미터 퇴화 저항기를 통합한 기본 2 트랜지스터 전류 미러의 개조로서, 전류 소스가 중간 저항 값만 사용하여 저전류를 발생시킬 수 있다.[1][2][3]

Widlar 회로는 양극성 트랜지스터, MOS 트랜지스터 및 진공 튜브와 함께 사용될 수 있다.예로는 741개의 작동 증폭기가 있으며,[4] 위들러는 많은 설계에서 회로를 부품으로 사용하였다.[5]

이 회로는 발명가 밥 위들러의 이름을 따서 명명되었으며 1967년에 특허를 얻었다.[6][7]

DC 분석

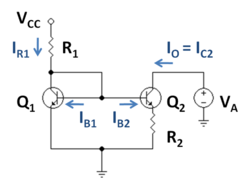

그림 1은 양극 트랜지스터를 사용하는 위들러 전류원의 예로서, 이미터 저항기 R이2 출력 트랜지스터 Q에2 연결되어 있으며, Q에1 비해 Q의2 전류를 감소시키는 효과가 있다.이 회로의 핵심은 저항기2 R을2 가로지르는 전압 강하가 트랜지스터 Q의 베이스-이미터 전압에서 차감되어 이 트랜지스터를 트랜지스터 Q에1 비해 꺼지게 하는 것이다.이러한 관찰은 그림 1의 회로 양쪽에서 발견된 기본 전압 표현식을 다음과 같이 동일시함으로써 표현된다.

여기서 β는2 출력 트랜지스터의 베타 값이며, 부분적으로 두 트랜지스터의 전류가 매우 다르기 때문에 입력 트랜지스터와 같지 않다.[8]변수 I는B2 출력 트랜지스터의 기본 전류로, V는BE 베이스-이미터 전압을 가리킨다.이 방정식은 (충격 다이오드 법칙 사용)을 암시한다.

Eq. 1

여기서 V는T 열전압이다.

이 방정식은 전류 모두 스케일 전류 I 및S1 I보다S2 훨씬 크다는 근사치를 만들어낸다. 단전에 가까운 전류 레벨을 제외하고 유효하다.다음에서 척도 전류는 동일하다고 가정하며, 실제로는 이를 구체적으로 정리할 필요가 있다.

지정된 전류를 사용하는 설계 절차

미러를 설계하려면 출력 전류가 두 저항 값 R 및1 R과2 관련되어야 한다.기본적인 관찰은 출력 트랜지스터의 컬렉터 베이스 전압이 0이 아닌 경우에만 활성 모드에 있다는 것이다.따라서 미러 설계를 위한 가장 단순한 바이어스 조건은 인가 전압 V를A 기본 전압 V와B 동일하게 설정한다.이A V의 최소 유용 값은 전류 소스의 준수 전압이라고 불린다.그러한 바이어스 조건에서는 얼리 효과(Early effect)가 설계에서 아무런 역할도 하지 않는다.[9]

이러한 고려사항은 다음과 같은 설계 절차를 제안한다.

- 원하는 출력O 전류 I = I를C2 선택하십시오.

- 출력 전류보다 클 것으로 가정되는 기준 전류 I를R1 선택한다. 아마도 상당히 클 것이다.

- Q1, IC1: 입력 수집기 전류 결정

- Shockley 다이오드 법칙을 사용하여 기본BE1 전압 V 결정

- 여기서 나는S 때때로 척도 전류라고 불리는 장치 매개변수다.

- 또한 기본 전압의 값은 준수 전압A V = V를BE1 설정한다. 이 전압은 거울이 제대로 작동하는 가장 낮은 전압이다.

- R1 결정:

- Eq. 1을 사용하여 방출체 다리 저항 R을2 결정한다(클러터를 줄이기 위해 스케일 전류가 동일하게 선택됨).

지정된 저항 값을 사용하여 전류 찾기

설계 문제의 역방향은 저항기 값이 알려졌을 때 전류를 찾는 것이다.그 다음에 반복적인 방법이 설명된다.출력 트랜지스터 Q의2 수집기-기준 전압이 0이 되도록 전류 소스가 편향되었다고 가정하십시오.R을1 통과하는 전류는 다음과 같이 주어진 입력 또는 기준 전류다.

재배열 시 다음과C1 같이 확인됨:

Eq. 2

다이오드 방정식은 다음을 제공한다.

Eq. 3

Eq.1은 다음을 제공한다.

이 세 가지 관계는 반복에 의해 해결될 수 있는 조류에 대한 비선형적이고 암묵적인 결정이다.

- 우리는 나와C1 나 사이의C2 시작 값을 추측한다.

- V에BE1 대한 가치를 찾음:

- IC1:의 새로운 가치를 찾아 보십시오.

- IC2:의 새로운 가치를 찾아 보십시오.

이 절차는 수렴에 반복되며, 스프레드시트에서 편리하게 설정된다.단순히 매크로를 사용하여 초기 값을 가진 스프레드시트 셀에 새 값을 복사하여 솔루션을 빠른 순서로 얻는다.

표시된 회로와 같이 V가CC 변경되면 출력 전류가 변경된다는 점에 유의하십시오.따라서 V의CC 변동에도 불구하고 출력 전류를 일정하게 유지하기 위해서는 회로가 저항기1 R을 사용하기보다는 일정한 전류원에 의해 구동되어야 한다.

정확한 용액

위의 초월 방정식은 램버트 W 함수의 관점에서 정확하게 풀 수 있다.

출력 임피던스

전류 소스의 중요한 속성은 작은 신호 증분 출력 임피던스로 이상적으로는 무한해야 한다.위들러 회로는 트랜지스터 }}: 전류가 증가하면 R에2 걸친 전압 강하가2 증가하여 Q에2 대한 V가BE 감소하여 전류의 증가에 대응한다이2 피드백은 R과 관련된 피드백이 주어진 전류를 구동하기 위해 더 큰 전압을 사용하도록 강제하기 때문에 회로의 출력 임피던스가 증가함을 의미한다.

출력 저항은 그림 2와 같이 회로에 대한 작은 신호 모델을 사용하여 발견된다.트랜지스터 Q는1 다이오드가 연결되어 있기 때문에 소형 신호 방출기 저항 r로E 대체된다.[10]트랜지스터 Q는2 하이브리드 파이 모델로 대체된다.출력에 시험 전류 I이x 부착되어 있다.

이 수치를 이용하여, 출력 저항은 키르흐호프의 법칙을 이용하여 결정된다.왼쪽 지면에서 R의2 접지 연결부까지 Kirchhoff의 전압 법칙 사용:

재배열:

R의2 접지 연결부에서 시험 전류의 접지까지 Kirchhoff의 전압 법칙 사용:

또는b I:를 대신하여

Eq. 4

Eq. 4에 따르면 출력 트랜지스터의 r에π 비해 R이2 충분히 큰 한 출력 트랜지스터 자체의 출력 저항(rO)보다 Widlar 전류 소스의 출력 저항이 증가한다(대형 저항2 R은 곱하는O 인자가 값(β + 1)에 근접하게 한다).출력 트랜지스터는 낮은 전류를 전달하여 r이π 커지게 하고, R의2 증가는 이 전류를 더욱 감소시키는 경향이 있어 r의π 상관적인 증가를 유발한다.따라서 R2 ≫ r의π 목표는 비현실적일 수 있으며, 아래에 추가 논의가 제공된다.저항 R1∥r은E 방출체 저항 r이E 보통 몇 옴에 불과하기 때문에 보통 작다.

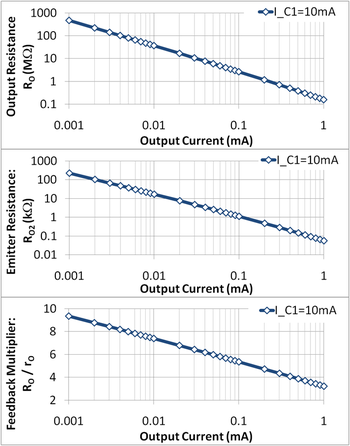

출력 저항의 전류 의존성

저항성π r과O r의 현재 의존성은 기사 하이브리드-pi 모델에서 논의된다.저항기 값의 현재 의존도는 다음과 같다.

그리고

VCB = 0V일 때 조기 효과로 인한 출력 저항(장치 매개 변수 V는A 조기 전압)

이 글의 앞부분부터(편리를 위해 척도 전류를 동일하게 설정):Eq. 5

따라서, 소 r의E 일반적인 경우에, 그리고 r과O 관련된 선도적 용어가 훨씬 더 클 것으로 예상하면서 R의O 두 번째 임기를 무시하는 경우: Eq. 6

어디 마지막 형태 R2에 방정식 5를 대체하는 것에 의해 발견된다.방정식 6를 출력 저항의 가치보다 훨씬 IC1 을 디자인만을 위한 출력 트랜지스터 결과 rO보다 더 큰<>IC2.그림 3은 회로 출력 저항 수신 전용 피드백으로 출력 트랜지스터의 저항 rO의 현재 의존에 의해 그렇게 결정하지 못한다를 보여 준다.(그림 3의 출력 저항은 4개의 크기 순서가 다른 반면, 피드백 계수는 1개의 크기 순서에 의해서만 변화한다.)

피드백 계수를 증가시키기 위해 I을C1 증가시키면 준수 전압도 증가하게 되는데, 이는 전류 소스가 더 제한적인 전압 범위에서 작동한다는 것을 의미하기 때문에 좋은 것은 아니다.따라서 예를 들어, 규정 준수 전압 설정 목표C1, I에 대한 상한값 설정, 출력 저항 충족 목표의 경우 출력 전류 I의C2 최대값이 제한된다.

그림 3의 중앙 패널은 이미터 다리 저항과 출력 전류 사이의 설계 절충을 보여준다: 낮은 출력 전류는 더 큰 다리 저항을 필요로 하고, 따라서 더 큰 설계 영역을 필요로 한다.따라서 면적의 상한은 출력 전류에서 하한을 설정하고 회로 출력 저항에서 상한을 설정한다.

R에O 대한 Eq. 6은 Eq. 5에 따른 R의2 값 선택에 따라 달라진다.즉, Eq. 6은 회로 동작식이 아니라 설계 값 방정식이다.Eq. 5를 사용하여 특정 설계 목적에 대해 R을2 선택한 후 R 값은 고정된다.회로 작동으로 인해 전류, 전압 또는 온도가 설계된 값에서 벗어날 경우, 그러한 편차로 인한 R의O 변화를 예측하려면 Eq. 6이 아니라 Eq. 4를 사용해야 한다.

참고 항목

참조

- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Analysis and design of analog integrated circuits (4th ed.). John Wiley and Sons. pp. §4.4.1.1 pp. 299–303. ISBN 0-471-32168-0.

{{cite book}}: CS1 maint : 복수이름 : 작성자 목록(링크) - ^ AS Sedra & KC Smith (2004). Microelectronic circuits (5th ed.). Oxford University Press. Example 6.14, pp. 654–655. ISBN 0-19-514251-9.

- ^ MH Rashid (1999). Microelectronic circuits: analysis and design. PWS Publishing Co. pp. 661–665. ISBN 0-534-95174-0.

- ^ AS Sedra & KC Smith (2004). §9.4.2, p. 899 (5th ed.). ISBN 0-19-514251-9.

- ^ 예를 들어 IC 전압 조절기의 그림 2를 참조하십시오.

- ^ RJ 위들러:미국 특허 번호 03320439; 1965년 5월 26일 신청; 1967년 5월 16일 허가: 통합 회로에 대한 저부가 전류 소스

- ^ 자세한 내용은 Widlar: 선형 집적 회로에 대한 일부 회로 설계 기법 및 단일 작동 증폭기에 대한 설계 기법을 참조하십시오.

- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Figure 2.38, p. 115. ISBN 0-471-32168-0.

{{cite book}}: CS1 maint : 복수이름 : 작성자 목록(링크) - ^ 물론 거울의 출력 저항이 주요 고려사항인 설계를 상상할 수도 있다.그렇다면 다른 접근이 필요하다.

- ^ 다이오드에 연결된 트랜지스터에서 수집기는 베이스와 단락되어 있기 때문에 트랜지스터 수집기-베이스 접합부는 그 전체에 시간 변동 전압이 없다.그 결과 트랜지스터는 베이스-방사선 다이오드처럼 동작하는데, 저주파수에서는 단순히 저항기E r = VT/I인E 작은 신호 회로가 있고E, I는 DC Q 포인트 방출기 전류가 있다.다이오드 소신호 회로를 참조하십시오.

추가 읽기

- Linden T. Harrison (2005). Current Sources and Voltage References: A Design Reference for Electronics Engineers. Elsevier-Newnes. ISBN 0-7506-7752-X.

- Sundaram Natarajan (2005). Microelectronics: Analysis and Design. Tata McGraw-Hill. p. 319. ISBN 0-07-059096-6.

- 현재 미러 및 활성 부하: 무후오청

![{\displaystyle {\begin{aligned}(\beta _{2}+1)I_{B2}&=\left(1+{\frac {1}{\beta _{2}}}\right)I_{C2}={\frac {1}{R_{2}}}\left(V_{BE1}-V_{BE2}\right)\\&={\frac {V_{\text{T}}}{R_{2}}}\left[\ln \left(I_{C1}/I_{S1}\right)-\ln \left(I_{C2}/I_{S2}\right)\right]={\frac {V_{\text{T}}}{R_{2}}}\ln \left({\frac {I_{C1}I_{S2}}{I_{C2}I_{S1}}}\right)\ ,\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2fe36a235ecb9c1bd0e3eedd49a6363f645cfeca)

![I_{b}\left[(R_{1}\parallel r_{E})+r_{\pi }\right]+[I_{x}+I_{b}]R_{2}=0\ .](https://wikimedia.org/api/rest_v1/media/math/render/svg/3862be56e5a63578fd1bf57900a13aedaa94788c)

![R_{O}={\frac {V_{x}}{I_{x}}}=r_{O}\left[1+{\frac {\beta R_{2}}{(R_{1}\parallel r_{E})+r_{\pi }+R_{2}}}\right]](https://wikimedia.org/api/rest_v1/media/math/render/svg/d8b1cfc4fd11db5b1b3d090da8cfbd0e592e0095)

![+\ R_{2}\left[{\frac {(R_{1}\parallel r_{E})+r_{\pi }}{(R_{1}\parallel r_{E})+r_{\pi }+R_{2}}}\right]\ .](https://wikimedia.org/api/rest_v1/media/math/render/svg/033a7d64c94712c0e8c1e3cf1bfcd747be5318e7)