내장 웨이퍼 레벨 볼 그리드 어레이

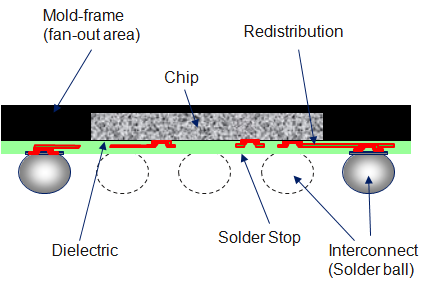

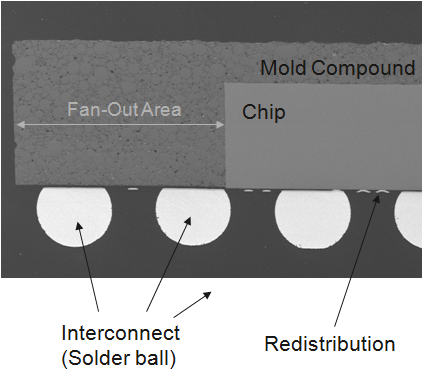

Embedded wafer level ball grid array임베디드 웨이퍼 레벨 볼 그리드 어레이(eWLB)는 집적회로의 패키징 기술입니다.패키지 인터커넥트는 실리콘 칩과 주조 화합물로 만들어진 인공 웨이퍼에 적용됩니다.

eWLB는 기존의 웨이퍼 레벨 볼 그리드 어레이 기술(WLB 또는 WLP: 웨이퍼 레벨 패키지)을 더욱 발전시킨 것입니다.eWLB 테크놀로지의 배후에 있는 주된 원동력은 팬아웃과 인터커넥트 루팅을 위한 더 많은 공간을 가능하게 하는 것이었습니다.

패키지 생성을 위한 모든 프로세스 단계는 웨이퍼에서 수행됩니다.이것에 의해, 종래의 패키징 테크놀로지(예를 들면, 볼 그리드 어레이)에 비해, 전기 및 열성능이 뛰어난 매우 작고 평평한 패키지를 저비용으로 생성할 수 있습니다.실리콘 웨이퍼에 내장된 모든 WLB 기술에서 상호 연결(일반적으로 납땜 볼)이 칩에 들어가는 것이 일반적입니다(팬인 설계라고 합니다).따라서 패키징할 수 있는 것은 인터커넥트 수가 제한된 칩뿐입니다.

eWLB 테크놀로지에 의해, 많은 수의 상호 접속을 가지는 칩을 실현할 수 있습니다.이 패키지는 기존의 웨이퍼 레벨 패키지와 마찬가지로 실리콘 웨이퍼에 작성되지 않고 인공 웨이퍼에 작성됩니다.따라서 프런트 엔드 가공 웨이퍼를 다이싱하여 싱글 칩을 캐리어에 장착합니다.칩 간 거리는 자유롭게 선택할 수 있지만 일반적으로 실리콘 웨이퍼보다 더 큽니다.칩 주변의 틈새와 가장자리는 이제 웨이퍼를 형성하기 위한 주조 화합물로 채워집니다.경화 후 금형 주위에 금형틀을 포함한 인공 웨이퍼를 생성하여 추가 상호접속 요소를 반송한다.인공 웨이퍼 구축(이른바 재구성) 후 칩 패드에서 인터커넥트로의 전기적 접속은 다른 전통적인 웨이퍼 레벨 패키지와 마찬가지로 박막 기술로 이루어집니다.

이 테크놀로지를 사용하면 임의의 거리(팬아웃 설계)에서 패키지로 임의의 수의 추가 인터커넥트를 실현할 수 있습니다.따라서 이 웨이퍼 레벨 패키징 기술은 칩 면적이 필요한 개수의 인터커넥트를 적절한 거리에 배치하기에 충분하지 않은 공간에 민감한 애플리케이션에도 사용할 수 있습니다.eWLB 기술은 Infineon, STMicroelectronics 및 STATS ChipPAC [1]Ltd에 의해 개발되었습니다.최초의 컴포넌트는 2009년 중반(휴대전화)에 출시되었습니다.

프로세스 단계

이점

- 저비용(패키지 및 테스트)

- 최소 가로형 패키지 크기 및 높이

- 뛰어난 전기적 및 열적 특성

- 패키지에서 실현 가능한 상호 연결 수는 제한되지 않습니다.

- 다중 다이 패키지 및 스택형 패키지의 높은 통합 가능성

- 향후 패키지 표준

단점들

- 육안검사가 제한되어 점검 및 수리가 어려움

- 패키지와 보드 사이의 기계적 응력이 다른 패키지 기술보다 강하게 전달됨

「 」를 참조해 주세요.

레퍼런스

외부 링크

- https://web.archive.org/web/20120305094749/http://www.infineonventures.com/cms/en/corporate/press/news/releases/2007/INFCOM200711-013.html

- http://content.yudu.com/Library/A1mxrk/3DPackagingFebruaryi/resources/4.htm

- https://safe.nrao.edu/wiki/pub/Main/EuropeanMicrowaveWeek08/WFR14-1.pdf

- https://web.archive.org/web/20080517033548/http://www.ciol.com/Semicon/Tech-Watch/News-Reports/Infineon,-ASE-intro-eWLB-package-technology/131107101404/0/

- http://www.statschippac.com/services/packagingservices/waferlevelproducts/~/media/파일/패키지%20데이터시트/eWLB.ashx

- http://www.amkor.com/go/packaging/all-packages/cspnl/

- http://www.wsdmag.com/Articles/ArticleID/19576/19576.html

- http://www.semineedle.com/posting/26088?snc=20641&snc=20641

- http://ieeexplore.ieee.org/Xplore/login.jsp?url=http%3A%2F%2Fieeexplore.ieee.org%2Fiel5%2F4147209%2F4141004%2F04147210.pdf%3Farnumber%3D4147210&authDecision=-203

- https://web.archive.org/web/20110703111509/http://141.30.122.65/키노트/6-Plieninger-ESTC_Keynote_20060907.pdf

- https://web.archive.org/web/20090728202431/http://annualreport2008.infineon.com/de/template.asp?content=innovationen

- 윤승욱 외eWLB(Embedded Wafer Level BGA), 전자부품 및 기술회의, 2010