OR 게이트

OR gate| 입력 | 산출량 | |

| A | B | A 또는 B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

OR 게이트는 수학 로직에서 논리 분리())를 구현하는 디지털 로직 게이트로, 위의 진실 표에 따라 작동합니다.HIGH 출력(1)은 게이트에 대한 입력 중 하나 또는 둘 다 HIGH(1)인 경우에 발생합니다.어느 쪽의 입력도 높지 않으면 LOW 출력(0)이 됩니다.다른 의미에서 OR 함수는 보완적인 AND 함수가 [1]최소값을 찾듯이 두 이진수 사이의 최대값을 효과적으로 찾습니다.

기호

OR 게이트에는 American(ANSI 또는 'military') 기호와 IEC('유럽' 또는 '직사각형') 기호, 사용되지 않는 DIN [2][3]기호 등 두 가지 기호가 있습니다.자세한 내용은 로직 게이트 기호를 참조하십시오.

하드웨어 설명 및 핀 배치

OR 게이트는 기본적인 로직게이트로 TTL 및 CMOS IC 로직패밀리에서 사용할 수 있습니다.표준 4000 시리즈 CMOS IC는 4071로 4개의 독립된2 입력 OR 게이트를 갖추고 있습니다.TTL 디바이스는 7432 입니다.원래 7432 OR 게이트에는 많은 오프스팟이 있으며, 모두 핀 배치는 같지만 내부 아키텍처는 다르므로 서로 다른 전압 범위 및/또는 더 빠른 속도로 작동할 수 있습니다.표준 2입력 OR 게이트 외에 3입력 및 4입력 OR 게이트도 사용할 수 있습니다.CMOS 시리즈에서는, 다음과 같은 것이 있습니다.

- 4075: 트리플 3입력 OR 게이트

- 4072: 듀얼 4입력 OR 게이트

다음과 같은 종류가 있습니다.

- 74LS32: 쿼드2 입력 OR 게이트(저전력 Shottky 버전)

- 74HC32: 쿼드 2입력 OR 게이트(고속 CMOS 버전) - 소비전류/와이더 전압범위 감소

- 74AC32: 쿼드2 입력 OR 게이트(고도의 CMOS 버전) - 74와 유사HC32, 단, 대폭적인 스위칭 속도와 강력한 드라이브 탑재

- 74LVC32: 동일한 저전압 CMOS 버전.

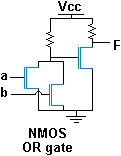

실장

해석적 표현

( , ) + - b {\, b)=는 OR 게이트의 해석 표현입니다.

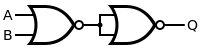

대체 수단

특정 OR 게이트를 사용할 수 없는 경우 아래 이미지에 표시된 구성의 NAND 또는 NOR 게이트에서 OR 게이트를 만들 수 있습니다.논리 게이트는 NAND 또는 NOR 게이트의 조합으로 만들 수 있습니다.

| 원하는 게이트 | NAND 구조 | NOR 구조 |

|---|---|---|

|  |  |

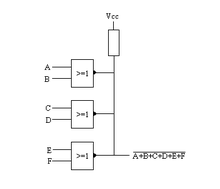

유선-OR

많은 회로에서 제어 신호에 사용되는 액티브 로우 오픈 컬렉터 로직 출력의 경우 여러 출력을 함께 배선하여 OR 함수를 생성할 수 있습니다.이 배치를 유선 OR이라고 합니다.이러한 OR 기능의 실장은 일반적으로 N 또는 P형 전용 트랜지스터 프로세스의 집적회로에서도 볼 수 있습니다.

「 」를 참조해 주세요.

레퍼런스

- ^ "OR Gate". Hyperphysics.phy-astr.gsu.edu. Retrieved 2012-09-24.

- ^ Harris, David Harris, Sarah (2007). Digital design and computer architecture (1st ed.). San Francisco,Calif.: Morgan Kaufmann. p. 21. ISBN 9780123704979.

- ^ Brumbach, Michael E. Industrial electricity (8th ed.). Clifton Park, N.Y.: Delmar. p. 546. ISBN 9781435483743.

OR 게이트의 해석 표현입니다.

OR 게이트의 해석 표현입니다.