POWER6

POWER6이 글의 외부 링크 사용은 위키백과의 정책이나 지침을 따르지 않을 수 있습니다.(2017년 9월)(본 방법 및 |

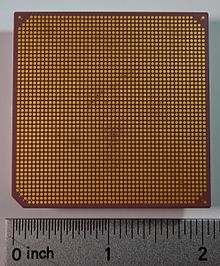

파워6 CPU | |

| 일반정보 | |

|---|---|

| 런칭 | 2007 |

| 설계자 : | IBM |

| 성능 | |

| 최대 CPU 클럭 속도 | 3.6GHz ~ 5.0GHz |

| 캐시 | |

| L1 캐시 | 64+64KB/코어 |

| L2 캐시 | 코어당 4MB |

| L3 캐시 | 32MB/칩(오프칩) |

| 건축과 분류 | |

| 기술노드 | 65nm |

| 명령어세트 | 파워 ISA (Power ISA v.2.05) |

| 물리적 규격 | |

| 코어스 |

|

| 역사 | |

| 이전 버전 | POWER5 |

| 후임자 | POWER7 |

| POWER, PowerPC 및 Power ISA 아키텍처 |

|---|

| NXP (이전 프리스케일 및 모토로라) |

| IBM |

|

| IBM/닌텐도 |

| 다른. |

| 관련 링크 |

| 회색으로 취소됨, 이탤릭체로 기록됨 |

POWER6는 Power ISA v.2.03을 구현한 IBM이 개발한 마이크로프로세서입니다.2007년 시스템에서 사용이 가능해졌을 때, POWER5+의 뒤를 이어 IBM의 대표적인 파워 마이크로프로세서가 되었습니다.이 프로젝트는 eCLipz 프로젝트의 일부라고 하며, IBM의 서버 하드웨어를 실제적(즉, iSeries, pSeries 및 zSeries의 약자인 "ipz")으로 통합하는 것을 목표로 한다고 합니다.[1]

역사

POWER6는 2006년 2월 국제 고체 회로 회의(ISSCC)에서 설명되었으며, 2006년[2] 10월 마이크로프로세서 포럼과 2007년 2월 다음 ISSCC에서 추가 세부 사항이 추가되었습니다.그것은 2007년 5월 21일에 공식적으로 발표되었습니다.[3]2007년 6월 8일 3.5, 4.2 및 4.7 GHz의 속도로 출시되었지만 [4]회사는 시제품이 6 GHz에 도달했다고 언급했습니다.[5] POWER6는 2005년 중반에 첫 번째 실리콘에 도달했으며 2008년 5월 P595가 출시되면서 5.0 GHz에 도달했습니다.[6][7]

묘사

POWER6는 듀얼 코어 프로세서입니다.각 코어는 양방향 동시 멀티스레딩(SMT)이 가능합니다.POWER6에는 약 7억 9천만 개의 트랜지스터가 있으며 65nm 공정에서 제작된 341mm의2 대형 트랜지스터가 있습니다.POWER5와 눈에 띄는 차이점은 POWER6가 순서가 맞지 않는 대신 순서대로 명령을 실행한다는 점입니다.이러한 변화에 따라 최적의 성능을 위해 소프트웨어를 다시 컴파일해야 하는 경우가 종종 있지만 POWER6 프로젝트의 수석 엔지니어에 따르면 POWER6는 수정되지 않은 소프트웨어를 사용하더라도 POWER5+에 비해 성능이 크게 향상되었다고 합니다.[4]

또한 POWER6는 ViVA-2, Virtual Vector Architecture를 활용하므로 여러 POWER6 노드를 결합하여 단일 벡터 프로세서 역할을 수행할 수 있습니다.[8]

각 코어는 두 개의 정수 단위, 두 개의 이진 부동 소수점 단위, AltiVec 단위 및 새로운 소수 부동 소수점 단위를 포함합니다.회사 논문에 따르면 이진 부동 소수점 장치는 "[a] 6주기, 13-FO4 파이프라인을 달성하기 위한 많은 마이크로아키텍처, 로직, 회로, 래치 및 통합 기술을 통합한다"고 합니다.[9]IBM의 경쟁사 서버와 달리 POWER6는 IEEE 754 십진법 산술을 하드웨어로 지원하며 실리콘에 통합된 첫 번째 십진법 부동 소수점 단위를 포함합니다.50개 이상의 새로운 부동 소수점 명령어가 십진법 수학과 이진법과 십진법 사이의 변환을 처리합니다.[10]이 기능은 시스템 z10에 탑재된 z10 마이크로프로세서에도 추가되었습니다.[8]

각 코어에는 64KB의 4방향 세트 연관 명령 캐시와 8방향 세트 연관 설계의 64KB 데이터 캐시가 있으며, 2단계 파이프라인으로 독립적인 32비트 읽기 또는 사이클당 1개의 64비트 쓰기를 지원합니다.[9]각 코어에는 준프라이빗 4개의 MiB 유니파이드 L2 캐시가 있으며, 캐시에는 특정 코어가 할당되지만 다른 코어에는 빠르게 액세스할 수 있습니다.두 코어는 80GB/[10]s 버스를 사용하여 32 MiB L3 캐시를 공유합니다.

POWER6는 2개의 노드 간 링크(50GB/s)를 사용하여 최대 31개의 다른 프로세서에 연결할 수 있으며 코어당 최대 10개의 논리적 파티션(시스템당 최대 254개)을 지원합니다.설정된 파라미터에 따라 성능과 전력을 모니터링하고 조정하는 서비스 프로세서 인터페이스가 있습니다.[11]

IBM은 또한 프로세서를 위해 5GHz 듀티 사이클 보정 클록 분배 네트워크를 사용합니다.네트워크에서 회사는 폭 3 ㎛, 두께 1.2 ㎛의 구리 배전선을 구현합니다.POWER6 설계는 이중 전원 공급 장치, 0.8~1.2V 범위의 논리 공급 장치 및 약 150mV 이상의 SRAM 전원 공급 장치를 사용합니다.[9]

POWER6의 열적 특성은 POWER5의 열적 특성과 유사합니다.IBM의 수석 과학자인 Frank Soltis 박사는 IBM이 POWER6 설계에서 90 nm와 65 nm 부분의 조합을 사용하여 고주파와 관련된 전력 누출 문제를 해결했다고 말했습니다.[12]

POWER6+

약간 향상된 POWER6+는 2009년 4월에 출시되었으나 2008년 10월부터 Power 560 및 570 시스템에 탑재되어 출시되었습니다.IBM의 메인프레임 프로세서에서 가져온 기능인 안전한 메모리 파티션을 위한 메모리 키를 추가했습니다.[13]

상품들

2008년[update] 현재 POWER6 시스템 범위에는 "Express" 모델(520, 550 및 560)과 Enterprise 모델(570 및 595)이 포함되어 있습니다.[14]다양한 시스템 모델은 모든 규모의 비즈니스에 적합하도록 설계되었습니다.예를 들어 520 Express는 중소기업용으로, Power 595는 대규모 다중 환경 데이터 센터용으로 판매됩니다.Express와 Enterprise 모델의 주요 차이점은 후자에 주문형 용량 업그레이드(CUoD) 기능과 핫 플러그형 프로세서 및 메모리 "북"이 포함되어 있다는 점입니다.

| 이름. | 소켓수 | 코어수 | CPU 클럭 주파수 |

|---|---|---|---|

| 520 익스프레스 | 2 | 4 | 4.2 GHz 또는 4.7 GHz |

| 550 익스프레스 | 4 | 8 | 4.2GHz 또는 5.0GHz |

| 560 익스프레스 | 8 | 16 | 3.6GHz |

| 570 | 8 | 16 | 4.4 GHz 또는 5.0 GHz |

| 570 | 16 | 32 | 4.2GHz |

| 575 | 16 | 32 | 4.7GHz |

| 595 | 32 | 64 | 4.2GHz 또는 5.0GHz |

IBM은 POWER6 기반 블레이드 서버 4대도 제공합니다.[15]사양은 아래 표와 같습니다.

| 이름. | 코어수 | CPU 클럭 주파수 | 블레이드 슬롯 필요 |

|---|---|---|---|

| 블레이드 센터 JS12 | 2 | 3.8GHz | 1 |

| 블레이드 센터 JS22 | 4 | 4.0GHz | 1 |

| 블레이드 센터 JS23 | 4 | 4.2GHz | 1 |

| 블레이드 센터 JS43 | 8 | 4.2GHz | 2 |

모든 블레이드는 AIX, IBM i 및 Linux를 지원합니다.BladeCenter S 및 H 섀시는 AIX, i 및 Linux를 실행하는 블레이드에서 지원됩니다.BladeCenter E, HT 및 T 섀시는 AIX 및 Linux를 실행하는 블레이드를 지원하지만 i는 지원하지 않습니다.

리노에서 열린 슈퍼컴퓨팅 2007(SC07) 컨퍼런스에서 수냉식 신형 Power 575가 공개되었습니다.575는 4.7GHz에 32개의 POWER6 코어와 최대 256GB의 RAM이 있는 2U "노드"로 구성되어 있습니다.한 프레임에 최대 448개의 코어를 설치할 수 있습니다.

| 이름. | 코어수 | CPU 클럭 주파수 | 컨트롤러 수 |

|---|---|---|---|

| DS8700 | 2, 4 | 4.7GHz | 1, 2 |

| DS8800 | 2, 4, 8 | 5.0GHz | 1, 2 |

참고 항목

- IBM 파워 마이크로프로세서

- POWER7

- POWER6와 많은 기술을 공유하는 메인프레임 프로세서인 z10.

참고문헌

- ^ "A Mainframe Roadmap". Isham Research. Archived from the original on 2016-03-03.

- ^ David Kanter (October 16, 2006). "Fall Processor Forum 2006: IBM's POWER6". Real World Technologies.

- ^ "IBM Unleashes World's Fastest Chip in Powerful New Computer" (Press release). IBM. Archived from the original on May 24, 2007.

- ^ a b "IBM POWER system hardware". IBM. Archived from the original on 2008-12-16. Retrieved 2008-10-09.

- ^ Vance, Ashlee (2006-02-07). "IBM thumbs nose at heat concerns, kicks Power6 to 6GHz". The Register. Retrieved 2006-02-07.

- ^ "IBM's Power6 Gets First Silicon as Power5+ Looms". IT Jungle. Archived from the original on 2005-11-25. Retrieved 2005-08-22.

- ^ "IBM smacks rivals with 5.0GHz Power6 beast". The Register. Retrieved 2008-10-12.

- ^ a b "An eCLipz Looms on the Horizon". Real World Technologies. Retrieved 2005-12-19.

- ^ a b c "IBM Tips Power6 Processor Architecture". InformationWeek. 6 February 2006. Retrieved 2022-07-13.

- ^ a b "Fall Processor Forum: Power6 at 5 GHz". Heinz Heise. Archived from the original on 2007-11-16. Retrieved 2006-10-12.

- ^ Merritt, Rick (2006-10-10). "IBM cranks dual-core Power6 beyond 4GHz". EE Times. Retrieved 2022-07-13.

- ^ Roger Howorth (2006-02-08). "IBM's Power6 processor to run at 4GHz in 2007". IT Week. Archived from the original on 2007-09-26. Retrieved 2007-07-11.

- ^ "IBM Power Systems Announcement Overview" (PDF). IBM. 28 April 2009. Archived from the original (PDF) on 13 May 2011. Retrieved 6 March 2018.

- ^ "IBM Power Systems Hardware". IBM. Archived from the original on May 12, 2008.

- ^ "IBM Power Systems Hardware - Blade Servers". IBM. Archived from the original on May 21, 2008.

외부 링크

- IBM POWER6 프레스 키트

- "IBM's Power6 gets help with math, multimedia". CNET. October 10, 2006.

- "IBM Debuts Power6 In New Unix Server". InformationWeek. May 21, 2007.

- "POWER6 set to carry the POWER4/POWER5/970 lineage forward?". Ars Technica. October 19, 2006.

- "IBM unveils POWER6 microprocessor details". Ars Technica. February 12, 2007.

- "IBM's POWER6 flies the coop at 4.7GHz". Ars Technica. May 21, 2007.

권장읽기

- POWER Roadmap, IBM, 2006년 10월

- M. J. Mack; W. M. Sauer; S. B. Swaney; B. G. Mealey (November 2007). "IBM POWER6 Reliability". IBM Journal of Research and Development. 51 (6): 763–774. doi:10.1147/rd.516.0763.

- R. Berridge; R. M. Averill; A. E. Barish; M. A. Bowen; P. J. Camporese; J. DiLullo; P. E. Dudley; J. Keinert; D. W. Lewis; R. D. Morel; T. Rosser; N. S. Schwartz; P. Shephard; H. H. Smith; D. Thomas; P. J. Restle; J. R. Ripley; S. L. Runyon; P. M. Williams (November 2007). "IBM POWER6 microprocessor physical design and design methodology". IBM Journal of Research and Development. 51 (6): 685–714. doi:10.1147/rd.516.0685.

- H. -Y. McCreary; M. A. Broyles; M. S. Floyd; A. J. Geissler; S. P. Hartman; F. L. Rawson; T. J. Rosedahl; J. C. Rubio; M. S. Ware (November 2007). "EnergyScale for IBM POWER6 microprocessor based systems". IBM Journal of Research and Development. 51 (6): 775–786. doi:10.1147/rd.516.0775.

- M. S. Floyd; S. Ghiasi; T. W. Keller; K. Rajamani; F. L. Rawson; J. C. Rubio; M. S. Ware (November 2007). "System power management support in the IBM POWER6 microprocessor". IBM Journal of Research and Development. 51 (6): 733–746. CiteSeerX 10.1.1.128.8084. doi:10.1147/rd.516.0733.

- H. Q. Le; W. J. Starke; J. S. Fields; F. P. O'Connell; D. Q. Nguyen; B. J. Ronchetti; W. M. Sauer; E. M. Schwarz; M. T. Vaden (November 2007). "IBM POWER6 microarchitecture". IBM Journal of Research and Development. 51 (6): 639–662. CiteSeerX 10.1.1.115.6020. doi:10.1147/rd.516.0639.

- D. W. Plass; Y. H. Chan (November 2007). "IBM POWER6 SRAM arrays". IBM Journal of Research and Development. 51 (6): 747–756. doi:10.1147/rd.516.0747.

- L. Eisen; J. W. Ward; H. -W. Tast; N. Mading; J. Leenstra; S. M. Mueller; C. Jacobi; J. Preiss; E. M. Schwarz; S. R. Carlough (November 2007). "IBM POWER6 accelerators: VMX and DFU". IBM Journal of Research and Development. 51 (6): 1–21. CiteSeerX 10.1.1.128.3776. doi:10.1147/rd.516.0663.

- "파워: 6세대"(2006년 10월 30일).마이크로프로세서 보고서.