방사선 경화

Radiation hardening전자 부품과 회로 손상 또는 오작동 전리 방사선(입자 복사와 고에너지 전자기 방사선)[1]우주( 낮은 지구 주위를 도특히 밖)에서 원자로 및 입자 acc 주변 환경 특히 높은 수준에 의해 야기되는 지게 만드는 방사선 강화는 가는 과정이다.ele격노기, 핵 사고 또는 핵 전쟁 중.

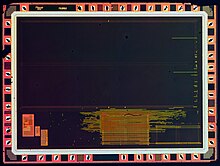

대부분의 반도체 전자 부품은 방사선 손상에 취약하며 방사선 경화(rad-hard) 부품은 방사선 손상에 대한 민감성을 감소시키는 설계 및 제조 변형과 함께 비경화 등가물에 기초한다.마이크로일렉트로닉스 칩의 내방사선성 설계를 작성하기 위해 광범위한 개발과 테스트가 필요하기 때문에 방사선 경화 칩의 기술은 최근 개발에 비해 뒤처지는 경향이 있습니다.

방사선 강화 제품은 일반적으로 총 이온화 선량(TID), 강화된 저 선량률 효과(ELDRS), 중성자와 양성자 치환 손상 및 단일 사건 효과(SEE)를 포함한 하나 이상의 결과 영향 시험에 대해 시험된다.

방사선에 의한 문제

높은 수준의 이온화 방사선이 있는 환경에서는 특별한 설계상의 문제가 발생한다.하나의 하전 입자가 수천 개의 전자를 방출하여 전자 노이즈와 신호 스파이크를 일으킬 수 있습니다.디지털 회선의 경우, 부정확하거나 이해할 수 없는 결과가 발생할 수 있습니다.이것은 인공위성, 우주선, 미래의 [2][3][4]양자 컴퓨터, 군용 항공기, 원자력 발전소, 그리고 핵무기의 설계에서 특히 심각한 문제이다.이러한 시스템의 적절한 작동을 보장하기 위해 군사 또는 항공우주 시장을 위한 집적회로 및 센서 제조업체는 다양한 방사선 경화 방법을 사용한다.결과 시스템은 rad(iation)-hardened, rad-hard 또는 (컨텍스트 내에서) hardened라고 한다.

주요 방사선 손상원

전리방사선에 대한 전자장치의 대표적인 피폭원은 인공위성을 위한 Van Allen 방사선 벨트, 센서와 제어회로를 위한 발전소의 원자로, 제어전자, 특히 입자 검출기 장치를 위한 입자 가속기, 칩 패키징 재료의 동위원소로부터의 잔류 방사선, 우주 방사선이다.우주선과 고고도 항공기, 그리고 잠재적으로 모든 군사 및 민간 전자제품에 대한 핵폭발.

- 우주선은 모든 방향에서 발생하며 X선 및 감마선과 함께 약 85%의 양성자, 14%의 알파 입자, 1%의 중이온으로 구성됩니다.대부분의 영향은 에너지가 0.1~20GeV인 입자에 의해 발생합니다.대기는 이 중 대부분을 여과하기 때문에 주로 우주선이나 고고도 항공기의 관심사이지만 [5][6]지표면의 일반 컴퓨터에도 영향을 미칠 수 있다.

- 태양 입자 이벤트는 태양 방향에서 발생하며, 고에너지(몇 개의 GeV) 양성자와 중이온의 큰 플럭스로 구성되어 있으며, 다시 X선 방사선을 동반한다.

- Van Allen 방사선 벨트는 지자기장에 갇힌 전자(최대 10 MeV)와 양성자(최대 100s MeV)를 포함합니다.지구에서 멀리 떨어진 지역의 입자속은 태양의 실제 상태와 자기권에 따라 크게 달라질 수 있습니다.그들의 위치 때문에 그들은 위성에 대한 우려를 제기한다.

- 2차 입자는 다른 종류의 방사선과 전자기기의 주변 구조의 상호작용에서 발생한다.

- 원자로는 원자력 발전소의 센서와 제어 회로에 영향을 미칠 수 있는 감마선과 중성자 방사선을 생성한다.

- 입자 가속기는 높은 에너지 양성자와 전자를 생성하며, 이들의 상호작용에 의해 생성된 2차 입자는 대형 강입자 [7]충돌기와 같은 시스템의 경우 연간 10 MRad[Si]의 크기로 민감한 제어 및 입자 검출기 구성요소에 상당한 방사선 손상을 일으킨다.

- 핵폭발은 광범위한 전자파 복사, 전자기 펄스(EMP), 중성자 복사 및 1차 및 2차 하전 입자의 플럭스를 통해 짧고 매우 강한 서지를 생성한다.핵전쟁의 경우, 그것들은 모든 민간 및 군사 전자제품에 잠재적인 우려를 제기한다.

- 칩 패키징 재료는 1970년대 새로운 D램 칩에서 소프트 에러를 일으킨 것으로 밝혀진 음흉한 방사선원이었다.칩의 패키징에 포함된 방사성 원소의 흔적은 알파 입자를 생성했으며, 이 입자는 때때로 DRAM 데이터 비트를 저장하는 데 사용되는 캐패시터 중 일부를 방출했습니다.오늘날에는 순도 높은 패키징 재료를 사용하고 오류 수정 코드를 사용하여 DRAM 오류를 검출하고 수정함으로써 이러한 영향을 줄이고 있습니다.

전자제품에 대한 방사선 영향

이 섹션은 확인을 위해 추가 인용문이 필요합니다. 2021년 12월 (이를 에 대해 합니다) |

기본 메커니즘

다음 두 가지 기본적인 손상 메커니즘이 발생합니다.

격자 변위

격자 변위는 중성자, 양성자, 알파 입자, 중이온 및 매우 높은 에너지 감마 광자에 의해 발생합니다.그들은 결정 격자에서 원자의 배치를 변화시켜 지속적인 손상을 만들고, 재조합 중심 수를 증가시켜, 마이너리티 캐리어를 고갈시키고 영향을 받은 반도체 접합부의 아날로그 특성을 악화시킨다.반직관적으로 단시간에 높은 선량은 손상된 격자의 부분 어닐링("치유")을 유발하여 장기간에 걸쳐 낮은 강도로 전달된 동일한 선량에 비해 낮은 수준의 손상을 초래한다(LDR 또는 낮은 선량률).이러한 유형의 문제는 기본 영역의 소수 캐리어에 의존하는 양극성 트랜지스터에서 특히 중요합니다. 재결합으로 인한 손실이 증가하면 트랜지스터 이득의 손실이 발생합니다(중성자 효과 참조).ELDRS(향상된 저선량 속도 민감) 무상으로 인증된 구성 요소는 0.01rad(Si)/s = 36rad(Si)/h 미만의 플럭스에서는 손상이 나타나지 않습니다.

이온화 효과

이온화 효과는 에너지가 너무 낮아 격자 효과를 일으키지 못하는 하전 입자에 의해 발생합니다.이온화 효과는 보통 일시적인 것으로 글리치와 소프트 에러를 발생시키지만, 다른 손상 메커니즘(예: 래치업)을 트리거하면 디바이스 파괴로 이어질 수 있습니다.자외선과 X선 복사에 의한 광전류도 이 범주에 속할 수 있습니다.MOSFET 트랜지스터의 산화층 구멍의 점진적 축적은 선량이 충분히 높을 때 장치 고장까지 성능 악화로 이어집니다(총 이온화 선량 효과 참조).

영향은 방사선의 종류, 총 선량과 방사선의 흐름, 방사선의 조합, 심지어 디바이스 부하(동작 주파수, 동작 전압, 미립자에 부딪힌 순간 트랜지스터의 실제 상태)의 종류에 따라 크게 달라질 수 있습니다.이러한 파라미터는 철저한 테스트를 어렵게 합니다.많은 테스트 샘플이 필요합니다.

결과 효과

"최종 사용자" 효과는 여러 그룹으로 특징지을 수 있습니다.

반도체 격자와 상호작용하는 중성자는 원자를 치환할 것이다.이는 재조합 센터 수 증가와 심각한 결함으로 이어져 마이너리티 캐리어의 수명이 단축되고 CMOS보다 양극성 장치에 더 많은 영향을 미칩니다.실리콘의 양극성 소자는 10~1011 중성자/cm² 수준에서10 전기적 파라미터의 변화를 보이는 경향이 있으며 CMOS 소자는 10 중성자/cm²까지 영향을15 받지 않습니다.장치의 민감도는 통합 수준의 증가와 개별 구조물의 크기 감소와 함께 증가할 수 있다.또한 고에너지 천체물리학 기구의 주요 소음원인 중성자 활성화에 의한 유도 방사능의 위험도 있다.유도 방사선은 사용된 재료의 불순물로부터 나오는 잔류 방사선과 함께 기기의 수명 동안 모든 종류의 단일 이벤트 문제를 일으킬 수 있다.광커플러에서 흔히 볼 수 있는 GaAs LED는 중성자에 매우 민감하다.격자 손상은 결정 발진기의 주파수에 영향을 미칩니다.하전 입자의 운동 에너지 효과(격자 변위)도 여기에 속합니다.

총 이온화 선량 효과

전리방사선으로 인한 반도체 격자의 누적손상(격자변위손상)이 값은 rad 단위로 측정되며 장치 성능이 서서히 저하됩니다.실리콘 기반 장치에 전달되는 총 선량이 5000rad를 초과하면 몇 초에서 몇 분 사이에 장기적인 열화가 발생합니다.CMOS 장치에서 방사선은 게이트 절연층에 전자-홀 쌍을 만들어 재결합 중에 광전류를 발생시키고, 절연체의 격자 결함에 갇힌 구멍은 지속적인 게이트 바이어싱을 만들어 트랜지스터의 임계값 전압에 영향을 미치므로 N형 MOSFET 트랜지스터는 더 쉽고 P형 O형 트랜지스터는 더 쉽다.켜는 게 더 어려워누적된 전하가 트랜지스터를 영구적으로 개방(또는 폐쇄) 상태로 유지할 수 있을 정도로 높을 수 있으며, 이로 인해 장치 고장이 발생할 수 있습니다.일부 자가 치유는 시간이 지남에 따라 이루어지지만, 이 효과는 그다지 크지 않습니다.이 효과는, 고속 전자 기기의 핫 캐리어 열화와 같습니다.결정 발진기는 주파수를 변경하는 방사선량에 다소 민감하다.스윕 석영을 사용하면 감도를 크게 줄일 수 있습니다.천연 석영 결정은 특히 민감합니다.모든 결과 영향 시험 절차에 대해 TID 시험을 위한 방사선 성능 곡선을 생성할 수 있다.이러한 곡선은 TID 테스트 프로세스 전체의 성능 경향을 나타내며 방사선 테스트 보고서에 포함된다.

과도 선량 효과

일반적으로 핵폭발 중에 발생하는 단시간 고강도 방사선의 펄스.높은 방사 플럭스는 반도체 본체 전체에 광전류를 만들어 트랜지스터를 랜덤하게 열게 하고 플립 플랍과 메모리 셀의 논리 상태를 변화시킵니다.펄스 지속 시간이 너무 길거나 펄스로 인해 접합부 손상 또는 래치업이 발생할 경우 영구 손상이 발생할 수 있습니다.래치업은 일반적으로 핵폭발의 X선과 감마선 섬광에 의해 발생한다.수정발진기는 석영으로 유도되는 광전도성에 의해 플래시 지속시간 동안 발진을 멈출 수 있습니다.

시스템 생성 EMP 효과

SGEMP는 방사선 섬광이 기기를 통과하여 칩, 회로 기판, 전기 케이블 및 케이스의 재료에 국소 이온화 및 전류를 발생시킴으로써 발생합니다.

디지털 손상: 참조

단일 사건 효과(SEE)는 1970년대부터 [8]광범위하게 연구되어 왔다.고에너지 입자가 반도체를 통과할 때 이온화된 흔적을 남긴다.이 이온화는 과도 선량 1과 유사한 국소적 효과를 일으킬 수 있습니다. 즉, 출력의 양성 결함, 메모리 또는 레지스터의 양성 비트 플립 또는 특히 고전력 트랜지스터의 경우 파괴적 래치업 및 번아웃입니다.단일 이벤트 효과는 위성, 항공기 및 기타 민간 및 군사 항공우주 애플리케이션에서 전자 장치에 중요하다.래치가 포함되지 않은 회로에서는 SEE의 지속시간을 넘어 회로의 반응시간을 늦추는 RC시상수회로를 도입하는 것이 도움이 되는 경우가 있습니다.

단일 이벤트 과도

SET는 이온화 이벤트로부터 수집된 전하가 회로를 통과하는 스플리어스 신호의 형태로 방전될 때 발생합니다.이것은 사실상 정전기 방전의 영향입니다.소프트 에러, 되돌릴 수 있습니다.

단일 이벤트 역전

전자제품에서 단일 이벤트 업셋(SEU) 또는 일시적인 방사선 효과는 칩과 상호작용하는 단일 이온에 의해 발생하는 메모리 또는 레지스터 비트의 상태 변화입니다.이로 인해 디바이스에 지속적인 손상이 발생하는 것은 아니지만 이러한 오류로부터 복구할 수 없는 시스템에 지속적인 문제가 발생할 수 있습니다.소프트 에러, 되돌릴 수 있습니다.매우 민감한 디바이스에서는 단일 이온으로 인해 인접한 여러 메모리 셀에서 Multiple-Bit Upter(MBU; 다중 비트 업라이트)가 발생할 수 있습니다.SEU는 스테이트 머신 등의 제어회선을 업라이트 하거나 디바이스를 정의되지 않은 상태, 테스트모드 또는 정지상태로 만들 때 Single-Event Functional Interrupt(SEFI; 싱글이벤트 기능 인터럽트)가 될 수 있습니다.이 경우 리셋 또는 전원 재투입이 필요합니다.

싱글 이벤트 래치업

SEL은 기생 PNPN 구조의 모든 칩에서 발생할 수 있습니다.두 개의 내부 트랜지스터 접합부 중 하나를 통과하는 중이온 또는 고에너지 양성자는 사이리스터와 같은 구조를 켤 수 있으며, 사이리스터는 장치의 전원을 껐다 켤 때까지 "단축"(래치업으로 알려진 효과) 상태로 유지됩니다.이 효과는 전원과 기판 사이에 발생할 수 있으므로 파괴적으로 높은 전류가 관여되어 부품이 고장날 수 있다.하드 에러, 되돌릴 수 없습니다.벌크 CMOS 디바이스가 가장 취약합니다.

싱글 이벤트 스냅백

단일 이벤트 스냅백은 SEL과 비슷하지만 PNPN 구조가 필요하지 않으며, 이온이 드레인 접점 부근에 부딪혀 전하 캐리어의 눈사태 증대를 일으킬 때 큰 전류를 전환하는 N 채널 MOS 트랜지스터에서 유도될 수 있습니다.그러면 트랜지스터가 열리고 열린 상태로 유지되며, 이는 되돌릴 수 없는 하드 오류입니다.

단일 이벤트로 인한 번아웃

소스 영역 바로 아래의 기판이 전방 바이어스 되어 드레인 소스 전압이 기생 구조의 파괴 전압보다 높을 때 전력 MOSFET에서 SEB가 발생할 수 있다.그 결과 고전류 및 국소 과열로 인해 디바이스가 파손될 수 있습니다.하드 에러, 되돌릴 수 없습니다.

단일 이벤트 게이트 파열

게이트에 고전압이 인가되는 동안 게이트 영역에 중이온이 닿으면 전력 MOSFET에서 SEGR이 관찰되었습니다.그런 다음 이산화실리콘의 절연층에서 국부적 고장이 발생하여 게이트 영역의 국부적 과열과 파괴(미세적 폭발처럼 보입니다)를 일으킵니다.쓰기 또는 지우기 중에 EEPROM 셀에 비교적 높은 전압이 가해지는 경우에도 발생할 수 있습니다.하드 에러, 되돌릴 수 없습니다.

'테스트' 참조

양성자 빔은 가용성으로 인해 SEE 시험에 널리 사용되는 반면, 낮은 에너지에서 양성자 조사는 SEE 민감도를 과소평가할 수 있다.또한 양성자 빔은 양성자 테스트 결과를 흐리게 하거나 성숙 전 장치 고장을 초래할 수 있는 총 이온화 선량(TID) 실패 위험에 장치를 노출시킨다.가장 대표적인 SEE 시험 방법인 백색 중성자 빔은 일반적으로 고체 표적 기반 선원에서 도출되며, 결과적으로 플럭스 불균일성과 작은 빔 영역이 발생한다.또한 백색 중성자 빔은 에너지 스펙트럼의 불확실성을 측정하며, 종종 높은 열 중성자 함량을 가진다.

양성자와 파쇄 중성자 선원의 단점은 SEE 시험에 단일 에너지 14 MeV 중성자를 사용함으로써 피할 수 있다.잠재적 우려 사항은 단일 에너지 중성자 유도 단일 사건 효과가 넓은 스펙트럼 대기 중성자의 실제 영향을 정확하게 나타내지 못할 것이라는 것이다.그러나 최근 연구에 따르면 반대로 단일 에너지 중성자(특히 14 MeV 중성자)는 현대 마이크로 일렉트로닉스의 [9]SEE 단면을 매우 정확하게 이해하는 데 사용될 수 있다.

방사선 경화 기술

물리적.

경화 칩은 흔히 일반적인 반도체 웨이퍼 대신 절연 기판에서 제조됩니다.실리콘 온 인슐레이터(SOI)와 실리콘 온 사파이어(SOS)가 일반적으로 사용됩니다.일반 상용 등급 칩은 50~100 그레이(5~10 krad)를 견딜 수 있지만, 우주 등급 SOI 및 SOS 칩은 1000~3000 그레이(100~300 krad)[10][11]의 용량에도 견딜 수 있습니다.한때 방사선 강화 버전(RadHard)[12]으로 많은 4000 시리즈 칩을 사용할 수 있었습니다.SOI는 래치업이벤트를 배제하지만 TID 및 SEE 경도는 [13]개선되지 않습니다.

바이폴라 집적회로는 일반적으로 CMOS 회로보다 방사선 허용도가 높습니다.저전력 숏키(LS) 5400 시리즈는 1000 krad에 견딜 수 있으며, 많은 ECL 디바이스는 10,000 [12]krad에 견딜 수 있습니다.

자기저항 RAM(MRAM)은 방사선 경화, 개서 가능한 비휘발성 도체 메모리를 제공할 수 있는 유력한 후보로 간주됩니다.물리적 원리 및 초기 테스트에 따르면 MRAM은 이온화에 의한 데이터 [14]손실에 취약하지 않습니다.

캐패시터 베이스의 DRAM은, 많은 경우, 보다 견고하고(단, 보다 크고, 보다 고가의) SRAM으로 대체됩니다.

탄화규소 또는 [citation needed]질화갈륨과 같은 깊은 수준의 결함에 대해 높은 내성을 제공하는 넓은 밴드 갭을 가진 기판 선택.

방사능으로부터 패키지를 보호하여 베어 [15]디바이스의 노출을 줄입니다.

칩을 보호하는 붕소인규산염 유리 패시베이션 층에서 고갈된 붕소(동위원소 붕소-11로만 구성됨)를 사용하여 칩 자체를 (중성자로부터) 차폐하는 것은 자연적으로 널리 퍼져 있는 붕소-10이 중성자를 쉽게 포착하고 알파 붕괴를 겪기 때문이다(소프트 오차 참조).

방사선 [16]저항성을 높이기 위해 평소보다 더 큰 프로세스 노드를 사용합니다.새로운 방사선 경화 공정의 높은 개발 비용 때문에 2016년 현재 최소 "진짜" rad-hard(RHBP, Rad-Hard By Process) 공정은 150 nm이지만, "진짜" rad-hard 프로세스(RHBD, Rad-hard by Design)[17]에 사용된 기법 중 일부를 사용한 rad-hard 65 nm FPGA를 사용할 수 있었다.2019년 현재 110 nm rad-hard 프로세스를 사용할 [18]수 있습니다.

셀당 트랜지스터가 통상보다 많은 SRAM 셀(4T 또는 6T)을 사용하여 [19][17]셀당 소비 전력과 사이즈가 높아져 셀이 SEU에 대한 내구성이 향상됩니다.

엣지리스 CMOS 트랜지스터의 사용으로 독특한 물리구조와 함께 독특한 물리배치.[20]

논리

Error Correcting Code Memory(ECC 메모리)는 다중 비트를 사용하여 파손된 데이터를 확인하고 수정할 수 있습니다.방사선의 영향은 시스템이 RAM에 액세스하지 않을 때에도 메모리 내용을 손상시키므로 "스크러버" 회로는 RAM을 지속적으로 스위프해야 합니다.데이터를 읽고 용장 비트에 데이터 오류가 없는지 확인한 후 RAM에 수정을 다시 써야 합니다.

다중 요소는 시스템 수준에서 사용할 수 있습니다.3개의 마이크로프로세서 보드가 독립적으로 계산의 답을 계산하여 그 답을 비교할 수 있습니다.소수 결과를 내는 어떤 시스템도 다시 계산될 것이다.로직은 같은 시스템에서 에러가 반복되면 보드가 셧다운되도록 추가할 수 있습니다.

회로 [21]레벨에서는 용장 소자를 사용할 수 있습니다.단일 비트를 3비트로 대체하고 각 비트에 대해 별도의 "투표 로직"으로 교체하여 지속적으로 결과를 결정할 수 있습니다(트리플 모듈러 용장성).따라서 칩 설계 면적이 5배 증가하므로 소형 설계용으로 예약해야 합니다.그러나 실시간으로 "장애 안전"할 수 있다는 두 번째 장점이 있습니다.(방사선과 무관할 수 있음) 단일 비트 장애가 발생한 경우, 투표 로직은 감시 타이머에 의존하지 않고 올바른 결과를 계속 생성합니다.3개의 개별 프로세서 시스템 간의 시스템 레벨 투표에서는 일반적으로 3개의 프로세서 시스템 간의 투표를 수행하기 위해 회로 레벨 투표 로직을 사용해야 합니다.

경화 래치를 사용할 [22]수 있습니다.

워치독 타이머는 온보드 프로세서의 쓰기 조작 등 일반적으로 시스템이 가동 중임을 나타내는 시퀀스가 실행되지 않는 한 시스템의 하드리셋을 실행합니다.통상의 동작중에, 소프트웨어는 워치독타이머에의 기입을 정기적으로 스케줄 해, 타이머가 다 써지지 않게 합니다.방사선에 의해 프로세서가 올바르게 동작하지 않는 경우는, 소프트웨어가 올바르게 동작해 워치독타이머를 클리어 할 수 없을 가능성이 있습니다.워치독은 최종적으로 타임아웃 되어 하드리셋을 강제로 시스템에 적용합니다.이는 방사선 경화의 다른 방법에 대한 최후의 수단으로 간주된다.

군사 및 우주 산업 응용 프로그램

방사선 강화 및 방사선 내성 컴포넌트는 POL(Point-of-Load) 애플리케이션, 위성 시스템 전원, 스텝다운 스위칭 레귤레이터,[23] 마이크로프로세서, FPGA, FPGA 전원, 고효율 저전압 서브시스템 전원 등 군사 및 항공우주 애플리케이션에서 자주 사용됩니다.

그러나 모든 군사용 부품이 방사선 경화 상태인 것은 아니다.예를 들어 US MIL-STD-883은 많은 방사선 관련 시험을 특징으로 하지만 단일 이벤트 래치업 빈도에 대한 규격은 없다.포보스-그룬트 우주 탐사선은 비슷한 [13]가정 때문에 실패했을 수도 있다.

우주 응용 분야에 사용되는 방사선 경화 전자 장치의 시장 규모는 2021년에 23억 5천만 달러로 추정되었다.새로운 연구는 이것이 2032년까지 [24]약 47억 6천만 달러에 달할 것으로 추정했다.

통신용 핵경도

전기통신에서 핵경도라는 용어는 다음과 같은 의미를 갖는다. 1) 주어진 핵환경에서 시스템, 설비 또는 장치의 성능이 저하될 것으로 예상되는 정도를 나타내는 표현 2) 핵물질을 포함하는 환경에서 생존할 수 있는 시스템 또는 전자부품의 물리적 속성디온과 전자기 펄스(EMP)가 있습니다.

메모들

- 핵 경도는 민감도 또는 취약성의 관점에서 표현될 수 있다.

- 예상되는 성능 저하 범위(예: 정지 시간, 데이터 손실 및 장비 손상)를 정의하거나 지정해야 합니다.환경(예: 방사선 수준, 과압, 피크 속도, 흡수 에너지 및 전기적 스트레스)을 정의하거나 지정해야 한다.

- 핵무기에 의해 생성된 특정 환경에서 정의된 수준의 생존성을 허용하는 시스템 또는 구성요소의 물리적 속성.

- 핵 경도는 특정 또는 실제 정량화된 환경 조건과 물리적 파라미터(피크 방사선 수준, 과압, 속도, 흡수 에너지 및 전기적 스트레스 등)에 대해 결정된다.설계 시방서를 통해 달성되며, 시험 및 분석 기법을 통해 검증됩니다.

rad-hard 컴퓨터의 예

- System/4 Pi는 IBM이 제작하고 우주왕복선(AP-101 변형)에 탑재되어 사용되며 System/360 아키텍처를 기반으로 합니다.

- 1976년에 도입된 RCA1802 8비트 CPU는 방사선 경화 마이크로프로세서 최초로 시리얼로 생산되었습니다.

- PIC 1886VE, 180nm 벌크실리콘 기술로 Milandr에 의해 설계되고 Sitronics-Mikron에 의해 제조된 러시아의 50MHz 마이크로 컨트롤러.

- m68k 베이스:

- General Dynamics에서 사용하는 Coldfire M5208은 저전력(1.5W) 방사선 경화 대안입니다.

- MIL-STD-1750A 기반:

- GEC-Plesey가 제조한 RH1750.

- 2003년에 도입된 스페이스 마이크로사의 프로톤 100k SBC는 단일 프로세서에서 단일 이벤트 업라이트(SEU)를 경감하는 TTMR이라고 하는 갱신된 투표 방식을 사용합니다.CPU는 적도 BSP-15.

- 2004년에 도입된 Space Micro Inc.의 Proton200k SBC는 특허받은 Time Triple Modular Redundancy(TTMR; 타임 트리플 모듈러 용장성) 테크놀로지 및 H-Core 테크놀로지에 의한 Single Event Function Interrupt(SEFI; 싱글 이벤트 기능 인터럽트) 테크놀로지를 통해 SEU를 경감합니다.프로세서는 고속 Texas Instruments 320C6Xx 시리즈 디지털 신호 프로세서입니다.프로톤200k는 4000MIPS로 동작하며 SEU를 경감합니다.

- MIPS 기반:

- RH32는 Honeywell Aerospace가 생산한다.

- NASA가 사용하는 Mongoose-V는 우주선 탑재 컴퓨터 애플리케이션(즉, New Horizons)용 32비트 마이크로프로세서입니다.

- KOMDIV-32는 러시아 쿠르차토프 연구소에서 제조한 NIISI에서 개발한 MIPS R3000과 호환되는 32비트 마이크로프로세서입니다.

- SPARC 기반:

- ERC32와 LEON 2, 3, 4, 5는 Gaisler Research와 European Space Agency가 설계한 방사선 경화 프로세서이다.이것들은 각각 GNU Lesser General Public License와 GNU General Public License에서 이용 가능한 합성 가능한 VHDL로 설명되어 있습니다.

- Cobham Semiconductor Solutions(구 Aeroflex Microelectronics Solutions)가 제작한 6세대 싱글보드 컴퓨터(SBC)는 LEON 마이크로프로세서를 [25]지원합니다.

- PowerPC 기반:

- BAE Systems가 생산하는 RAD6000 싱글보드 컴퓨터(SBC)에는 rad-hard POWER1 CPU가 탑재되어 있습니다.

- RHPPC는 Honeywell Aerospace가 생산합니다.강화된 전력에 근거하고 있다PC 603e.

- SP0 및 SP0-S는 Aitech Defense Systems에서 생산되며 SOI PowerQ를 사용하는 3U cPCI SBC입니다.UICC-II MPC8548E, 전원PC e500 베이스로 833MHz~1.18GHz의 처리속도에 대응 [1]

- Space Micro Inc.의 Proton400k SBC, 전력 기반 프리스케일 P2020 CPUPC e500.

- Broad Reach Engineering의 BRE440.IBM PPC440 코어 기반 system-on-a-chip, 266 MIPS, PCI, 2x 이더넷, 2x UARTS, DMA 컨트롤러, L1/L2 캐시 광대역 엔지니어링 웹 사이트

- RAD750 SBC는 BAE 시스템즈에서 생산되며 전력에 기반합니다.PC 750 프로세서는 RAD6000의 후속 프로세서입니다.

- Maxwell Technologies가 만든 SCS750은 3개의 파워에 투표합니다.PC 750코어를 서로 연결하여 방사선 영향을 줄입니다.그 중 7개는 가이아 우주선에 의해 사용된다.

- 보잉사는 위성 개발 센터를 통해 동력 기반 방사선 경화 우주 컴퓨터 변형을 생산합니다.PC 750.

- RAD5500 프로세서는 RAD750의 후속 기종으로,PC e5500.

- ARM 기반:

- RISC-V 기반:

「 」를 참조해 주세요.

레퍼런스

- ^ Messenger, George C. "Radiation hardening". AccessScience. doi:10.1036/1097-8542.566850.

- ^ "Quantum computers may be destroyed by high-energy particles from space". New Scientist. Retrieved 7 September 2020.

- ^ "Cosmic rays may soon stymie quantum computing". phys.org. Retrieved 7 September 2020.

- ^ Vepsäläinen, Antti P.; Karamlou, Amir H.; Orrell, John L.; Dogra, Akshunna S.; Loer, Ben; Vasconcelos, Francisca; Kim, David K.; Melville, Alexander J.; Niedzielski, Bethany M.; Yoder, Jonilyn L.; Gustavsson, Simon; Formaggio, Joseph A.; VanDevender, Brent A.; Oliver, William D. (August 2020). "Impact of ionizing radiation on superconducting qubit coherence". Nature. 584 (7822): 551–556. arXiv:2001.09190. Bibcode:2020Natur.584..551V. doi:10.1038/s41586-020-2619-8. ISSN 1476-4687. PMID 32848227. S2CID 210920566. Retrieved 7 September 2020.

- ^ Ziegler, J. F.; Lanford, W. A. (16 November 1979). "Effect of Cosmic Rays on Computer Memories". Science. 206 (4420): 776–788. Bibcode:1979Sci...206..776Z. doi:10.1126/science.206.4420.776. PMID 17820742. S2CID 2000982.

- ^ Ziegler, J. F.; Lanford, W. A. (June 1981). "The effect of sea level cosmic rays on electronic devices". Journal of Applied Physics. 52 (6): 4305–4312. Bibcode:1981JAP....52.4305Z. doi:10.1063/1.329243.

- ^ Brugger, M. (May 2012). Radiation Damage to Electronics at the LHC. 3rd International Particle Accelerator Conference. New Orleans, Louisiana. pp. THPPP006.

- ^ G.C. Messenger, Milton Ash, 싱글 이벤트 현상, Springer Science & Business Media, 2013, ISBN 1461560438, 12-xiii 페이지

- ^ Normand, Eugene; Dominik, Laura (20–23 July 2010). "Cross Comparison Guide for Results of Neutron SEE Testing of Microelectronics Applicable to Avionics". 2010 IEEE Radiation Effects Data Workshop. 2010 IEEE Radiation Effects Data Workshop. p. 8. doi:10.1109/REDW.2010.5619496. ISBN 978-1-4244-8405-8.

- ^ Microsemi Corporation (March 2012), RTSX-SU Radiation-Tolerant FPGAs (UMC) (PDF) (Datasheet), retrieved May 30, 2021

- ^ Atmel Corporation (2008), Rad Hard 16 MegaBit 3.3V SRAM MultiChip Module AT68166H (PDF) (Datasheet), retrieved May 30, 2021

- ^ a b Leppälä, Kari; Verkasalo, Raimo (17–23 September 1989). Protection of Instrument Control Computers against Soft and Hard Errors and Cosmic Ray Effects. International Seminar on Space Scientific Engineering. CiteSeerX 10.1.1.48.1291.

- ^ a b Shunkov, >V. "Common misconceptions about space-grade integrated circuits". habr.com.

- ^ Wang, B.; Wang, Z.; Hu, C.; Zhao, Y.; Zhang, Y.; Zhao, W. (2018). "Radiation Hardening Techniques for SOT-MRAM Peripheral Circuitry". 2018 IEEE International Magnetics Conference (INTERMAG). 2018 IEEE International Magnetics Conference (INTERMAG). pp. 1–2. doi:10.1109/INTMAG.2018.8508368. ISBN 978-1-5386-6425-4.

- ^ "StackPath".

- ^ "The other Atmel: Radiation Hardened Sparc CPU's the CPU Shack Museum". 27 July 2009.

- ^ a b "Avnet: Quality Electronic Components & Services" (PDF).

- ^ "Aerospace & Defense Solutions" (PDF). Onsemi.

- ^ Tiehu Li Yintang Yang, Junan Zhang, and Jia Liu. "A novel SEU hardened SRAM bit-cell design". IEICE Electronics Express. 14 (12): 1–8.

{{cite journal}}: CS1 maint: 작성자 파라미터 사용(링크) - ^ 베니그니, M., 리버럴리, V., Stabile, A. 및 C. (2010).rad-hard SRAM 셀 설계: 비교 연구.2010년 제27회 마이크로일렉트로닉스 소송 국제회의.도이: 10.1109/miel.2010.5490481

- ^ Platteter, Dale G. (October 1980). Protection of LSI Microprocessors using Triple Modular Redundancy. International IEEE Symposium on Fault Tolerant Computing.

- ^ Krishnamohan, Srivathsan; Mahapatra, Nihar R. (2005). "Analysis and design of soft-error hardened latches". Proceedings of the 15th ACM Great Lakes symposium on VLSI - GLSVSLI '05. Proceedings of the 15th ACM Great Lakes symposium on VLSI. p. 328. doi:10.1145/1057661.1057740. ISBN 1595930574.

- ^ Mil & Aero Staff (2016-06-03). "FPGA development devices for radiation-hardened space applications introduced by Microsemi". Military & Aerospace Electronics. Retrieved 2018-11-02.

- ^ Diagle, Lisa (2022-06-17). "Rad-hard electronics for space to reach $4.76 billion by 2032, study says". Military Embedded Systems. Retrieved 2022-06-18.

- ^ "Single Board Computer (SBC) Family". Cobham. Archived from the original on 2019-04-08. Retrieved 2018-11-02.

- ^ "VA10820 - Radiation Hardened ARM Cortex-M0 MCU". Vorago Technologies. Archived from the original on 2019-02-14. Retrieved 2018-11-02.

- ^ "High Performance Spacecraft Computing (HPSC)Project Overview" (PDF). 5 November 2018.

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ ESA Dahlia

- ^ "NOEL-V Processor". Cobham Gaisler. Retrieved 14 January 2020.

서적 및 보고서

- Calligaro, Christiano; Gatti, Umberto (2018). Rad-hard Semiconductor Memories. River Publishers Series in Electronic Materials and Devices. River Publishers. ISBN 978-8770220200.

- Holmes-Siedle, Andrew; Adams, Len (2002). Handbook of Radiation Effects (Second ed.). Oxford University Press. ISBN 0-19-850733-X.

- León-Florian, E.; Schönbacher, H.; Tavlet, M. (1993). Data compilation of dosimetry methods and radiation sources for material testing (Report). CERN Technical Inspection and Safety Commission. CERN-TIS-CFM-IR-93-03.

- Ma, Tso-Ping; Dressendorfer, Paul V. (1989). Ionizing Radiation Effects in MOS Devices and Circuits. New York: John Wiley & Sons. ISBN 0-471-84893-X.

- Messenger, George C.; Ash, Milton S. (1992). The Effects of Radiation on Electronic Systems (Second ed.). New York: Van Nostrand Reinhold. ISBN 0-442-23952-1.

- Oldham, Timothy R. (2000). Ionizing Radiation Effects in MOS Oxides. International Series on Advances in Solid State Electronics and Technology. World Scientific. doi:10.1142/3655. ISBN 978-981-02-3326-6.

- Platteter, Dale G. (2006). Archive of Radiation Effects Short Course Notebooks (1980–2006). IEEE. ISBN 1-4244-0304-9.

- Schrimpf, Ronald D.; Fleetwood, Daniel M. (July 2004). Radiation Effects and Soft Errors in Integrated Circuits and Electronic Devices. Selected Topics in Electronics and Systems. Vol. 34. World Scientific. doi:10.1142/5607. ISBN 978-981-238-940-4.

- Schroder, Dieter K. (1990). Semiconductor Material and Device Characterization. New York: John Wiley & Sons. ISBN 0-471-51104-8.

- Schulman, James Herbert; Compton, Walter Dale (1962). Color Centers in Solids. International Series of Monographs on Solid State Physics. Vol. 2. Pergamon Press.

- Holmes-Siedle, Andrew; van Lint, Victor A. J. (2000). "Radiation Effects in Electronic Materials and Devices". In Meyers, Robert A. (ed.). Encyclopedia of Physical Science and Technology. Vol. 13 (Third ed.). New York: Academic Press. ISBN 0-12-227423-7.

- van Lint, Victor A. J.; Flanagan, Terry M.; Leadon, Roland Eugene; Naber, James Allen; Rogers, Vern C. (1980). Mechanisms of Radiation Effects in Electronic Materials. NASA Sti/Recon Technical Report A. Vol. 1. New York: John Wiley & Sons. p. 13073. Bibcode:1980STIA...8113073V. ISBN 0-471-04106-8.

- Watkins, George D. (1986). "The Lattice Vacancy in Silicon". In Pantelides, Sokrates T. (ed.). Deep Centers in Semiconductors: A State-of-the-Art Approach (Second ed.). New York: Gordon and Breach. ISBN 2-88124-109-3.

- Watts, Stephen J. (1997). "Overview of radiation damage in silicon detectors — Models and defect engineering". Nuclear Instruments and Methods in Physics Research Section A. 386 (1): 149–155. Bibcode:1997NIMPA.386..149W. doi:10.1016/S0168-9002(96)01110-2.

- Ziegler, James F.; Biersack, Jochen P.; Littmark, Uffe (1985). The Stopping and Range of Ions in Solids. Vol. 1. New York: Pergamon Press. ISBN 0-08-021603-X.

외부 링크

- 연방표준 1037C(링크)

- (I) COTS를 사용한 통합 접근법 공간용 Rad-Terrance(SBC) 작성– Chad Thibodeau, Maxwell Technologies, COTS Journal, 2003년 12월

- Sandia Labs, 공간 및 방위 요구에 대응한 방사선 경화 Pentium (...) 개발– Sandia 프레스 릴리즈, 1998년 12월 8일

(마이크로 일렉트로닉스의 방사선 경화를 위한 Sandia의 제조 프로세스에 대한 일반적인 "배경화" 섹션도 포함) - 석영 결정에 대한 방사선 영향

- 밴더빌트 대학교 우주 방위 전자 연구소