울트라램

UltraRAM| 컴퓨터 메모리 및 데이터 스토리지 유형 |

|---|

| 휘발성 |

| 비휘발성 |

이 기사는 대부분의 독자들이 이해하기에는 너무 전문적일 수 있다.세부사항을 할 수 바랍니다. ( 4월 ( 템플릿메시지 및 ) |

울트라램은 개발 중인 새로운 저장장치다.랭커스터대 물리공학과가 워릭 물리학과와 공동으로 첨단 전자재료 저널에 울트라램 양산 가능성을 시사하는 논문을[1] 발표했다.S램프는 "RAM)의 기본성과 같은 데이터 스토리지 메모리에 있는 반면, DRAM)의 기본계획과 같은 데이터 저장 기술을 결합한 메모리 스토리지 기술로서 묘사되었다.e랭커스터 대학의 연구진은,[3] 품질 향상, 제조 공정의 미세 조정, UltraRAM 디바이스의 [4]실장 및 확장을 위한 추가 작업이 진행되고 있다고 말하고 있습니다.

메모리 개념

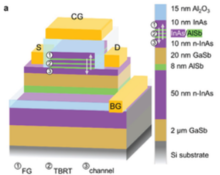

ULTRARAM은 FG(정면 게이트)에 전자가 있는지 여부에 따라 논리 상태가 결정되는 전하 기반 메모리입니다.FG는 Al2O3 유전체에 의해 컨트롤 게이트(CG)로부터, InAs/AlSb TBRT 헤테로 구조에 의해 기본 채널로부터 전기적으로 격리됩니다.FG(논리 0 상태를 정의)에 전자가 존재하면 기초가 되는n타입 InAs 채널의 캐리어가 고갈되어 컨덕턴스가 저하됩니다.따라서 소스(S) 접점과 드레인(D) 접점 사이에 전압이 인가되었을 때 채널을 통해 전류를 측정함으로써 FG의 충전 상태, 즉 메모리의 논리 상태를 비파괴적으로 판독할 수 있다.메모리의 마지막 컴포넌트는 InAs 백게이트(BG)로 게이트 스택 전체에 전압을 수직으로 인가하여 다양한 작업을 수행할 수 있습니다.

메모리를 뒷받침하는 참신함은 TBRT(Triple Barrier Resonant Tunneling) 구조이며, 단층 장벽과 달리 ±2.5V만 적용하면 전기 저항이 높은 상태에서 전도성이 높은 상태로 전환할 수 있습니다.이것은 AlSb 장벽과 InAs QW(Quantum Well) 층의 두께를 신중하게 설계함으로써 달성됩니다.메모리가 유지 상태에 있는 경우, 즉 디바이스에 전압이 인가되지 않은 경우, TBRT QW의 전자 접지 상태는 서로 어긋나며 에너지적으로 InAs FG 및 채널층의 300K 전자 모집단을 훨씬 웃돈다.실제로 비휘발성은 공진 터널 구조에 대해 비정상적으로 높은 에너지로 존재하는 QW 접지 상태에 의해 강화된다.이는 초박형 QW와 InAs의 매우 낮은 전자 유효 질량의 조합 때문입니다.이 상태에서 TBRT는 FG로 또는 FG 밖으로 전자가 전달되는 것을 방지하는 큰 장벽을 제공합니다.그러나 장치 전체에 적절한 바이어스를 적용하면 TBRT QW 접지 상태가 채널(프로그램 작동 중) 또는 FG(소거 작동 중)에서 점유된 전자 상태와 정렬되도록 전도 대역을 기울입니다.이를 통해 공명 터널링의 본질적으로 빠른 양자역학 과정을 통해 전자가 의도된 방향으로 TBRT 영역을 빠르게 이동할 수 있습니다.DRAM에 비해 필요한 저전압과 장치의 단위면적당 캐패시턴스가 낮기 때문에 DRAM과 플래시보다 각각 2~3배 낮은 20nm의 특징사이즈 ULTARAM 메모리에 대해 10~17J의 초저논리 상태 스위칭 에너지가 예측된다.단, 이 초저 스위칭 에너지를 nm 스케일디바이스 제작으로 실현하기 위해서는 먼저 µm 스케일디바이스의 기본 특성을 이해하고 최적화해야 합니다.GaAs 기판에서 성장한 ULTRAAM 프로토타입 디바이스는 이전에 105초의 비휘발성 유지와 106번의 프로그램 삭제 [1]사이클의 내구성을 보여 왔습니다.

운용

충전된 FG는 논리 '0'으로, 충전되지 않은 FG는 논리 '1'로 정의된다.프로그램 및 소거 사이클에서 각각 FG를 충전 및 방전하려면 CG에 ±2.55V의 전압 펄스를 사용합니다.

이전에 서브마이크로미터 피쳐 크기와 100mV/dec 미만의 서브임계 스윙을 갖는 InAs 채널 트랜지스터가 [5]시연되었습니다.그 결과 Lancaster 팀이 설계한 디바이스의 임계 전압 창은 350mV이므로 통상 오프 채널을 구현하면 ULTRAAM의 0/1 전류 대비가 30년까지 향상될 것으로 예상됩니다.채널의 신중한 수정을 통해 0/1 콘트라스트를 개선함으로써 메모리 어레이를 새로운 [1]고밀도 RAM 아키텍처로 구축할 수 있습니다.

중요성

실리콘 장치의 ULTARAM은 GaAs 화합물 반도체 웨이퍼의 이전 기술을 능가하는 성능을 발휘하여 최소 1000년 이상의 데이터 저장 시간, 빠른 스위칭 속도(디바이스 크기 기준) 및 최소 1000만~1000배 이상의 프로그램 삭제 사이클 내구성을 보여줍니다.r은 플래시보다 크다.연구를 이끄는 랭커스터 물리학과 Manus Hayne 교수는 "실리콘에 대한 ULTRARAM™은 큰 결정격자 불일치, 소자에서 화합물 반도체로의 변화,[2] 열수축의 차이 등 매우 중요한 재료 문제를 극복한 우리 연구의 큰 발전"이라고 말했다.

레퍼런스

- ^ a b c Hodgson, Peter D.; Lane, Dominic; Carrington, Peter J.; Delli, Evangelia; Beanland, Richard; Hayne, Manus (2022-01-05). "ULTRARAM: A Low‐Energy, High‐Endurance, Compound‐Semiconductor Memory on Silicon". Advanced Electronic Materials. 8 (4): 2101103. doi:10.1002/aelm.202101103. ISSN 2199-160X. S2CID 248070399.

- ^ a b "Mass production of revolutionary computer memory moves closer with ULTRARAM™ on silicon wafers for the first time". ScienceDaily. Retrieved 2022-04-08.

- ^ "'UltraRAM' breakthrough could merge storage and RAM into one component". PCWorld. Retrieved 2022-04-08.

- ^ Mark Tyson (2022-01-10). "UltraRAM Breakthrough Brings New Memory and Storage Tech to Silicon". Tom's Hardware. Retrieved 2022-04-08.

- ^ Chang, S. W.; Li, Xu; Oxland, R.; Wang, S. W.; Wang, C. H.; Contreras-Guerrero, R.; Bhuwalka, K. K.; Doornbos, G.; Vasen, T.; Holland, M. C.; Vellianitis, G. (30 January 2014). "InAs N-MOSFETs with record performance of Ion = 600 μA/μm at Ioff = 100 nA/μm (Vd = 0.5 V)". 2013 IEEE International Electron Devices Meeting: 16.1.1–16.1.4. doi:10.1109/IEDM.2013.6724639. S2CID 10847457.

외부 링크

- Nasser, Hussein (19 Jan 2022). "Is ULTRARAM a game changer?". YouTube.