카본나노튜브 전계효과 트랜지스터

Carbon nanotube field-effect transistor카본나노튜브 전계효과 트랜지스터(CNTPET)는 기존의 MOSFET 구조에서 벌크 실리콘 대신 단일 카본나노튜브 또는 카본나노튜브 어레이를 채널 재료로 사용하는 전계효과 트랜지스터입니다.1998년에 처음 증명된 CNTFET는 그 [1][2]이후 큰 발전을 거듭하고 있습니다.

개요 및 배경

무어의 법칙에 따르면 집적회로의 개별 디바이스 치수는 2년마다 약 2배씩 감소했습니다.이러한 장치의 축소는 20세기 후반부터 기술 진보의 원동력이 되어 왔습니다.그러나 ITRS 2009년 판에서 지적했듯이 임계 치수가 22nm [3]미만으로 축소됨에 따라 제조 기술과 디바이스 퍼포먼스에 관련된 추가 스케일 다운은 심각한 한계에 직면하게 되었습니다.한계에는 짧은 채널과 얇은 절연막을 통한 전자 터널링, 관련 누출 전류, 수동적 전력 손실, 짧은 채널 효과 및 장치 구조 및 [4]도핑의 변화가 포함됩니다.이러한 한계는 기존의 벌크 MOSFET 구조에서 단일 카본 나노튜브 또는 카본 나노튜브 어레이를 사용하여 채널 재료를 수정함으로써 어느 정도 극복하고 디바이스 치수를 더욱 축소할 수 있습니다.

탄소나노튜브의 전자구조

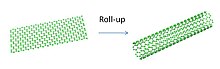

카본나노튜브는 Bravais 격자 벡터 δh 중 하나를 따라 감겨 중공 원통을 [5]형성한다고 생각되면 카본나노튜브의 뛰어난 전기적 특성은 그래핀의 독특한 전자구조로부터 계승된 것으로 볼 수 있다. [6] [7] 이 구조에서는 주기적인 경계조건이 δ상에h 부여되어 [8]원통표면에 심리스하게 결합된 탄소원자의 격자가 된다.

따라서 이러한 탄소나노튜브의 둘레는 2차원 그래핀 시트의 결정학적으로 등가한 2개의 부위를 연결하는 롤업 벡터 δh=n1 δ+m2 δ로 나타낼 수 있다.서 nn과 m은 정수이고, 그리고12 '은 육각형 격자의 원시 격자 벡터입니다.따라서 탄소나노튜브의 구조는 롤업 [6]벡터를 정의하는 한 쌍의 정수style(n, m)\n, m)\display(n, m를 가진 지수로 설명할 수 있다.정수 ,) { n , )、 nanotube t\ _ { } iral iral iraliraliraliral {\ {\ = d t ( d / ) 2+ + n { \ _ { t } { 0 / } { 0 / rta } { 0} d } { 0 } d } { d } } } { d } { d } } : by by by " - [ [ / ( +n) ]{ \= \ ^ { - 1 }[ { \ { , n / ( +n )}。 { 0 은 C 결합 거리입니다.

키랄 각도와 직경의 차이는 다양한 카본 나노튜브의 특성 차이를 일으킨다.예를 들어는(n, m){\displaystyle(n,m)}탄소 나노 튜블 때 nxm{\displaystyle n=m},[5] 있는 작은 밴드 갭 반도체 금속은 n− m=3나 그냥 나는 0{\displaystyle i\neq 0},[6][7]≠고란 적당한 온도의 밴드 갭 반도체{\displaystyle n-m=3i} 때 n− m≠ 3나는{\disp 표시할 수 있다.laystyle3i 서 는 정수입니다. i는 정수입니다.

이러한 결과는 1D 탄소 나노튜브의 주기적인 경계 조건이 그 둘레 주위에 소수의 파동 벡터만 존재할 수 있다는 점에 주목함으로써 동기 부여될 수 있다.금속 전도는 이러한 파동 벡터 중 하나가 원자가와 전도 대역이 퇴화된 그래핀의 2D 육각형 브릴루인 영역의 K 지점을 통과할 때 발생할 것으로 예상할 수 있습니다.

그러나 이 분석은 [5]금속성인 안락의자 튜브( \ n)를 제외하고 모든 를 - 3i \ \ n= 3 i \band 갭 [6]반도체로 변환하는 그래핀 시트를 롤업하여 발생하는 곡률의 영향을 무시한다.n- i ( \ n - m =i ), 0 ( \ i \ 0 )의 탄소나노튜브의 밴드갭은 비교적 작으나 나노튜브 직경이 약 [9]나노미터 정도일 경우 상온을 쉽게 초과할 수 있다. [10]

n- 3 ( \ n - m \ )의 반도체 카본 나노튜브의 g ( \ _ { } )는 주로 직경에 따라 달라집니다.실제로 이들 의 전자구조에 대한 단일결합 밀착기술에 따르면 )0{0t})이며[11], 여기서 V0 V_0})은 가장 가까운 호핑행렬이다.이 결과는 (0 / d 0}/t})}이(가) 전전자 제1원칙의 국소밀도 함수[12] 계산과 [13]실험 모두에서 확인된 것보다 훨씬 적은한 우수한 근사치이다.

곡률 효과를 포함한 전가밀착 결합 모델을 사용하여 계산한 최대 3나노미터 직경의 탄소나노튜브 밴드 갭의 산란도는 탄소나노튜브[9] 연구 초기에 나타났고 [14]리뷰에서 재인쇄되었다.

트랜지스터 응용 동기

카본 나노튜브의 밴드갭은 키랄 각도와 직경의 직접적인 영향을 받습니다.이러한 특성을 제어할 수 있다면 CNT는 미래 나노 스케일 트랜지스터 소자의 유망한 후보가 될 것입니다.또한 CNT의 완전하고 중공인 실린더 구조에는 경계가 없기 때문에 경계 산란이 없다.CNT는 전방 산란과 후방 산란만 허용되는 준1D 물질로 탄소나노튜브의 자유 경로가 일반적으로 마이크로미터 정도로 긴 것을 의미한다.그 결과 비교적 긴 길이와 [15]저장의 나노튜브에서 준탄도수송을 관찰할 수 있다.SP2 구성의 강력한 공유 탄소-탄소 결합 때문에 탄소 나노튜브는 화학적으로 비활성이며 큰 전류를 운반할 수 있습니다.이론적으로 카본 나노튜브는 다이아몬드나 사파이어와 마찬가지로 열을 전도할 수 있으며, 소형화된 치수로 인해 CNTFET는 실리콘 기반 [16]장치보다 훨씬 적은 전력을 사용하여 안정적으로 전환해야 합니다.

디바이스 제작

CNTFET 장치에는 여러 가지 유형이 있습니다. 가장 일반적인 기하학적 구조에 대한 일반적인 조사가 아래에 나와 있습니다.

백게이트 CNTFET

카본나노튜브(CNT) 전계효과 트랜지스터를 제작하기 위한 최초의 기술은 이산화규소 기판에 평행한 금속 스트립을 미리 패턴화한 후 CNT를 랜덤 [1][2]패턴으로 위에 퇴적시키는 것이었습니다.우연히 두 개의 금속 스트립에 떨어진 반도체 CNT는 기본적인 전계효과 트랜지스터에 필요한 모든 요건을 충족합니다.한쪽 금속 스트립은 "소스" 접점이고 다른 한쪽은 "드레인" 접점입니다.산화실리콘 기판을 게이트 산화물로 사용할 수 있으며 뒷면에 금속 접점을 추가하면 반도체 CNT를 게이트할 수 있습니다.

이 기술은 최적화되지 않은 트랜지스터를 위해 만들어진 몇 가지 단점으로 인해 어려움을 겪었습니다.첫 번째 금속 접촉은 CNT와 거의 접촉하지 않았습니다. 왜냐하면 나노튜브가 CNT 위에 놓여있기 때문에 접촉 면적이 매우 작았기 때문입니다.또한 CNT의 반도체 특성으로 인해 금속-반도체 [17]계면에 쇼트키 장벽이 형성되어 접촉 저항이 증가합니다.두 번째 단점은 백게이트 디바이스 지오메트리에 의한 것입니다.그 두께는 저전압으로 소자의 온/오프를 전환하는 것을 어렵게 만들었으며, 제조 공정으로 인해 게이트 유전체와 [18]CNT 사이의 접촉 불량으로 이어졌습니다.

최상위 게이트 CNTFET

결국 연구자들은 백게이트 방식에서 보다 고도의 탑게이트 제작 프로세스로 [18]이행했습니다.제1공정에서는 산화실리콘 기판상에 단벽 카본나노튜브를 퇴적시킨다.그리고 나서 개별 나노튜브는 원자력 현미경이나 주사 전자 현미경을 통해 배치된다.개별 튜브를 분리한 후 고해상도 전자빔 리소그래피를 사용하여 소스 및 드레인 접점을 정의하고 패턴화한다.고온 아닐 공정은 접촉자와 CNT의 [19]접착성을 향상시켜 접촉 저항을 저감한다.그런 다음 증발 또는 원자층 증착을 통해 나노튜브 위에 얇은 탑게이트 유전체를 퇴적시킨다.마지막으로 게이트 유전체 위에 상부 게이트 접점을 퇴적시켜 처리를 완료한다.

게이트 접점은 백게이트 케이스와는 달리 서로 전기적으로 격리되기 때문에 톱게이트 CNTFET 어레이를 동일한 웨이퍼 상에 제작할 수 있다.또, 게이트 유전체의 얇은 두께에 의해, 낮은 게이트 전압을 이용해 나노튜브에 대해 보다 큰 전계를 발생시킬 수 있다.이러한 장점은 제조 프로세스가 더 복잡하지만 일반적으로 상위 게이트 장치가 백 게이트 CNTFET보다 선호된다는 것을 의미합니다.

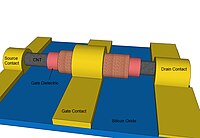

랩어라운드 게이트 CNTFET

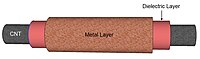

랩 어라운드게이트 CNTPET(게이트 [20]만능 CNTPET라고도 함)는 2008년에 개발되어 탑게이트 디바이스 지오메트리를 한층 더 개량한 것입니다.CNT의 금속 게이트 접점에 가까운 부분만 게이트하는 것이 아니라 나노튜브 전체 둘레가 게이트된다.이를 통해 CNTFET의 전기적 성능이 이상적으로 향상되어 누출 전류를 줄이고 장치 켜기/끄기 비율을 개선할 수 있습니다.

디바이스 제작은 먼저 CNT를 게이트 유전체로 감싸고 원자층 [21]증착을 통한 게이트 접점으로 시작합니다.이렇게 감싼 나노튜브는 절연 기판 위에 용액을 퇴적시켜 나노튜브의 끝부분을 드러내고 포장지를 부분적으로 에칭하여 떼어냅니다.그런 다음 소스, 드레인 및 게이트 접점은 CNT 끝과 금속 외부 게이트 랩에 부착됩니다.

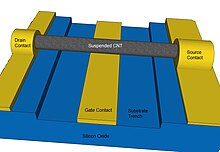

서스펜드 CNTFET

또 다른 CNTFET 디바이스 지오메트리는 나노튜브를 트렌치 위에 매달아 기판 및 게이트 [22]산화물과의 접촉을 줄이는 것을 포함한다.이 기술은 CNT-기판 인터페이스에서의 산란을 줄여 디바이스 [22][23][24]성능을 향상시킬 수 있는 장점이 있습니다.현탁 CNTFET를 제조하는 방법에는 [22]촉매 입자를 사용하여 트렌치 위에 성장시킨 후 기판에 전사한 후 [24]아래 유전체를 언더 에칭하고 트렌치 [23]기판에 전사 인쇄하는 방법 등 여러 가지가 있습니다.

CNTFET의 주요 문제는 게이트 유전체(일반적으로 공기 또는 진공)로 사용할 수 있는 재료 옵션이 매우 제한적이라는 것입니다. 게이트 바이어스를 적용하면 나노튜브가 게이트에 더 가까이 당겨지는 효과가 있어 나노튜브가 게이트될 수 있는 양에 상한을 둡니다.이 기술은 또한 짧은 나노튜브에만 효과가 있습니다. 긴 튜브는 가운데에서 구부러지고 게이트 쪽으로 처져 금속 접촉에 닿아 장치를 단락시킬 수 있기 때문입니다.일반적으로 현탁 CNTFET는 상업적인 용도로는 실용적이지 않지만 깨끗한 나노튜브의 고유 특성을 연구하는 데 유용할 수 있습니다.

CNTFET 재료 고려 사항

CNTFET를 제작할 때 사용할 재료를 고려할 때 일반적인 결정을 내려야 합니다.반도체 단벽 카본 나노튜브는 적어도 낮은 소스/드레인 바이어스에서는 완전히 꺼질 수 있기 때문에 금속 단벽 및 금속 다벽 튜브보다 선호된다.CNT 반도체에 적합한 접촉 재료를 찾기 위해 많은 노력을 기울였습니다. 지금까지 최고의 재료는 Palladium입니다. Palladium의 작업 기능이 나노튜브와 거의 일치하고 CNT에 매우 [25]잘 밀착되기 때문입니다.

I-V 특성

CNT-금속 접점의 경우 금속과 CNT의 다른 작업 기능으로 인해 소스 및 드레인에서 쇼트키 장벽이 발생하며, 이러한 장벽은 은, 티타늄, 팔라듐 및 [27]알루미늄과 같은 금속으로 구성됩니다.비록 숏키 장벽 다이오드와 같이 장벽이 이 FET를 하나의 유형의 반송파만 전송하도록 만들었지만, 금속-CNT 인터페이스를 통한 반송파 전송은 숏키 장벽을 통과하는 양자 기계 터널링에 의해 지배됩니다.CNTFET는 게이트 필드를 통해 쉽게 얇아질 수 있기 때문에 터널을 통과하면 상당한 전류 기여가 발생합니다.CNTFET는 양극성이며 전자 또는 홀 또는 전자와 홀을 동시에 [27]주입할 수 있습니다.이 때문에 숏키 장벽의 두께가 중요한 요소가 됩니다.

CNTFET는 게이트에 양의 바이어스가 인가되면 전자를 전도하고, 음의 바이어스가 인가되면 드레인 전류가 인가되는 게이트 [28]전압의 크기에 따라 증가합니다.V = Vds/2 주변에서는g 전류에 대한 전자 및 홀 기여량이 동일하기 때문에 전류가 최소가 됩니다.

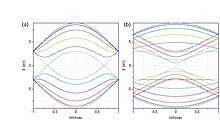

다른 FET와 마찬가지로 인가된 게이트 전압이 임계값 전압보다 낮지 않은 한 드레인 전류는 드레인 바이어스가 증가함에 따라 증가합니다.설계 파라미터가 다른 평면 CNTPET의 경우 채널 길이가 짧은 FET는 더 높은 포화전류를 생성하며, 길이가 일정하게 유지되는 더 작은 직경으로 구성된 FET에 대해서도 포화 드레인 전류가 높아집니다.원통형 CNTFET의 경우 CNT는 최종적으로 게이트 [29]단자가 되는 금속 접점으로 둘러싸인 산화층으로 둘러싸여 있기 때문에 평면 CNTFET보다 높은 드레인 전류가 구동되는 것이 분명하다.

드레인 전류의 이론적 도출

탑 게이트 CNT 트랜지스터의 드레인 전류에 대한 이론적 조사는 Kazierski와 동료들에 의해 [30]수행되었습니다.CNT 트랜지스터에 전계가 인가되면 소스와 드레인에서 튜브로 이동 전하가 유도됩니다.이러한 전하는 소스S N에 의해 채워진 양의 속도 상태와 드레인D [30]N에 의해 채워진 음의 속도 상태의 밀도로부터 생성되며, 이러한 밀도는 페르미-디락 확률 분포에 의해 결정된다.

그리고 평형 전자 밀도는

- 0 2µ - +D ( ) ( - ) ( \ N { 0 } ={ - \ + \ ( E - E _ E _ { } )、 D

여기서 채널 D(ESF), U 및DF U의 상태 밀도는 다음과 같이 정의됩니다.

용어 ( - / )( \ \ (E - E _ {} /)는 브래킷 내부의 값이 양의 경우 1이고 음의 경우 0입니다.V는SC CNT 에너지가 외부 단자 전압의 영향을 받고 다음과 같은 비선형 방정식에 의해 단자 용량에서 장치 단자 전압 및 전하와 암묵적으로 관련이 있음을 나타내는 자체 일관성 전압입니다.

여기서t Q는 단자 캐패시턴스에 저장된 전하를 나타내고, 총 단자 캐패시턴스Σ C는 위 그림에 표시된 게이트, 드레인, 소스 및 기판 캐패시턴스의 합계를 나타냅니다.자기 정합 전압 방정식의 해법에 대한 표준 접근법은 뉴턴-라프슨 반복 방법을 사용하는 것입니다.CNT 탄도 수송 이론에 따르면 나노튜브를 통한 비평형 전하의 수송에 의해 발생하는 드레인 전류는 페르미-디락 통계를 사용하여 계산할 수 있다.

여기서0 F는 차수 0의 페르미-디락 적분, k는 볼츠만 상수, T는 온도, δ환원 플랑크 상수이다.이 방정식은 자기 정합 전압을 알고 있는 한 쉽게 풀 수 있습니다.그러나 반복적인 방법으로 자기 정합 전압을 해결해야 하는 경우에는 계산에 시간이 걸릴 수 있으며, 이것이 이 계산의 주요 결점입니다.

주요 장점

이 섹션은 목록 형식이지만 산문으로 더 잘 읽힐 수 있습니다. 가능 (2022년 3월) |

MOSFET와의 비교

CNTFET는 성능 면에서 MOSFET와 비교하여 다른 특성을 나타냅니다.평판 게이트 구조에서 p-CNTFET는 0.6V의 게이트 오버드라이브에서 단위폭당 온전류의 최대 1500A/m를 생성하는 반면 p-MOSFET는 동일한 게이트 [31]전압에서 최대 500A/m를 발생한다.이러한 온전류 이점은 높은 게이트 캐패시턴스와 개선된 채널 전송에서 비롯됩니다.CNTFET의 단위 폭당 유효 게이트 캐패시턴스는 p-MOSFET의 약 2배이기 때문에 CNTFET의 [29]경우 고k 게이트 유전체와의 호환성이 확실한 이점이 됩니다.CNTFET의 반송파 속도는 MOSFET보다 약 2배 높아져 이동성과 밴드 구조가 향상되었습니다.또한 CNTFET는 약 4배 높은 트랜스컨덕턴스를 [citation needed]가지고 있습니다.

첫 번째 10나노미터 미만의 CNT 트랜지스터는 0.5V의 동작 전압에서 직경 정규화 전류 밀도(2.41mA/μm)의 4배 이상으로 최고의 경쟁 실리콘 소자를 능가하는 성능을 발휘했습니다.CNTFET의 역 서브 임계값 기울기는 94mV/[32]decade였습니다.

열방산

CNT의 전류 감소와 연소는 수백 켈빈의 온도가 상승하기 때문에 발생할 수 있습니다.일반적으로 자기발열효과는 방열기구가 다르기 때문에 반도체 CNTFET는 금속보다 훨씬 덜하다.CNTFET에서 발생하는 열의 일부분이 채널을 통해 소산됩니다.열은 불균일하게 분포되어 있으며 채널의 [33]소스 측과 드레인 측에 가장 높은 값이 표시됩니다.따라서 소스 영역과 드레인 영역 근처에서 온도가 상당히 낮아집니다.반도체 CNT의 경우 온도 상승은 실리콘에 비해 I-V 특성에 상대적으로 작은 영향을 미칩니다.

단점들

수명(열화)

탄소 나노튜브는 [citation needed]산소에 노출되면 며칠 안에 분해된다.나노튜브를 다른 폴리머로 수동화하고 [citation needed]수명을 늘리는 연구가 여러 차례 행해져 왔다.

탄소나노튜브는 최근 몇 달 동안, 그리고 그 이상 동안 [34]계속 작동해도 공기 중에 안정적이라는 것이 증명되었다.게이트 전압이 인가되는 동안 장치 전류에서 바람직하지 않은 드리프트/세틀링이 발생할 수 있지만 게이트 변경으로 인해 임계값 [34]전압의 변화가 거의 없이 이 동작이 빠르게 재설정됩니다.

신뢰성.

카본나노튜브는 높은 전계나 온도 구배에서 작동할 때 신뢰성 문제가 나타났다.아발란체 파괴는 반도체 CNT에서 발생하고 줄 파괴는 금속 CNT에서 발생합니다.실리콘의 눈사태 거동과 달리 CNT의 눈사태는 온도에 거의 의존하지 않습니다.눈사태 지점보다 높은 전압을 가하면 줄 가열이 발생하고 CNT가 최종적으로 [35]분해됩니다.이 신뢰성 문제는 이미 연구되었으며, 멀티채널 구조를 통해 CNTFET의 신뢰성을 향상시킬 수 있다는 것이 밝혀졌습니다.멀티채널 CNTPET는 몇 개월 후에도 안정적인 성능을 유지할 수 있지만, 싱글채널 CNTPET는 일반적으로 대기 [36]중 몇 주 후에 마모됩니다.멀티채널 CNTFET는 일부 채널이 고장나도 전기적 특성이 약간 변경되어도 계속 작동합니다.

대량 생산의 어려움, 생산 비용

CNT는 실리콘에 비해 강성, 강도, 끈기 등 독특한 특성이 있지만 현재 양산 기술이 없고 원가도 높다.제작의 어려움을 극복하기 위해 직접 성장, 용액의 적하, 다양한 전사 인쇄 기술 [37]등 여러 가지 방법이 연구되었습니다.가장 유망한 대량생산 방법은 미리 생산된 나노튜브를 원하는 위치로 어느 정도 자체 조립하는 것입니다.많은 튜브를 개별적으로 조작하는 것은 대규모로 실용적이지 않으며 최종 위치에서 튜브를 키우는 것은 많은 문제를 야기합니다.

장래의 일

CNTFET와 관련된 향후 가장 바람직한 작업은 신뢰성이 높고 생산 비용이 저렴하거나 성능이 향상된 트랜지스터가 될 것입니다.예를 들어 CNT와 금속 접점 사이의 쇼트키 장벽과 같은 내부 CNT 트랜지스터에 외부 효과를 추가하는 것, [30]단일 게이트에 있는 여러 CNT, 채널 프린지 용량, 기생 소스/드레인 저항 및 산란 효과에 의한 직렬 저항.

레퍼런스

- ^ a b Dekker, Cees; Tans, Sander J.; Verschueren, Alwin R. M. (1998). "Room-temperature transistor based on a single carbon nanotube". Nature. 393 (6680): 49–52. Bibcode:1998Natur.393...49T. doi:10.1038/29954. S2CID 4403144.

- ^ a b Martel, R.; Schmidt, T.; Shea, H. R.; Hertel, T.; Avouris, Ph. (1998). "Single- and multi-wall carbon nanotube field-effect transistors" (PDF). Applied Physics Letters. 73 (17): 2447. Bibcode:1998ApPhL..73.2447M. doi:10.1063/1.122477.

- ^ 반도체 국제 기술 로드맵 2011년 8월 25일 Wayback Machine 2009 Edition에서 아카이브

- ^ Avouris, P; Chen, J (2006). "Nanotube electronics and optoelectronics". Materials Today. 9 (10): 46–54. doi:10.1016/S1369-7021(06)71653-4.

- ^ a b c Mintmire, J.W.; Dunlap, B.I.; White, C.T. (3 February 1992). "Are fullerene tubules metallic?". Phys. Rev. Lett. 68 (5): 631–634. Bibcode:1992PhRvL..68..631M. doi:10.1103/PhysRevLett.68.631. PMID 10045950.

- ^ a b c d e Hamada, N.; Sawada, S.; Oshiyama, A. (9 March 1992). "New one-dimensional conductors: graphitic microtubules". Phys. Rev. Lett. 68 (10): 1579–1581. Bibcode:1992PhRvL..68.1579H. doi:10.1103/PhysRevLett.68.1579. PMID 10045167.

- ^ a b c d Dresselhaus, M.; Dresselhaus, G.; Saito, Riichiro (15 July 1992). "Carbon fibers based on C60 and their symmetry" (PDF). Physical Review B. 45 (11): 6234–6242. Bibcode:1992PhRvB..45.6234D. doi:10.1103/PhysRevB.45.6234. PMID 10000369. Archived from the original (PDF) on July 22, 2011.

- ^ Iijima, Sumio (7 November 1991). "Helical microtubules of graphitic carbon". Nature. 354 (6348): 56–58. Bibcode:1991Natur.354...56I. doi:10.1038/354056a0. S2CID 4302490.

- ^ a b White, C. T.; Mintmire, J. W.; et al. (April 1993). "Chapter 6: Predicting Properties of Fullerenes and their Derivatives". In Billups, W . E.; Ciufolini, M. A. (eds.). Buckminsterfullerenes. VCH Publishers, Inc., New York, New York. p. 167. ISBN 1-56081-608-2.

- ^ Ouyang, M; Huang, J. L.; Chung, C. L.; Lieber, C. M. (2001). "Energy Gaps in "metallic" single-walled carbon nanotubes". Science. 292 (5517): 702–705. Bibcode:2001Sci...292..702O. doi:10.1126/science.1058853. PMID 11326093. S2CID 19088925.

- ^ White, C.T.; Robertson,D.H; Mintmire, J.W (1993). "Helical and rotational symmetries of nanoscale graphitic tubules". Phys. Rev. B. 68 (9): 5485–5488. Bibcode:1993PhRvB..47.5485W. doi:10.1103/PhysRevB.47.5485. PMID 10006726.

- ^ Mintmire, J.W.; White, C.T. (1995). "Electronic and structural properties of carbon nanotubes". Carbon. 33 (7): 891–902. doi:10.1016/0008-6223(95)00018-9.

- ^ Wildoer J.W.G.; Venema, L.C.; Rinzler, A.G.; Smalley, R.E.; Dekker, C. (1998). "Electronic structure of atomically resolved carbon nanotubes". Nature. 391 (6662): 58–62. Bibcode:1998Natur.391...59W. doi:10.1038/34139. S2CID 205003208.

- ^ White, C.T.; Mintmire, J.W (2005). "Fundamental properties of single-wall carbon nanotubes". J. Phys. Chem. B. 109 (1): 52–65. doi:10.1021/jp047416. PMID 16850984.

- ^ H. 다이, A. 제이비, E. 팝, D.Mann, Y. Lu, "탄소 나노튜브의 전기적 특성과 전계효과 트랜지스터", 나노: 개요 보고서 및 리뷰 1, 1 (2006)

- ^ Collins, P.G.; Avouris, P. (2000). "Nanotubes for Electronics". Scientific American. 283 (6): 62–69. Bibcode:2000SciAm.283f..62C. doi:10.1038/scientificamerican1200-62. PMID 11103460.

- ^ Heinze, S; Tersoff, J; Martel, R; Derycke, V; Appenzeller, J; Avouris, P (2002). "Carbon nanotubes as Schottky barrier transistors" (PDF). Physical Review Letters. 89 (10): 106801. arXiv:cond-mat/0207397. Bibcode:2002PhRvL..89j6801H. doi:10.1103/PhysRevLett.89.106801. PMID 12225214. S2CID 119093126. Archived from the original (PDF) on December 3, 2008.

- ^ a b Wind, S. J.; Appenzeller, J.; Martel, R.; Derycke, V.; Avouris, Ph. (2002). "Vertical scaling of carbon nanotube field-effect transistors using top gate electrodes" (PDF). Applied Physics Letters. 80 (20): 3817. Bibcode:2002ApPhL..80.3817W. doi:10.1063/1.1480877. Archived from the original (PDF) on 2011-07-03.

- ^ Lim, Seong Chu (November 2006). "A strategy for forming robust adhesion with the substrate in a carbon-nanotube field-emission array". Carbon. 44 (13): 2809. doi:10.1016/j.carbon.2006.03.030.

- ^ Chen, Zhihong; Farmer, Damon; Xu, Sheng; Gordon, Roy; Avouris, Phaedon; Appenzeller, Joerg (2008). "Externally Assembled Gate-All-Around Carbon Nanotube Field-Effect Transistor". IEEE Electron Device Letters. 29 (2): 183–185. Bibcode:2008IEDL...29..183C. doi:10.1109/LED.2007.914069. S2CID 18509168.

- ^ Farmer, DB; Gordon, RG (2006). "Atomic layer deposition on suspended single-walled carbon nanotubes via gas-phase noncovalent functionalization". Nano Letters. 6 (4): 699–703. Bibcode:2006NanoL...6..699F. doi:10.1021/nl052453d. PMID 16608267.

- ^ a b c Cao, J; Wang, Q; Dai, H (2005). "Electron transport in very clean, as-grown suspended carbon nanotubes". Nature Materials. 4 (10): 745–9. arXiv:cond-mat/0509125. Bibcode:2005NatMa...4..745C. doi:10.1038/nmat1478. PMID 16142240. S2CID 36444609.

- ^ a b Sangwan, V. K.; Ballarotto, V. W.; Fuhrer, M. S.; Williams, E. D. (2008). "Facile fabrication of suspended as-grown carbon nanotube devices". Applied Physics Letters. 93 (11): 113112. arXiv:0909.3679. Bibcode:2008ApPhL..93k3112S. doi:10.1063/1.2987457. S2CID 119260715.

- ^ a b Lin, Yu-Ming; Tsang, James C; Freitag, Marcus; Avouris, Phaedon (2007). "Impact of oxide substrate on electrical and optical properties of carbon nanotube devices" (PDF). Nanotechnology. 18 (29): 295202. Bibcode:2007Nanot..18C5202L. doi:10.1088/0957-4484/18/29/295202.

- ^ Javey, Ali; Guo, Jing; Wang, Qian; Lundstrom, Mark; Dai, Hongjie (2003). "Ballistic carbon nanotube field-effect transistors" (PDF). Nature. 424 (6949): 654–7. Bibcode:2003Natur.424..654J. doi:10.1038/nature01797. PMID 12904787. S2CID 1142790. Archived from the original (PDF) on July 24, 2008.

- ^ Zhao, Y.; et al. (2014). "CNT Mobility". doi:10.4231/D3V698C9Z.

{{cite journal}}:Cite 저널 요구 사항journal=(도움말) - ^ a b Avouris, Phaedon; Chen, Zhihong; Perebeinos, Vasili (2007). "Carbon-based electronics". Nature Nanotechnology. 2 (10): 605–15. Bibcode:2007NatNa...2..605A. doi:10.1038/nnano.2007.300. PMID 18654384.

- ^ P.Avouris et al, "카본 나노튜브를 사용한 전자 및 옵토일렉트로닉스", 2010년 10월 8일 Wayback Machine American Institute of Physics, 2004년 6월/7월 18-21일 아카이브(pdf 버전)

- ^ a b S. Rasmita et al, "탄소나노튜브 전계효과 트랜지스터 시뮬레이션", 국제전자공학연구저널, 117~125권, No.2(2009)

- ^ a b c Kazmierski, Tom J.; Zhou, Dafeng; Al-Hashimi, Bashir M.; Ashburn, Peter (2010). "Numerically Efficient Modeling of CNT Transistors with Ballistic and Nonballistic Effects for Circuit Simulation" (PDF). IEEE Transactions on Nanotechnology. 9 (1): 99–107. Bibcode:2010ITNan...9...99K. doi:10.1109/TNANO.2009.2017019. S2CID 8846760.

- ^ Jing Guo; Datta, S.; Lundstrom, M.; Brink, M.; McEuen, P.; Javey, A.; Hongjie Dai; Hyoungsub Kim; McIntyre, P. (2002). "Assessment of silicon MOS and carbon nanotube FET performance limits using a general theory of ballistic transistors" (PDF). Digest. International Electron Devices Meeting. p. 711. doi:10.1109/IEDM.2002.1175937. ISBN 0-7803-7462-2.

- ^ Franklin, Aaron D.; Luisier, Mathieu; Han, Shu-Jen; Tulevski, George; Breslin, Chris M.; Gignac, Lynne; Lundstrom, Mark S.; Haensch, Wilfried (2012-02-08). "Sub-10 nm Carbon Nanotube Transistor". Nano Letters. 12 (2): 758–762. Bibcode:2012NanoL..12..758F. doi:10.1021/nl203701g. ISSN 1530-6984. PMID 22260387. S2CID 12194219.

- ^ Ouyang, Yijian; Guo, Jing (2006). "Heat dissipation in carbon nanotube transistors". Applied Physics Letters. 89 (18): 183122. Bibcode:2006ApPhL..89r3122O. doi:10.1063/1.2382734.

- ^ a b Noyce, Steven G.; Doherty, James L.; Cheng, Zhihui; Han, Hui; Bowen, Shane; Franklin, Aaron D. (2019-02-05). "Electronic Stability of Carbon Nanotube Transistors Under Long-Term Bias Stress". Nano Letters. American Chemical Society (ACS). 19 (3): 1460–1466. Bibcode:2019NanoL..19.1460N. doi:10.1021/acs.nanolett.8b03986. ISSN 1530-6984. PMID 30720283.

- ^ Pop, Eric; Dutta, Sumit; Estrada, David; Liao, Albert (2009). "Avalanche, joule breakdown and hysteresis in carbon nanotube transistors" (PDF). 2009 IEEE International Reliability Physics Symposium (IRPS 2009). p. 405. doi:10.1109/IRPS.2009.5173287. ISBN 978-1-4244-2888-5.

- ^ C. Changxin과 Z.야페이, "나노웰드 카본 나노튜브: 전계효과 트랜지스터에서 '태양광 마이크로셀' 나노과학기술 시리즈(2009년), 63f ISBN 3-642-01498-4페이지

- ^ Chang-Jian, Shiang-Kuo; Ho, Jeng-Rong; John Cheng, J.-W. (2010). "Characterization of developing source/drain current of carbon nanotube field-effect transistors with n-doping by polyethylene imine". Microelectronic Engineering. 87 (10): 1973–1977. doi:10.1016/j.mee.2009.12.019.

가진 지수로 설명할 수 있다.정수

가진 지수로 설명할 수 있다.정수

![{\displaystyle \theta =\tan ^{-1}[{\sqrt {3}}\,n/(2m+n)]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/44bdad0652d145e2caa1f557844d5425bde736a5)

정수입니다.

정수입니다.

탄소나노튜브의 밴드갭은 비교적 작으나 나노튜브 직경이 약

탄소나노튜브의 밴드갭은 비교적 작으나 나노튜브 직경이 약

![I_{{DS}}={\frac {2qkT}{\pi {\hbar }}}\left[F_{0}\left({\frac {U_{{SF}}}{kT}}\right)-F_{0}\left({\frac {U_{{DF}}}{kT}}\right)\right]](https://wikimedia.org/api/rest_v1/media/math/render/svg/bad7659b78100973438a38557bb8d1c827f1df32)