멀티스레딩(컴퓨터 아키텍처)

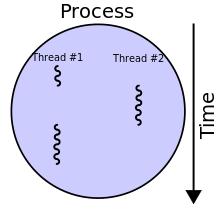

Multithreading (computer architecture)컴퓨터 아키텍처에서 멀티스레딩이란 중앙처리장치(CPU)(또는 멀티코어 프로세서의 단일 코어)가 운영체제에서 지원되는 여러 개의 실행 스레드를 동시에 제공하는 기능입니다.이 접근방식은 멀티프로세싱과는 다릅니다.멀티스레드 어플리케이션에서는 스레드는 컴퓨팅 유닛, CPU 캐시 및 Translation Lookaside Buffer(TLB)를 포함한 단일 또는 여러 코어의 리소스를 공유합니다.

멀티프로세서 시스템이 하나 이상의 코어에 복수의 완전한 처리 유닛을 포함할 경우 멀티스레딩은 명령 수준의 병렬화뿐만 아니라 스레드 수준의 병렬화를 사용함으로써 단일 코어의 활용도를 높이는 것을 목표로 한다.두 기술은 상호 보완적이기 때문에 여러 개의 멀티스레딩 CPU와 여러 개의 멀티스레딩 코어를 가진 CPU가 있는 거의 모든 최신 시스템 아키텍처에서 결합됩니다.

개요

멀티스레딩 패러다임은 1990년대 후반 이후 명령 수준의 병렬화를 더욱 활용하려는 노력이 교착상태에 빠지면서 더욱 인기를 끌고 있다.이를 통해 throughput 컴퓨팅의 개념은 트랜잭션 처리라는 보다 전문화된 분야에서 다시 등장할 수 있었습니다.단일 스레드 또는 단일 프로그램의 속도를 높이는 것은 매우 어렵지만 대부분의 컴퓨터 시스템은 실제로 여러 스레드 또는 프로그램 간에 멀티태스킹을 수행합니다.따라서 모든 태스크의 throughput을 개선하는 기술은 전체적인 성능 향상을 가져옵니다.

throughput 컴퓨팅의 2가지 주요 기술은 멀티스레딩과 멀티프로세싱입니다.

이점

스레드에 캐시 누락이 많으면 다른 스레드는 사용되지 않는 컴퓨팅 리소스를 계속 활용할 수 있습니다.이러한 리소스는 1개의 스레드만 실행되면 아이돌 상태가 되기 때문에 전체적인 실행 속도가 빨라질 수 있습니다.또한 스레드가 CPU의 모든 컴퓨팅 리소스를 사용할 수 없는 경우(명령어는 서로 결과에 따라 달라지기 때문에), 다른 스레드를 실행하면 해당 리소스가 유휴 상태가 되는 것을 방지할 수 있습니다.

단점들

캐시나 Translation Lookaside Buffer(TLB; 변환 룩사이드버퍼) 등의 하드웨어 리소스를 공유할 때 여러 스레드가 서로 간섭할 수 있습니다.그 결과 스레드 전환 하드웨어를 수용하기 위해 필요한 저주파수 또는 추가 파이프라인 스테이지에 의해 스레드 1개만 실행되어도 스레드 1개의 실행시간이 향상되지 않고 저하될 수 있다.

전체적인 효율은 다양합니다.인텔은 하이퍼스레딩 [1]테크놀로지를 통해 최대 30%의 향상을 주장하지만 최적화되지 않은 부동소수점 연산 루프를 실행하는 합성 프로그램은 병렬 실행 시 100%의 속도 향상을 실현합니다.한편, MMX 또는 AltiVec 확장 기능을 사용하여 데이터 프리페치를 실행하는 수동 조정 어셈블리 언어 프로그램에서는 캐시 누락이나 유휴 컴퓨팅 리소스가 발생하지 않습니다.따라서 이러한 프로그램은 하드웨어 멀티스레딩의 이점을 얻을 수 없으며 공유 리소스에 대한 경합으로 인해 성능이 저하될 수 있습니다.

소프트웨어의 관점에서 볼 때, 멀티스레딩에 대한 하드웨어 지원은 소프트웨어에 더 잘 나타나기 때문에 멀티프로세싱보다 애플리케이션 프로그램과 운영 체제 모두에 더 많은 변경이 필요합니다.멀티스레딩을 지원하기 위해 사용되는 하드웨어 기술은 종종 컴퓨터 멀티태스킹에 사용되는 소프트웨어 기술과 병행됩니다.스레드 스케줄링도 멀티스레딩의 주요 문제입니다.

멀티스레딩 유형

인터리브/임시 멀티스레딩

저밀도 멀티스레딩

가장 단순한 유형의 멀티스레딩은 일반적으로 긴 지연 시간 스톨을 생성하는 이벤트에 의해 차단될 때까지 하나의 스레드가 실행될 때 발생합니다.이러한 장애는 오프칩 메모리에 액세스해야 하는 캐시 누락일 수 있으며, 데이터가 반환되는 데 수백 개의 CPU 사이클이 걸릴 수 있습니다.스레드 프로세서는 스톨이 해결되기를 기다리는 대신 실행 준비가 된 다른 스레드로 실행을 전환합니다.이전 스레드의 데이터가 도착한 경우에만 이전 스레드가 실행 가능한 스레드 목록에 다시 배치됩니다.

예를 들어 다음과 같습니다.

- Cycle i: 스레드 A의 명령 j가 발행됩니다.

- Cycle i + 1: 스레드 A로부터의 명령 j + 1이 발행됩니다.

- Cycle i + 2: 스레드A로부터의 명령 j + 2가 발행됩니다.이것은 모든 캐시에서 누락되는 로드 명령입니다.

- Cycle i + 3: 스레드스케줄러가 호출되어 스레드B로 전환됩니다.

- Cycle i + 4: 스레드 B로부터의 명령 k가 발행됩니다.

- Cycle i + 5: 스레드 B로부터의 명령 k + 1이 발행됩니다.

개념적으로 실시간 운영 체제에서 사용되는 공동 멀티태스킹과 유사합니다. 즉, 태스크는 특정 유형의 이벤트를 기다려야 할 때 실행 시간을 자발적으로 포기합니다.이런 유형의 멀티스레딩을 블록, 공동 또는 거친 멀티스레딩이라고 합니다.

멀티스레딩 하드웨어 지원의 목적은 차단된 스레드와 실행 가능한 다른 스레드 간에 빠른 전환을 가능하게 하는 것입니다.스레드에서 다른 스레드로 전환한다는 것은 하드웨어가 하나의 레지스터 세트를 다른 레지스터 세트로 전환하는 것을 의미합니다.이 목적을 달성하기 위해 프로그램 표시 레지스터의 하드웨어와 일부 프로세서 제어 레지스터(프로그램 카운터 등)가 복제됩니다.예를 들어, 2개의 스레드를 빠르게 전환하기 위해 프로세서는 2개의 레지스터 세트로 구성됩니다.

멀티스레딩에 대한 추가 하드웨어 지원을 통해 스레드 전환이 1개의 CPU 사이클로 이루어지므로 성능이 향상됩니다.또, 하드웨어를 추가하면, 각 스레드가 다른 스레드와 하드웨어 자원을 공유하지 않고, 단독으로 실행하는 것처럼 동작할 수 있기 때문에, 멀티스레딩을 서포트하기 위해서 애플리케이션이나 operating system내에서 필요한 소프트웨어 변경의 양을 최소한으로 억제할 수 있습니다.

마이크로컨트롤러와 임베디드 프로세서의 많은 제품군은 인터럽트의 콘텍스트를 빠르게 전환할 수 있도록 여러 레지스터 뱅크를 갖추고 있습니다.이러한 방식은 사용자 프로그램 스레드와 인터럽트 [citation needed]스레드 간의 블록 멀티스레딩의 한 종류로 간주할 수 있습니다.

미세 멀티스레딩

미세 멀티스레딩의 목적은 실행 파이프라인에서 모든 데이터 종속성 스톨을 제거하는 것입니다.하나의 스레드는 다른 스레드와 상대적으로 독립적이기 때문에 파이프라인의 오래된 명령어로부터의 출력이 필요한 파이프라인 단계에서 하나의 명령어가 될 가능성은 적다.개념적으로는 운영체제에서 사용되는 프리엠프티브 멀티태스킹과 비슷합니다.유사적으로 액티브한 각 스레드에 주어진 타임슬라이스는 1개의 CPU 사이클입니다.

예를 들어 다음과 같습니다.

- Cycle i + 1: 스레드 B로부터의 명령이 발행됩니다.

- Cycle i + 2: 스레드 C로부터의 명령이 발행됩니다.

이러한 유형의 멀티스레딩은 처음에 배럴 처리라고 불렸는데, 배럴의 스택은 파이프라인 단계와 그 실행 스레드를 나타냅니다.인터리브, 프리엠프티브, 세밀한 멀티스레딩 또는 타임슬라이스 멀티스레딩은 보다 현대적인 용어입니다.

인터리브 멀티스레딩은 블록 타입의 멀티스레딩에서 논의되는 하드웨어 비용 외에 처리 중인 명령의 스레드 ID를 추적하는 각 파이프라인 스테이지의 추가 비용이 있습니다.또한 파이프라인에서 동시에 실행되는 스레드가 더 많기 때문에 캐시나 TLB 등의 공유 리소스를 더 커야 서로 다른 스레드 간의 스레싱을 방지할 수 있습니다.

동시 멀티스레딩

가장 고급 유형의 멀티스레딩은 슈퍼스케일러 프로세서에 적용됩니다.일반 슈퍼스칼라 프로세서는 CPU 사이클마다 1개의 스레드에서 여러 개의 명령을 발행하는 반면, SMT(Synchaneous Multithreading)에서는 슈퍼스칼라 프로세서가 CPU 사이클마다 여러 스레드에서 명령을 발행할 수 있습니다.이러한 유형의 멀티스레딩은 단일 스레드에 명령 수준의 병렬화가 제한되어 있음을 인식하여 여러 스레드에서 사용 가능한 병렬화를 이용하여 사용되지 않는 문제 슬롯과 관련된 낭비를 줄이려고 합니다.

예를 들어 다음과 같습니다.

- Cycle i: 스레드 A로부터의 명령 j, j+1과 스레드 B로부터의 명령 k를 동시에 발행한다.

- Cycle i + 1: 스레드 A로부터의 명령 j + 2, 스레드 B로부터의 명령 k + 1 및 스레드 C로부터의 명령 m을 동시에 발행한다.

- Cycle i + 2: 스레드 A로부터의 명령 j + 3과 스레드 C로부터의 명령 m + 1, m + 2가 동시에 발행된다.

시만텍과 다른 유형의 멀티스레딩을 구별하기 위해 "임시 멀티스레딩"이라는 용어는 한 번에 한 스레드의 명령만 실행할 수 있는 경우를 나타내는 데 사용됩니다.

시만텍은 인터리브 멀티스레딩에 대해 논의된 하드웨어 비용 외에도 처리 중인 각 명령의 스레드 ID를 추적하는 각 파이프라인 단계의 추가 비용이 있습니다.캐시나 TLB 등의 공유 리소스는 처리 중인 다수의 활성 스레드에 맞게 사이징해야 합니다.

구현에는 DEC(나중의 Compaq) EV8(미완료), 인텔 하이퍼스레딩 테크놀로지, IBM POWER5/POWER7/POWER8/POWER9, IBM z13/z14/z15, Sun Microsystems UltraSPARC T2, Cray XMT, AMD Gundozzzzzor가 포함됩니다.

구현의 상세

주요 연구 분야는 바로 실행할 수 있는 스레드 목록과 실행 가능한 스레드 목록을 신속하게 선택해야 하며, 실행 가능한 스레드 목록과 정지된 스레드 목록을 유지해야 하는 스레드 스케줄러입니다.중요한 서브토픽은 스케줄러가 사용할 수 있는 다양한 스레드priority 스킴입니다.스레드 스케줄러는 완전히 소프트웨어, 완전히 하드웨어 또는 하드웨어/소프트웨어 조합으로 구현될 수 있습니다.

또 다른 연구 분야는 캐시 누락, 스레드 간 통신, DMA 완료 등 스레드 전환의 원인이 되는 이벤트 유형입니다.

멀티스레딩 체계가 권한이 있는 제어 레지스터 및 TLB를 포함하여 소프트웨어에 표시되는 모든 상태를 복제하는 경우 각 스레드에 대해 가상 시스템을 생성할 수 있습니다.이것에 의해, 각 스레드는 같은 프로세서상에서 독자적인 operating system을 실행할 수 있습니다.한편 사용자 모드 상태만 저장하면 필요한 하드웨어가 줄어들기 때문에 동일한 다이 영역 또는 비용으로 동시에 더 많은 스레드를 활성화할 수 있습니다.

「 」를 참조해 주세요.

레퍼런스

- ^ "Intel Hyper-Threading Technology, Technical User's Guide" (PDF). p. 13. Archived from the original (PDF) on 2010-08-21.