현장 프로그래머블 게이트 어레이

Field-programmable gate array

FPGA(Field-Programmable Gate Array)는 제조 후 프로그래밍하거나 재프로그램할 수 있는 집적 회로의 한 종류입니다. 다양한 디지털 기능을 수행하도록 구성할 수 있는 프로그래밍 가능한 로직 블록과 상호 연결의 어레이로 구성됩니다. FPGA는 통신, 자동차, 항공우주 및 산업 분야와 같이 유연성, 속도 및 병렬 처리 기능이 필요한 애플리케이션에 일반적으로 사용됩니다.

FPGA 구성은 일반적으로 애플리케이션별 집적 회로(ASIC)에 사용되는 것과 유사한 하드웨어 설명 언어(HDL)를 사용하여 지정됩니다. 회로 다이어그램은 이전에 구성을 지정하는 데 사용되었습니다.

FPGA의 논리 블록은 복잡한 조합 기능을 수행하도록 구성하거나 AND 및 XOR와 같은 간단한 논리 게이트 역할을 할 수 있습니다. 대부분의 FPGA에서 로직 블록은 또한 메모리 요소를 포함하며, 이는 단순한 플립플롭 또는 보다 완전한 메모리 블록일 수 있습니다.[1] 많은 FPGA를 재프로그램하여 다양한 논리 기능을 구현할 수 있으므로 컴퓨터 소프트웨어에서 수행되는 것처럼 유연한 재구성 가능 컴퓨팅이 가능합니다.

FPGA는 하드웨어와 동시에 시스템 소프트웨어 개발을 시작하고 개발 초기 단계에서 시스템 성능 시뮬레이션을 가능하게 하며 시스템 아키텍처를 최종화하기 전에 다양한 시스템 시행 및 설계 반복을 허용하는 기능으로 인해 임베디드 시스템 개발에서도 역할을 합니다.[2]

FPGA는 시뮬레이션 프로세스의 속도를 높이기 위해 ASIC을 개발하는 동안 일반적으로 사용됩니다.

역사

FPGA 산업은 프로그래머블 읽기 전용 메모리(PROM)와 프로그래머블 로직 디바이스(PLD)에서 싹을 틔웠습니다. PROM과 PLD는 모두 공장이나 현장에서 일괄적으로 프로그래밍할 수 있는 옵션이 있었습니다(필드 프로그래밍 가능).[3]

Altera는 1983년에 설립되어 1984년에 업계 최초로 재프로그래밍 가능한 로직 디바이스인 EP300을 출시했습니다. 이는 패키지에 석영 창을 포함하여 사용자가 장치 구성을 유지하는 EPROM 셀을 지우기 위해 다이에 자외선 램프를 비추게 해줍니다.[4]

Xilinx는 1985년에[3] 최초로 상업적으로 실행 가능한 필드 프로그래머블 게이트 어레이인 XC2064를 생산했습니다.[5] XC2064는 프로그래밍이 가능한 게이트와 게이트 사이에 프로그래밍 가능한 상호 연결 기능을 갖추고 있어 새로운 기술과 시장의 시작이 되었습니다.[6] XC2064에는 64개의 구성 가능한 CLB(논리 블록)가 있으며 2개의 3입력 룩업 테이블(LUT)이 있습니다.[7]

1987년, 해군 표면전센터는 스티브 카셀만(Steve Casselman)이 제안한 600,000개의 재프로그래밍 가능한 게이트를 구현할 컴퓨터를 개발하기 위한 실험에 자금을 지원했습니다. Casselman은 성공적이었고 1992년에 시스템과 관련된 특허가 발행되었습니다.[3]

Altera와 Xilinx는 도전을 받지 않고 경쟁사들이 싹을 틔운 1985년부터 1990년대 중반까지 빠르게 성장하여 시장 점유율의 상당 부분을 잠식했습니다. 1993년까지 액텔(현 마이크로세미)은 시장의 약 18%를 점유하고 있었습니다.[6]

1990년대는 회로의 정교함과 생산량 모두에서 FPGA의 급속한 성장기였습니다. 1990년대 초 FPGA는 주로 통신 및 네트워킹에 사용되었습니다. 10년 말까지 FPGA는 소비자, 자동차 및 산업용 애플리케이션에 진출했습니다.[8]

2013년까지 Altera(31%), Actel(10%), Xilinx(36%)는 함께 FPGA 시장의 약 77%를 차지했습니다.[9]

마이크로소프트와 같은 회사들은 FPGA가 제공하는 와트당 성능의 이점으로 인해 고성능의 계산 집약적인 시스템(예: Bing 검색 엔진을 운영하는 데이터 센터)을 가속화하기 위해 FPGA를 사용하기 시작했습니다.[10] 마이크로소프트는 2014년부터 Bing을 가속화하기 위해 FPGA를 사용하기 시작했으며, 2018년에는 Azure 클라우드 컴퓨팅 플랫폼을 위해 다른 데이터 센터 워크로드 전반에 걸쳐 FPGA를 구축하기 시작했습니다.[11]

성장

다음 타임라인은 FPGA 설계의 여러 측면에서 진행 상황을 나타냅니다.

게이츠

시장규모

- 1985년: 최초의 상업용 FPGA: Xilinx XC2064[5][6]

- 1987: 1,400만[6] 달러

- c. 1993: >3억 8,500만[6][failed verification] 달러

- 2005: 19억[13] 달러

- 2010년 추산: 27억[13] 5천만 달러

- 2013: 54억[14] 달러

- 2020년 예상: 98억[14] 달러

설계시작

설계 시작은 FPGA에 구현하기 위한 새로운 사용자 정의 설계입니다.

설계.

현대의 FPGA는 복잡한 디지털 계산을 구현할 수 있는 충분한 논리 게이트와 RAM 블록을 가지고 있습니다. FPGA는 ASIC가 수행할 수 있는 모든 논리적 기능을 구현하는 데 사용할 수 있습니다. 출하 후 기능을 업데이트할 수 있는 기능, 설계의[17] 일부를 부분적으로 다시 구성하는 기능, ASIC 설계에 비해 낮은 비재회 엔지니어링 비용(일반적으로 높은 단가에도 불구하고)은 많은 애플리케이션에 이점을 제공합니다.[1]

FPGA 설계는 매우 빠른 I/O 속도와 양방향 데이터 버스를 사용하기 때문에 설정 시간과 유지 시간 내에 유효한 데이터의 정확한 타이밍을 확인하는 것이 어렵습니다.[18] 플로어 플래닝은 이러한 타이밍 제약을 충족하기 위해 FPGA 내의 자원 할당에 도움이 됩니다.

일부 FPGA에는 디지털 기능 외에도 아날로그 기능이 있습니다. 가장 일반적인 아날로그 기능은 각 출력 핀에서 프로그램 가능한 슬루 레이트로, 엔지니어는 가볍게 로드된 핀에서 허용할 수 없는 벨이 울리거나 커플링되는 낮은 레이트를 설정할 수 있고, 너무 느리게 실행되는 과도하게 로드된 고속 채널에서 더 높은 레이트를 설정할 수 있습니다.[19][20] 또한 쿼츠 크리스탈 오실레이터 드라이버 회로, 온 칩 저항 캐패시턴스 오실레이터 및 고속 직렬화기(SERDES) 전송 클럭 및 수신기 클럭 복구에 사용되는 전압 제어 오실레이터가 내장된 위상 고정 루프도 일반적입니다. 차동 신호 채널에 연결되도록 설계된 입력 핀의 차동 비교기는 상당히 일반적입니다. 일부 혼합 신호 FPGA에는 아날로그 신호 조절 블록과 함께 주변 아날로그-디지털 변환기(ADC) 및 디지털-아날로그 변환기(DAC)가 통합되어 있어 시스템 온-어-칩(SoC)으로 작동할 수 있습니다.[21] 이러한 장치는 내부 프로그래밍 가능 인터커넥트 패브릭에서 디지털 1과 0을 전송하는 FPGA와 내부 프로그래밍 가능 인터커넥트 패브릭에서 아날로그 값을 전송하는 필드 프로그래밍 가능 아날로그 어레이(FPAA) 사이의 경계를 흐립니다.

논리 블록

가장 일반적인 FPGA 아키텍처는 벤더, I/O 패드 및 라우팅 채널에 따라 CLB(Configurable Logic Block) 또는 LAB(Logic Array Block)라고 불리는 논리 블록의 배열로 구성됩니다.[1] 일반적으로 모든 라우팅 채널은 동일한 폭(신호 수)을 갖습니다. 배열에서 한 행의 높이 또는 한 열의 너비에 여러 개의 I/O 패드가 들어갈 수 있습니다.

"응용 회로는 충분한 자원을 가지고 FPGA에 매핑되어야 합니다. 필요한 로직 블록 및 I/O의 수는 설계에서 쉽게 결정되지만, 동일한 양의 로직을 가진 설계 중에서도 필요한 라우팅 채널의 수는 상당히 다를 수 있습니다. 예를 들어 크로스바 스위치는 동일한 게이트 수를 가진 시스톨릭 어레이보다 훨씬 더 많은 라우팅이 필요합니다. 사용되지 않는 라우팅 채널은 아무런 이점도 제공하지 않으면서 FPGA의 비용을 증가(및 성능을 감소)시키기 때문에 FPGA 제조업체는 룩업 테이블(LUT) 및 I/O 측면에서 적합한 대부분의 설계를 라우팅할 수 있도록 충분한 채널을 제공하려고 노력합니다. 이는 Rent's rule에서 도출된 추정치나 기존 설계에 대한 실험을 통해 결정됩니다."[22]

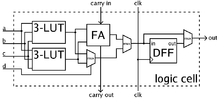

일반적으로 논리 블록은 몇 개의 논리 셀로 구성됩니다. 일반적인 셀은 4-입력 LUT, Full Adder(FA) 및 D-type Flip-flop으로 구성됩니다. LUT는 두 개의 3-입력 LUT로 나누어질 수 있습니다. 일반 모드에서는 첫 번째 멀티플렉서(mux)를 통해 4-입력 LUT로 결합됩니다. 산술 모드에서는 출력이 가산기로 공급됩니다. 모드 선택은 두 번째 먹스에 프로그래밍됩니다. 출력은 세 번째 먹스의 프로그래밍에 따라 동기식 또는 비동기식이 될 수 있습니다. 실제로는 공간을 절약하기 위해 가산기의 전체 또는 일부가 LUT에 함수로 저장됩니다.[23][24][25]

하드블록

현대의 FPGA 제품군은 실리콘에 고정된 더 높은 수준의 기능을 포함하도록 위의 기능을 확장합니다. 이러한 공통 기능을 회로에 내장하면 필요한 면적이 줄어들고 논리적 프리미티브로부터 기능을 구축하는 것에 비해 성능이 향상됩니다. 여기에는 곱셈기, 일반 DSP 블록, 임베디드 프로세서, 고속 I/O 로직 및 임베디드 메모리가 포함됩니다.

고사양 FPGA는 고속 멀티 기가비트 트랜시버와 프로세서 코어, 이더넷 미디어 액세스 제어 장치, PCI 또는 PCI Express 컨트롤러, 외장 메모리 컨트롤러와 같은 하드 IP 코어를 포함할 수 있습니다. 이러한 코어는 프로그래밍 가능한 패브릭과 함께 존재하지만, LUT 대신 트랜지스터로 구성되어 있기 때문에 패브릭 리소스를 상당량 소비하지 않고 ASIC 수준의 성능과 전력 소비를 가지며, 애플리케이션별 로직에 맞게 더 많은 패브릭을 사용할 수 있습니다. 다중 기가비트 송수신기에는 LUT로 구축할 수 없는 구성 요소인 고속 직렬화기 및 병렬화기와 함께 고성능 신호 조절 회로도 포함되어 있습니다. 라인 코딩과 같은 상위 물리 계층(PHY) 기능은 FPGA에 따라 하드 로직에서 직렬화기 및 병렬화기와 함께 구현될 수도 있고 구현되지 않을 수도 있습니다.

소프트코어

하드 매크로 프로세서를 사용하는 대안적인 방법은 FPGA 로직 내에 구현된 소프트 프로세서 IP 코어를 사용하는 것입니다. Nios II, MicroBlaze 및 Mico32는 인기 있는 소프트 코어 프로세서의 예입니다. 많은 최신 FPGA가 런타임에 프로그래밍되어 있기 때문에 현재 당면한 작업에 맞게 자체적으로 재구성하는 CPU인 재구성 가능 컴퓨팅 또는 재구성 가능 시스템에 대한 아이디어가 생겨났습니다. 또한 새로운 비 FPGA 아키텍처가 등장하기 시작했습니다. Stretch S5000과 같은 소프트웨어 구성이 가능한 마이크로프로세서는 동일한 칩에 일련의 프로세서 코어와 FPGA와 같은 프로그래밍 가능 코어를 제공하여 하이브리드 방식을 채택합니다.

통합

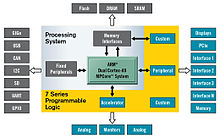

2012년에는 기존 FPGA의 논리 블록 및 상호 연결을 내장 마이크로프로세서 및 관련 주변 장치와 결합하여 프로그래밍 가능한 칩에 완전한 시스템을 형성함으로써 조잡한 아키텍처 접근 방식이 한 단계 더 발전했습니다. 이러한 하이브리드 기술의 예는 FPGA의 로직 패브릭에[27] 내장된 1.0GHz 듀얼 코어 ARM Cortex-A9 MPCore 프로세서를 [26]포함하는 Xilinx Zynq-7000 All Programmable SoC에서 찾을 수 있습니다. Atmel FPSLIC은 AVR 프로세서를 Atmel의 프로그래밍 가능한 로직 아키텍처와 결합하여 사용하는 또 다른 장치입니다. Microsemi SmartFusion 장치는 ARM Cortex-M3 하드 프로세서 코어(최대 512kB의 플래시와 64kB의 RAM 포함)와 멀티채널 아날로그-디지털 변환기 및 디지털-아날로그 변환기와 같은 아날로그 주변기기를 플래시 메모리 기반 FPGA 패브릭에 통합합니다.[citation needed]

클로킹

FPGA 내부의 대부분의 로직은 클럭 신호를 필요로 하는 동기 회로입니다. FPGA는 일반적으로 H 트리로 구현되는 클럭 및 리셋을 위한 전용 글로벌 및 지역 라우팅 네트워크를 포함하므로 최소한의 스큐로 전달할 수 있습니다. FPGA는 새로운 클럭 주파수를 합성하고 지터를 관리하기 위해 아날로그 위상 고정 루프 또는 지연 고정 루프 구성 요소를 포함할 수 있습니다. 복잡한 설계는 서로 다른 주파수 및 위상 관계를 가진 여러 시계를 사용할 수 있으며, 각각은 별개의 시계 도메인을 형성합니다. 이러한 클럭 신호는 오실레이터에 의해 로컬로 생성되거나 데이터 스트림에서 복구될 수 있습니다. 전이성을 방지하기 위해 클럭 도메인 교차 회로를 구축할 때는 주의해야 합니다. 일부 FPGA에는 서로 다른 클럭을 사용할 수 있는 이중 포트 RAM 블록이 포함되어 있어 클럭 도메인을 브리지하는 FIFO 및 이중 포트 버퍼를 구축하는 데 도움이 됩니다.

3D 아키텍처

FPGA의 크기와 전력 소비를 줄이기 위해 Tabula와 Xilinx와 같은 공급업체는 3D 또는 스택형 아키텍처를 도입했습니다.[28][29] Xilinx는 28nm 7시리즈 FPGA를 출시한 후, 3D 구축 및 적층형 다이 어셈블리를 위해 개발된 기술을 사용하여 하나의 패키지에 여러 개의 다이를 사용하여 FPGA 제품 라인에서 가장 밀도가 높은 부품을 구성할 것이라고 말했습니다.

Xilinx의 접근 방식은 여러 개의 활성 FPGA 다이를 실리콘 인터포저(passive interconnect를 운반하는 실리콘 조각)에 나란히 쌓아 올립니다.[29][30] 또한 멀티 다이 구조는 FPGA 패브릭 자체와 매우 빠른 28 Gbit/s 직렬 트랜시버 간에 공정 요구 사항이 다르기 때문에 FPGA의 다른 부분을 다른 공정 기술로 만들 수 있습니다. 이렇게 구축된 FPGA를 이종 FPGA라고 합니다.[31]

Altera의 이기종 접근 방식은 단일 단일 단일 FPGA 다이를 사용하고 인텔의 내장된 멀티 다이 인터커넥트 브리지(EMIB) 기술을 사용하여 다른 다이 및 기술을 FPGA에 연결하는 것입니다.[32]

프로그래밍

FPGA의 동작을 정의하기 위해 사용자는 HDL(Hardware Description Language) 또는 개략적인 설계로 설계를 제공합니다. HDL 폼은 손으로 일일이 그리는 것보다 높은 수준의 기능 동작을 지정할 수 있기 때문에 대형 구조물 작업에 더 적합합니다. 그러나 도식적인 항목을 사용하면 설계 및 구성 요소 모듈을 더 쉽게 시각화할 수 있습니다.

전자 설계 자동화 도구를 사용하여 기술 매핑된 넷리스트를 생성합니다. 그런 다음 일반적으로 FPGA 회사의 독점적인 Place-and-Route 소프트웨어가 수행하는 Place-and-Route라는 프로세스를 사용하여 넷리스트를 실제 FPGA 아키텍처에 맞출 수 있습니다. 사용자는 타이밍 분석, 시뮬레이션 및 기타 검증 및 검증 방법론을 통해 지도, 장소 및 경로 결과를 검증합니다. 설계 및 검증 프로세스가 완료되면 일반적으로 FPGA 공급업체의 독점 소프트웨어를 사용하여 생성된 이진 파일을 사용하여 FPGA를 구성(재)합니다. 이 파일은 직렬 인터페이스(JTAG)를 통해 FPGA/CPLD로 전송되거나 EEPROM과 같은 외부 메모리 장치로 전송됩니다.

가장 일반적인 HDL은 VHDL과 Verilog 뿐만 아니라 System Verilog와 같은 확장입니다. 그러나 그동안 어셈블리어와 동등한 수준으로 비교되던 HDL에서 설계의 복잡성을 줄이기 위한 시도로 대체 언어의 도입을 통해 추상화 수준을 높이려는 움직임이[by whom?] 있습니다. National Instruments의 LabVIEW 그래픽 프로그래밍 언어(때로는 G라고도 함)에는 FPGA 하드웨어를 목표로 하고 프로그래밍하는 데 사용할 수 있는 FPGA 추가 모듈이 있습니다. Verilog는 HDL을 보다 강력하고 유연하게 만드는 프로세스를 단순화하기 위해 만들어졌습니다. 현재 베리로그가 가장 인기가 많습니다. Verilog는 구현의 세부 사항을 숨기기 위해 추상화 수준을 만듭니다. Verilog는 VHDL과 달리 C와 유사한 구문을 가지고 있습니다.[33]

FPGA에서 복잡한 시스템의 설계를 단순화하기 위해 사전에 정의된 복잡한 기능과 회로의 라이브러리가 존재하며, 설계 프로세스의 속도를 높이기 위해 테스트되고 최적화되었습니다. 이러한 미리 정의된 회로를 일반적으로 IP(지식재산권) 코어라고 하며, FPGA 공급업체 및 타사 IP 공급업체에서 사용할 수 있습니다. 그들은 거의 무료가 아니며 일반적으로 독점 라이센스로 출시됩니다. 다른 미리 정의된 회로는 OpenCores(일반적으로 GPL, BSD 또는 유사한 라이센스와 같은 자유 및 오픈 소스 라이센스로 출시됨)와 같은 개발자 커뮤니티 및 기타 소스에서 사용할 수 있습니다. 이러한 디자인은 오픈 소스 하드웨어로 알려져 있습니다.

일반적인 설계 흐름에서 FPGA 애플리케이션 개발자는 설계 프로세스 전반에 걸쳐 여러 단계에서 설계를 시뮬레이션합니다. 처음에 VHDL 또는 Verilog의 RTL 설명은 시스템을 시뮬레이션하고 결과를 관찰하기 위한 테스트 벤치를 만들어 시뮬레이션됩니다. 그런 다음 합성 엔진이 설계를 넷리스트에 매핑한 후 넷리스트를 게이트 수준 설명으로 변환하여 시뮬레이션을 반복하여 오류 없이 합성이 진행되었음을 확인합니다. 마지막으로 설계는 FPGA에 배치되며, 여기서 포인트 전파 지연을 추가할 수 있고 시뮬레이션은 이 값들을 다시 넷리스트에 주석을 달아 다시 실행됩니다.

최근에는 프로그래머들이 FPGA가 제공하는 성능과 전력 효율성을 활용하기 위해 OpenCL(Open Computing Language)을 사용하고 있습니다. OpenCL을 통해 프로그래머는 C 프로그래밍 언어로 코드를 개발하고 OpenCL 컨스트럭트를 사용하여 OpenCL 커널로 FPGA 함수를 목표로 할 수 있습니다.[34] 자세한 내용은 높은 수준의 합성 및 C ~ HDL을 참조하십시오.

대부분의 FPGA는 프로그래밍할 SRAM 기반 접근 방식에 의존합니다. 이러한 FPGA는 시스템 내에서 프로그래밍 및 재프로그래밍이 가능하지만 외부 부팅 장치가 필요합니다. 예를 들어 플래시 메모리 또는 EEPROM 디바이스는 종종 라우팅 및 로직을 제어하는 내부 SRAM에 콘텐츠를 로드할 수 있습니다. SRAM 접근 방식은 CMOS를 기반으로 합니다.

SRAM 접근 방식에 대한 더 드문 대안은 다음과 같습니다.

- 퓨즈: 1회 프로그래밍 가능합니다. 양극성. 쓸모없는.

- 안티퓨즈: 1회 프로그래밍 가능합니다. CMOS. 예: 액텔 SX 및 액셀레이터 패밀리, 퀵로직 이클립스 II 패밀리.[35]

- PROM: 프로그래밍 가능한 읽기 전용 메모리 기술. 플라스틱 포장으로 인해 1회 프로그래밍이 가능합니다. 쓸모없는.

- EPROM: 삭제 가능한 프로그램 가능 읽기 전용 메모리 기술. 한 번만 프로그래밍할 수 있지만 창이 있으면 자외선(UV) 빛으로 지울 수 있습니다. CMOS. 오래된.

- EEPROM: 전기적으로 소거 가능한 프로그램 가능한 읽기 전용 메모리 기술. 플라스틱 패키지에서도 지울 수 있습니다. 일부 EEPROM 장치는 시스템 내에서 프로그래밍할 수 있습니다. CMOS.

- 플래시: 플래시 삭제 EPROM 기술. 플라스틱 패키지에서도 지울 수 있습니다. 일부 플래시 장치는 시스템 내에서 프로그래밍할 수 있지만 모든 플래시 장치는 프로그래밍할 수 없습니다. 일반적으로 플래시 셀은 동급의 EEPROM 셀보다 작기 때문에 제조 비용이 저렴합니다. CMOS. 예: Actel ProASIC 가족입니다.[35]

제조업체

2016년에는 오랜 업계 라이벌인 Xilinx(현재 AMD의 일부)와 Altera(현재 인텔 자회사)가 FPGA 시장을 주도했습니다.[36] 당시 그들은 시장의 거의 90%를 장악했습니다.

Xilinx(현재 AMD)와 Altera(현재 인텔) 모두 Windows 및 Linux(ISE/Vivado 및 Quartus)용 독점 전자 설계 자동화 소프트웨어를 제공하므로 엔지니어가 설계, 분석, 시뮬레이션 및 합성(컴파일)을 수행할 수 있습니다.[37][38]

2010년 3월, Tabula는 고밀도 애플리케이션에 대한 잠재적인 비용 절감을 주장하는 시간 다중화 로직 및 인터커넥트를 사용하는 FPGA 기술을 발표했습니다.[39] 2015년 3월 24일, 타불라는 공식적으로 문을 닫았습니다.[40]

2015년 6월 1일, Intel은 Altera를 약 167억 달러에 인수한다고 발표하고 2015년 12월 30일에 인수를 완료했습니다.[41]

2020년 10월 27일 AMD는 자일링스를[42] 인수한다고 발표했고 2022년 2월 약 500억 달러에 달하는 인수를 완료했습니다.[43]

기타 제조업체는 다음과 같습니다.

- 1.5 GHz 패브릭[44] 속도의 SRAM 기반 FPGAS 제조용 Achronix

- Altium, 시스템 온 FPGA 하드웨어-소프트웨어 설계 환경을 제공합니다.[45]

- Efinix는 중소형 FPGA를 제공합니다. 이들은 로직 및 라우팅 인터커넥트를 구성 가능한 XLR 셀로 결합합니다.

- 고윈 반도체, 중소형 SRAM 및 플래시 기반 FPGA 제조. 또한 몇 가지 자일링스, 알테라 및 격자 제품에 대한 핀 호환 대체 기능도 제공합니다.

- 저전력 SRAM 기반의 FPGA를 제조하는 Latitude Semiconductor는 플래시, 인스턴트 온 및 라이브 재구성 기능을 통합적으로 제공합니다.

- 옵션으로 통합된 비휘발성 구성 메모리를 갖춘 초저전력 SRAM 기반의 FPGA를 제공하는 SiliconBlue Technologies, 2011년 Ratice에 인수

- 마이크로칩:

- 디스플레이 브리지 MIPI & RGB 입력, MIPI, RGB 및 LVDS 출력을 갖춘 초저전력 SRAM 기반 FPGA, 초저전력 센서 허브를 제조하는 [47]QuickLogic

적용들

FPGA는 계산 가능한 모든 문제를 해결하는 데 사용할 수 있습니다. 이것은 FPGA가 Xilinx MicroBlaze 또는 Altera Nios II와 같은 소프트 마이크로프로세서를 구현하는 데 사용될 수 있다는 사실에 의해 매우 입증되었습니다. 이들의 장점은 병렬 특성과 특정 프로세스에 사용되는 게이트 수 측면에서 최적성 때문에 일부 애플리케이션의 경우 훨씬 더 빠르다는 것입니다.[48]

FPGA는 원래 인쇄회로기판의 글루 로직을 구현하기 위해 CPLD의 경쟁업체로 시작되었습니다. FPGA는 크기, 기능 및 속도가 증가함에 따라 일부 기능이 현재 SoC(Full System on Chip)로 판매될 정도로 추가 기능을 이어받았습니다. 특히 1990년대 후반에 FPGA 아키텍처에 전용 곱셈기가 도입되면서 전통적으로 디지털 신호 프로세서 하드웨어(DSP)의 유일한 예비 영역이었던 애플리케이션이 대신 FPGA를 통합하기 시작했습니다.[49][50]

FPGA의 진화는 이러한 장치의 사용 증가에 동기를 부여했습니다. 이러한 장치의 아키텍처를 통해 3D MRI 영상 분할, 3D 이산 웨이블릿 변환, 단층 영상 재구성 또는 PET/MRI 시스템과 같은 복잡한 작업에 최적화된 하드웨어 솔루션을 개발할 수 있습니다.[51][52] 개발된 솔루션은 병렬 처리를 통해 집중적인 계산 작업을 수행할 수 있으며 동적으로 재프로그래밍이 가능하며 비용이 저렴하며 의료 영상과 관련된 까다로운 실시간 요구 사항을 모두 충족할 수 있습니다.

FPGA 사용의 또 다른 경향은 하드웨어 가속화입니다. FPGA를 사용하여 알고리즘의 특정 부분을 가속하고 FPGA와 일반 프로세서 간에 계산의 일부를 공유할 수 있습니다. 검색 엔진 빙(Bing)은 2014년 검색 알고리즘에 FPGA 가속을 채택한 것으로 유명합니다.[53] 2018년[update] 현재, FPGA는 마이크로소프트의 소위 "프로젝트 캐터펄트"[11]를 포함한 AI 가속기 및 기계 학습 애플리케이션을 위한 인공 신경망 가속기로 사용이 증가하고 있습니다.

전통적으로 [when?]FPGA는 생산량이 적은 특정 수직 응용 분야를 위해 예약되었습니다. 이러한 소량 애플리케이션의 경우, 기업이 프로그래밍 가능한 칩에 대해 단위당 하드웨어 비용으로 지불하는 프리미엄이 ASIC를 만드는 데 드는 개발 리소스보다 더 저렴합니다. 2017년[update] 현재, 새로운 비용 및 성능 역학은 실행 가능한 애플리케이션의 범위를 넓혔습니다.

개인용 컴퓨터 주변기기가 틈새 시장에 존재하거나 대량 시장 진출에 어려움을 겪고 있는 경우(때로는 과도한 프로모션에도 불구하고), 소규모 생산 실행(예: 1,000대)에 FPGA를 활용하는 것이 비용 효율적일 수 있습니다. 예를 들어 예를 들어 이국적인 제품이 있습니다. VHS 테이프 아카이브(일부 버전만 FPGA 기반)인 ArVid와 Xilinx FPGA를 사용한 기가바이트 테크놀로지의 i-RAM 버짓 유사 SSD 드라이브.[54] 종종 맞춤형 칩을 대량으로 만들면 더 저렴하지만, 제품을 빠르게 시장에 내놓기 위해 FPGA를 선택할 수도 있습니다. 다시 말하지만, 더 저렴한 FPGA의 가용성이 증가하고 있는 만큼, 더 큰 생산 실행에서도 FPGA를 포함하는 것이 정당화될 수 있습니다.

FPGA의 다른 용도는 다음과 같습니다.

- 공간(방사선 경화[55] 포함)

- 하드웨어 보안 모듈[56]

- 고빈도매매[57][58]

- Retro Computing(예: MARS 및 MiSTer FPGA 프로젝트)[citation needed]

보안.

FPGA는 하드웨어 보안과 관련하여 ASIC이나 보안 마이크로프로세서에 비해 장점과 단점을 모두 가지고 있습니다. FPGA의 유연성으로 인해 제작 중 악의적인 수정이 발생할 경우 위험이 줄어듭니다.[59] 이전에는 많은 FPGA의 경우 설계 비트스트림이 외부 메모리(일반적으로 모든 전원을 켤 때)에서 FPGA가 이를 로드하는 동안 노출되었습니다. 모든 주요 FPGA 공급업체는 이제 비트스트림 암호화 및 인증과 같은 설계자에게 다양한 보안 솔루션을 제공합니다. 예를 들어 Altera와 Xilinx는 외부 플래시 메모리에 저장된 비트 스트림에 대해 AES 암호화(최대 256비트)를 제공합니다. PUF(Physical Unclonable functions)는 처리로 인해 고유한 서명이 있는 집적 회로로, 하드웨어 공간을 거의 차지하지 않으면서 FPGA를 확보하는 데에도 사용할 수 있습니다.[60]

Microsemi의 ProAsic 3 또는 Ratith의 XP2 프로그램 가능 장치와 같이 구성을 비휘발성 플래시 메모리에 내부적으로 저장하는 FPGA는 비트스트림을 노출하지 않으며 암호화가 필요하지 않습니다. 또한 룩업 테이블용 플래시 메모리는 공간 애플리케이션에 대한 단일 이벤트 반전 보호 기능을 제공합니다.[clarification needed] 변조 저항성에 대한 더 높은 보증을 원하는 고객은 Microsemi와 같은 공급업체에서 제공하는 쓰기 방식의 안티퓨즈 FPGA를 사용할 수 있습니다.

Altera는 Stratix 10 FPGA와 SoC를 통해 보안 장치 관리자와 물리적 복제 불가능 기능을 도입하여 물리적 공격에 대한 높은 수준의 보호 기능을 제공했습니다.[61]

2012년 연구원 세르게이 스코로보가토프와 크리스토퍼 우즈는 일부 FPGA가 적대적 의도에 취약할 수 있음을 보여주었습니다. 그들은 암호화 키 및 액세스 키 재프로그래밍, 암호화되지 않은 비트스트림 액세스, 낮은 수준의 실리콘 기능 수정 및 구성 데이터 추출과 같은 여러 수준에서 취약하게 만드는 Actel/Microsemi ProAsic 3의 일부로 실리콘에서 중요한 백도어 취약성이 제조되었음을 발견했습니다.[62]

2020년에는 모든 Xilinx 7 시리즈 FPGA에서 중요한 취약점("Starbleed"라는 이름)이 발견되어 비트스트림 암호화를 무용지물로 만들었습니다. 해결책이 없습니다. Xilinx는 하드웨어 수정본을 생성하지 않았습니다. 당시 이미 시장에 나와 있던 울트라스케일 이상의 기기는 영향을 받지 않았습니다.

유사한 기술

역사적으로 FPGA는 고정 ASIC에 비해 느리고 에너지 효율이 낮으며 일반적으로 기능성이 떨어졌습니다. 2006년에 실시된 연구에 따르면 FPGA에 구현된 설계는 평균적으로 40배의 면적이 필요하고 12배의 동적 전력이 필요하며 해당 ASIC 구현 속도의 3분의 1 속도로 실행됩니다.[63] 보다 최근에는 Xilinx Virtex-7이나 Altera Stratix 5와 같은 FPGA가 전력 사용량을 크게 줄이고 속도를 높이며 재료 비용을 절감하며 구현을 최소화함으로써 ASIC 및 ASSP("Application-specific standard part, 독립형 USB 인터페이스 칩[64] 등) 솔루션과 경쟁하게 되었습니다. 그리고 '온더플라이'로 재구성할 가능성을 높였습니다. 6~10개의 ASIC을 포함했던 설계를 이제는 하나의 FPGA를 사용하여 달성할 수 있습니다.[63]

FPGA의 장점은 버그를 수정하기 위해 이미 배포되었을 때(즉, "현장"에서" 다시 프로그래밍할 수 있는 기능을 포함하며, 종종 시장 출시 시간 단축 및 반복되지 않는 엔지니어링 비용 절감을 포함합니다. 공급업체는 또한 FPGA 프로토타이핑을 통해 중간 도로를 선택할 수 있습니다. 즉, FPGA에서 프로토타이핑 하드웨어를 개발하지만 설계가 완료된 후에는 더 이상 수정할 수 없도록 최종 버전을 ASIC로 제조할 수 있습니다. 이는 새로운 프로세서 디자인의 경우에도 종종 해당됩니다.[65] 일부 FPGA에는 장치의 한 부분을 다시 프로그래밍하고 다른 부분을 계속 실행할 수 있는 부분 재구성 기능이 있습니다.[66][67]

복합 프로그래머블 로직 디바이스(CPLD)와 FPGA의 주요 차이점은 아키텍처입니다. CPLD는 비교적 적은 수의 클록킹된 레지스터를 공급하는 하나 이상의 프로그래밍 가능한 제품의 총 논리 어레이로 구성된 비교적 제한적인 구조를 갖습니다. 결과적으로 CPLD는 유연성이 떨어지지만 더 예측 가능한 타이밍 지연과 더 높은 논리 대 상호 연결 비율의 장점이 있습니다.[citation needed] 그러나 FPGA 아키텍처는 상호 연결에 의해 지배됩니다. 따라서 설계가 훨씬 유연해졌을 뿐만 아니라 설계하기에도 훨씬 더 복잡하거나 최소한 더 복잡한 전자 설계 자동화(EDA) 소프트웨어가 필요합니다. 실제로 FPGA와 CPLD의 구별은 보통 자원 측면에서 CPLD보다 훨씬 크기 때문에 종종 크기 중 하나입니다. 일반적으로 FPGA에만 가산기, 곱셈기, 메모리 및 직렬화기/직렬화기와 같은 더 복잡한 내장 기능이 포함되어 있습니다. 또 다른 공통적인 차이점은 CPLD에는 구성을 저장하기 위해 내장된 플래시 메모리가 포함되어 있는 반면 FPGA에는 일반적으로 외부 비휘발성 메모리가 필요하다는 것입니다(항상 그렇지는 않습니다). 설계에 간단한 인스턴트 온(전원을 켤 때 논리가 이미 구성되어 있음)이 필요한 경우 일반적으로 CPLD가 선호됩니다. 대부분의 다른 애플리케이션에서는 일반적으로 FPGA가 선호됩니다. 때로는 CPLD와 FPGA가 모두 단일 시스템 설계에 사용되기도 합니다. 이러한 설계에서 CPLD는 일반적으로 글루 로직 기능을 수행하고 완전한 회로 기판의 리셋 및 부트 시퀀스를 제어할 뿐만 아니라 FPGA를 "부팅"하는 역할을 합니다. 따라서 용도에 따라 단일 설계에서 FPGA와 CPLD를 모두 사용하는 것이 현명할 수 있습니다.[68]

참고 항목

참고문헌

- ^ a b c "FPGA Architecture for the Challenge". toronto.edu. University of Toronto.

- ^ Simpson, P. A. (2015). FPGA Design, Best Practices for Team Based Reuse, 2nd edition. Switzerland: Springer International Publishing AG. p. 16. ISBN 978-3-319-17924-7.

- ^ a b c d "History of FPGAs". Archived from the original on April 12, 2007. Retrieved 2013-07-11.

- ^ Ron Wilson (21 April 2015). "In the Beginning". altera.com. Archived from the original on 2015-04-21.

- ^ a b "XCELL issue 32" (PDF). Xilinx. Archived (PDF) from the original on 2011-01-07.

- ^ a b c d e f 펀딩 유니버스. "Xilinx, Inc." 2009년 1월 15일 검색.

- ^ Clive Maxfield, Programmable Logic DesignLine "Xilinx는 혁신적인 65nm FPGA 아키텍처를 공개합니다. Virtex-5 제품군 Archive the Wayback Machine 2009-12-25입니다. 2006년 5월 15일. 2009년 2월 5일 검색.

- ^ a b Maxfield, Clive (2004). The Design Warrior's Guide to FPGAs: Devices, Tools and Flows. Elsevier. p. 4. ISBN 978-0-7506-7604-5.

- ^ "Top FPGA Companies For 2013". sourcetech411.com. 2013-04-28.

- ^ "Microsoft Supercharges Bing Search With Programmable Chips". WIRED. 16 June 2014.

- ^ a b "Project Catapult". Microsoft Research. July 2018.

- ^ Maxfield, Max. "Xilinx UltraScale FPGA Offers 50 Million Equivalent ASIC Gates". www.eetimes.com. EE Times.

- ^ a b Dylan McGrath, EE Times "FPGA 시장, 10년까지 27억 달러 돌파, In-Stat Says" 2006년 5월 24일. 2009년 2월 5일 검색.

- ^ a b "Global FPGA Market Analysis And Segment Forecasts To 2020 – FPGA Industry, Outlook, Size, Application, Product, Share, Growth Prospects, Key Opportunities, Dynamics, Trends, Analysis, FPGA Report – Grand View Research Inc". grandviewresearch.com.

- ^ Dylan McGrath, EE Times "Gartner Dataquest Analyst, ASIC, FPGA Markets Clean Bill of Health" 2005년 6월 13일. 2009년 2월 5일 검색.

- ^ "Virtex-4 Family Overview" (PDF). xilinx.com. Archived (PDF) from the original on 2007-11-22. Retrieved 14 April 2018.

- ^ Wisniewski, Remigiusz (2009). Synthesis of compositional microprogram control units for programmable devices. Zielona Góra: University of Zielona Góra. p. 153. ISBN 978-83-7481-293-1.[영구적 데드링크]

- ^ Oklobdzija, Vojin G. (2017). Digital Design and Fabrication. CRC Press. ISBN 9780849386046.

- ^ "FPGA Signal Integrity tutorial". altium.com. Archived from the original on 2016-03-07. Retrieved 2010-06-15.

- ^ NASA: Wayback Machine에서 FPGA 드라이브 강도 아카이브 2010-12-05

- ^ Mike Thompson (2007-07-02). "Mixed-signal FPGAs provide GREEN POWER". Design & Reuse.

- ^ M.b, Swami; V.p, Pawar (2014-07-31). "VLSI DESIGN: A NEW APPROACH". Journal of Intelligence Systems. 4 (1): 60–63. ISSN 2229-7057.

- ^ 2. 사이클론II Architecture. 알테라. 2007년2월

- ^ "Documentation: Stratix IV Devices" (PDF). Altera.com. 2008-06-11. Archived from the original (PDF) on 2011-09-26. Retrieved 2013-05-01.

- ^ Virtex-4 FPGA 사용 설명서(2008년 12월 1일). 자일링스

- ^ "Xilinx Inc, Form 8-K, Current Report, Filing Date Oct 19, 2011". secdatabase.com. Retrieved May 6, 2018.

- ^ "Xilinx Inc, Form 10-K, Annual Report, Filing Date May 31, 2011". secdatabase.com. Retrieved May 6, 2018.

- ^ 타카하시 학장님, 벤처 비트. "인텔 커넥션은 칩 스타트업인 타불라가 1억800만 달러를 모으는 것을 도왔습니다." 2011년 5월 2일. 2011년 5월 13일 회수.

- ^ a b 로렌스 라티프, 더 인콰이어러. "FPGA 제조사는 무어의 법칙을 이겼다고 주장합니다." 2010년 10월 27일. 2011년 5월 12일 회수.

- ^ EDN 유럽. "Xilinx는 Wayback Machine에서 스택 다이 3D 패키징 Archive 2011-02-19를 채택하고 있습니다." 2010년 11월 1일. 2011년 5월 12일 회수.

- ^ Saban, Kirk (December 11, 2012). "Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity, Bandwidth, and Power Efficiency" (PDF). xilinx.com. Archived (PDF) from the original on 2010-11-05. Retrieved 2018-11-30.

- ^ "Intel Custom Foundry EMIB". Intel. Archived from the original on 2015-07-13. Retrieved 2015-07-13.

- ^ "Battle Over the FPGA: VHDL vs Verilog! Who is the True Champ?". digilentinc.com. Archived from the original on 2020-12-26. Retrieved 2020-12-16.

- ^ "Why use OpenCL on FPGAs?". StreamComputing. 2014-09-16. Archived from the original on 2017-01-01. Retrieved 2015-07-17.

- ^ a b "All about FPGAs".

- ^ Dillien, Paul (March 6, 2017). "And the Winner of Best FPGA of 2016 is..." EETimes. Archived from the original on January 5, 2019. Retrieved September 7, 2017.

- ^ "Xilinx ISE Design Suite". www.xilinx.com. Retrieved 2018-12-01.

- ^ "FPGA Design Software - Intel Quartus Prime". Intel. Retrieved 2018-12-01.

- ^ "Tabula's Time Machine — Micro Processor Report" (PDF). Archived from the original (PDF) on 2011-04-10.

- ^ 타불라, 문을 닫다; 팹리스 칩 회사 실리콘 밸리 비즈니스 저널에서 120개 일자리 감소

- ^ "Intel to buy Altera for $16.7 billion in its biggest deal ever". Reuters. June 2015.

- ^ "AMD to Acquire Xilinx, Creating the Industry's High Performance Computing Leader". October 2020.

- ^ "AMD closes record chip industry deal with estimated $50 billion purchase of Xilinx". Reuters. February 2022.

- ^ "Achronix to Use Intel's 22nm Manufacturing". Intel Newsroom. 2010-11-01. Retrieved 2018-12-01.

- ^ Maxfield, Clive (16 June 2004). The Design Warrior's Guide to FPGAs. Elsevier Science. ISBN 9780080477138.

- ^ "Top FPGA Companies For 2013". SourceTech411. 2013-04-28. Retrieved 2018-12-01.

- ^ "QuickLogic — Customizable Semiconductor Solutions for Mobile Devices". www.quicklogic.com. QuickLogic Corporation. Retrieved 2018-10-07.

- ^ "Xilinx Inc, Form 8-K, Current Report, Filing Date Apr 26, 2006". secdatabase.com. Retrieved May 6, 2018.

- ^ "Publications and Presentations". bdti.com. Archived from the original on 2010-08-21. Retrieved 2018-11-02.

- ^ LaPedus, Mark. "Xilinx aims 65-nm FPGAs at DSP applications". EETimes.

- ^ Alcaín, Eduardo; Fernández, Pedro R.; Nieto, Rubén; Montemayor, Antonio S.; Vilas, Jaime; Galiana-Bordera, Adrian; Martinez-Girones, Pedro Miguel; Prieto-de-la-Lastra, Carmen; Rodriguez-Vila, Borja; Bonet, Marina; Rodriguez-Sanchez, Cristina (2021-12-15). "Hardware Architectures for Real-Time Medical Imaging". Electronics. 10 (24): 3118. doi:10.3390/electronics10243118. ISSN 2079-9292.

- ^ Nagornov, Nikolay N.; Lyakhov, Pavel A.; Valueva, Maria V.; Bergerman, Maxim V. (2022). "RNS-Based FPGA Accelerators for High-Quality 3D Medical Image Wavelet Processing Using Scaled Filter Coefficients". IEEE Access. 10: 19215–19231. doi:10.1109/ACCESS.2022.3151361. ISSN 2169-3536. S2CID 246895876.

- ^ Morgan, Timothy Pricket (2014-09-03). "How Microsoft Is Using FPGAs To Speed Up Bing Search". Enterprise Tech. Retrieved 2018-09-18.

- ^ "Gigabyte's i-RAM: Affordable Solid State Storage". anandtech.com. 2005-07-25. Retrieved 2020-12-16.

- ^ "FPGA development devices for radiation-hardened space applications introduced by Microsemi". www.militaryaerospace.com. 2016-06-03. Retrieved 2018-11-02.

- ^ "CrypTech: Building Transparency into Cryptography t" (PDF). Archived (PDF) from the original on 2016-08-07.

- ^ Mann, Tobias (2023-03-08). "While Intel XPUs are delayed, here's some more FPGAs to tide you over". The Register.

- ^ Leber, Christian; Geib, Benjamin; Litz, Heiner (September 2011). High Frequency Trading Acceleration Using FPGAs. International Conference on Field Programmable Logic and Applications. IEEE. doi:10.1109/FPL.2011.64.

- ^ Huffmire, Ted; Brotherton, Brett; Sherwood, Timothy; Kastner, Ryan; Levin, Timothy; Nguyen, Thuy D.; Irvine, Cynthia (2008). "Managing Security in FPGA-Based Embedded Systems". IEEE Design & Test of Computers. 25 (6): 590–598. doi:10.1109/MDT.2008.166. S2CID 115840.

- ^ Babaei, Armin; Schiele, Gregor; Zohner, Michael (2022-07-26). "Reconfigurable Security Architecture (RESA) Based on PUF for FPGA-Based IoT Devices". Sensors. 22 (15): 5577. Bibcode:2022Senso..22.5577B. doi:10.3390/s22155577. ISSN 1424-8220. PMC 9331300. PMID 35898079.

- ^ "EETimes on PUF: Security features for non-security experts – Intrinsic ID". Intrinsic ID. 2015-06-09. Archived from the original on 2015-07-13. Retrieved 2015-07-12.

- ^ Skorobogatov, Sergei; Woods, Christopher (2012). "Breakthrough Silicon Scanning Discovers Backdoor in Military Chip". Cryptographic Hardware and Embedded Systems – CHES 2012. Lecture Notes in Computer Science. Vol. 7428. pp. 23–40. doi:10.1007/978-3-642-33027-8_2. ISBN 978-3-642-33026-1.

- ^ a b Kuon, Ian; Rose, Jonathan (2006). "Measuring the gap between FPGAs and ASICs" (PDF). Proceedings of the international symposium on Field programmable gate arrays – FPGA'06. New York, NY: ACM. pp. 21–30. doi:10.1145/1117201.1117205. ISBN 1-59593-292-5. Archived from the original (PDF) on 2010-06-22. Retrieved 2017-10-25.

- ^ "ASIC, ASSP, SoC, FPGA – What's the Difference?". eetimes.com.

- ^ Cutress, Ian (August 27, 2019). "Xilinx Announces World Largest FPGA: Virtex Ultrascale+ VU19P with 9m Cells". AnandTech.

- ^ "AN 818: Static Update Partial Reconfiguration Tutorial: for Intel Stratix 10 GX FPGA Development Board". www.intel.com. Retrieved 2018-12-01.

- ^ "Can FPGAs dynamically modify their logic?". Electrical Engineering Stack Exchange. Retrieved 2018-12-01.

- ^ "CPLD vs FPGA: Differences between them and which one to use? – Numato Lab Help Center". numato.com. 2017-11-29.

더보기

- Sadrozinski, Hartmut F.-W.; Wu, Jinyuan (2010). Applications of Field-Programmable Gate Arrays in Scientific Research. Taylor & Francis. ISBN 978-1-4398-4133-4.

- Wirth, Niklaus (1995). Digital Circuit Design An Introduction Textbook. Springer. ISBN 978-3-540-58577-0.

- Mitra, Jubin (2018). "An FPGA-Based Phase Measurement System". IEEE Transactions on Very Large Scale Integration (VLSI) Systems. IEEE. 26: 133–142. doi:10.1109/TVLSI.2017.2758807. S2CID 4920719.

- 멘서, 오스카 등 (2020). "FPGAs의 역사, 현황, 미래" ACM의 통신. ACM. Vol. 63, No. 10. doi:10.1145/3410669